HT66FV1x0 Integrated Audio Amplifier Application Guideline

AN0486EN V1.10 8 / 16 June 8, 2021

The audio amplifier power pin AVDD_PA should be wired directly to the positive power supply

and the line width should not be less than 12mil.

To avoid noise interference caused by instantaneous large currents during audio amplifier

operations, two separate grounds are required, VSS for digital ground and AVSS_PA for analog

ground.

The audio amplifier ground pin AVSS_PA should be wired directly to the negative power

supply and the line width should not be less than 12mil.

The VSS and AVSS_PA are two separate grounds and should be implemented with copper

layers.

Ensure that enough space is reserved for the power and ground lines when placing components.

The power amplifier outputs, SP+/SP-, tracks should be thick and free of through holes.

As right angles tend to accumulate charge resulting in point discharge effects, which can

influence the PCB stability, it is better to route tracks using 45-degree angles or arc angles.

Software Description

Voice Playing Controller Setup

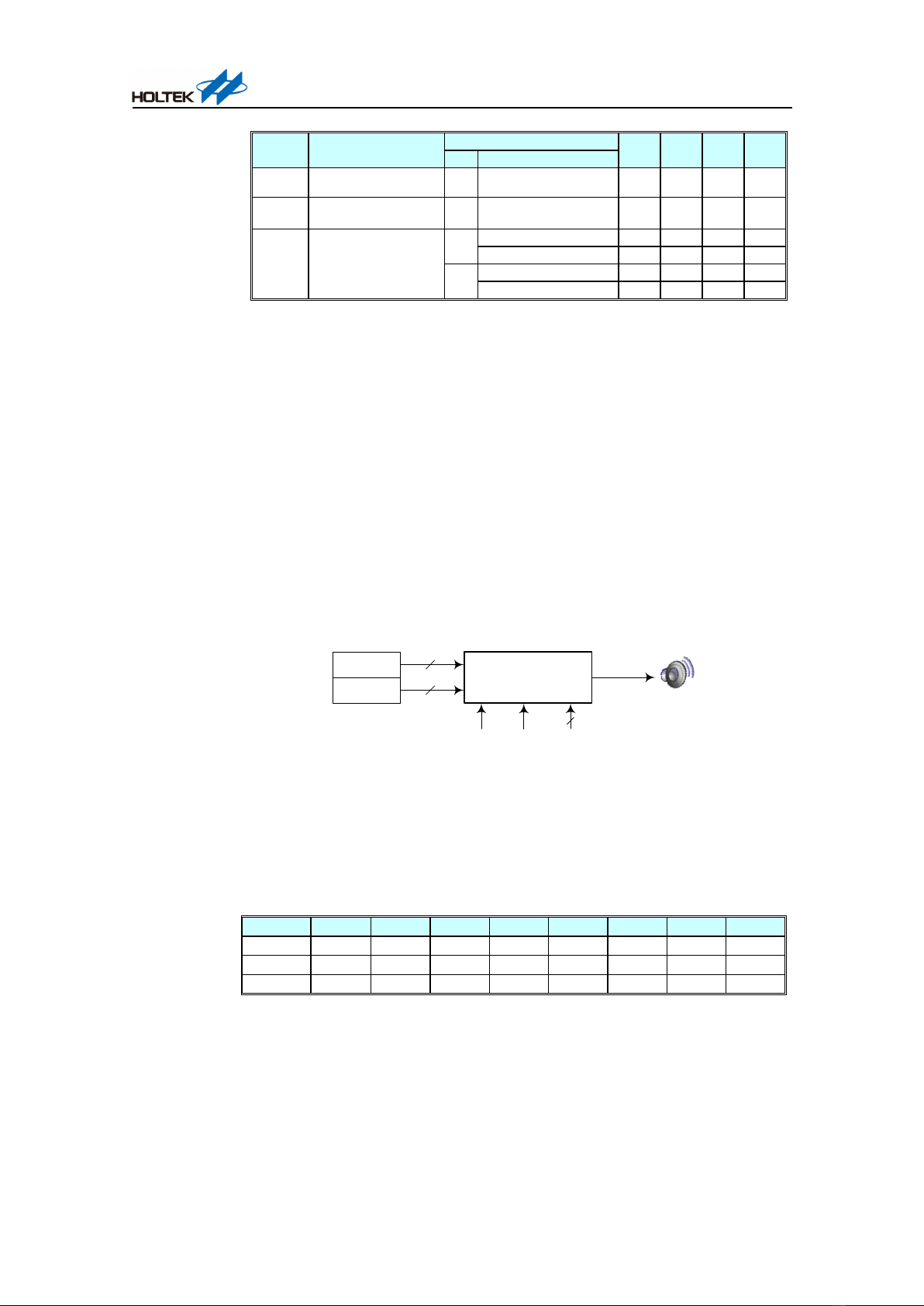

The HT66FV1x0 controls the voice playing function using several registers, as described below.

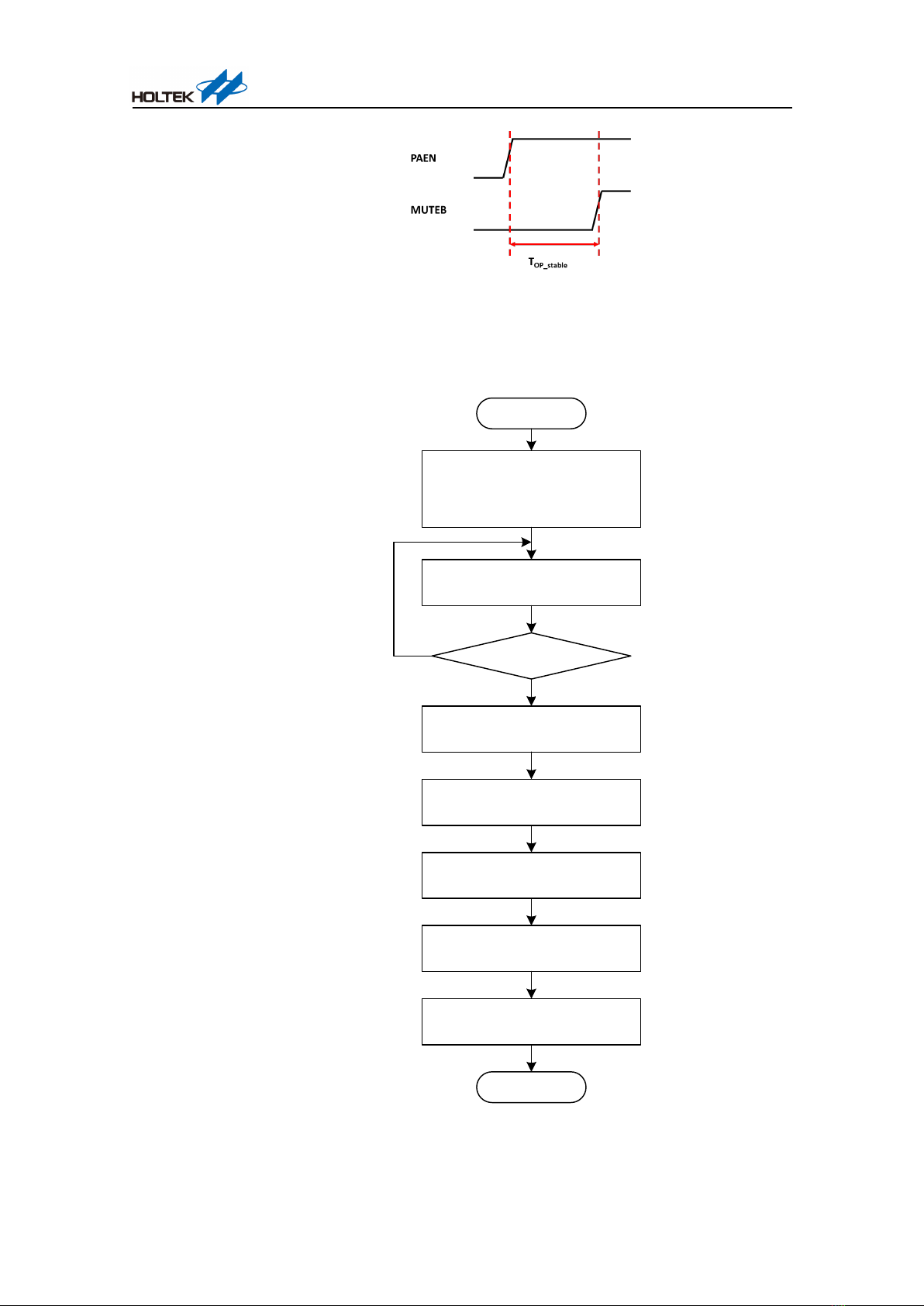

1. When the PAEN (PLAC.1) bit is set high, the power amplifier is enabled. When the DAEN

(PLAC.0) bit is set high, the 16-bit D/A converter is enabled.

2. When the MUTEB (USVC.7) bit is set high, the speaker is enabled.

3. There are two methods for volume control.

Analog volume control: Externally connect a variable resistor between the DAC output pin,

AUD, and the power amplifier analog input pin, AUD_IN. The DAC output signal is first

attenuated via the resistor divider and then input to the power amplifier. This method is

suitable for applications which use a rotary knob to adjust volume.

Digital volume control: Use the USVC6~USVC0 software bits to control the speaker

volume. This can be used to adjust the speaker volume within a range of +6dB to -32dB.

Each stage is 0.5dB for high volume applications or 1dB for low volume applications.

4. Voice data is stored in the external SPI Flash ROM. The MCU reads voice data from the SPI

Flash using its integrated SPI interface.

5. Each 16-bit section of voice data is placed in the PLADL and PLADH registers. Use a timer to

generate interrupt signals at regular intervals, read the voice data from the SPI Flash each time

an interrupt is generated and write it into the 16-bit DAC. After this the analog signal amplified

by the integrated power amplifier will be output to drive the speaker to produce sound.