INTEL OEM PRODUCTS AND SERVICES DIVISION PRELIMINARY - REV 0.1

Classic/PCI i486 Baby-AT Motherboard Technical Product Summary

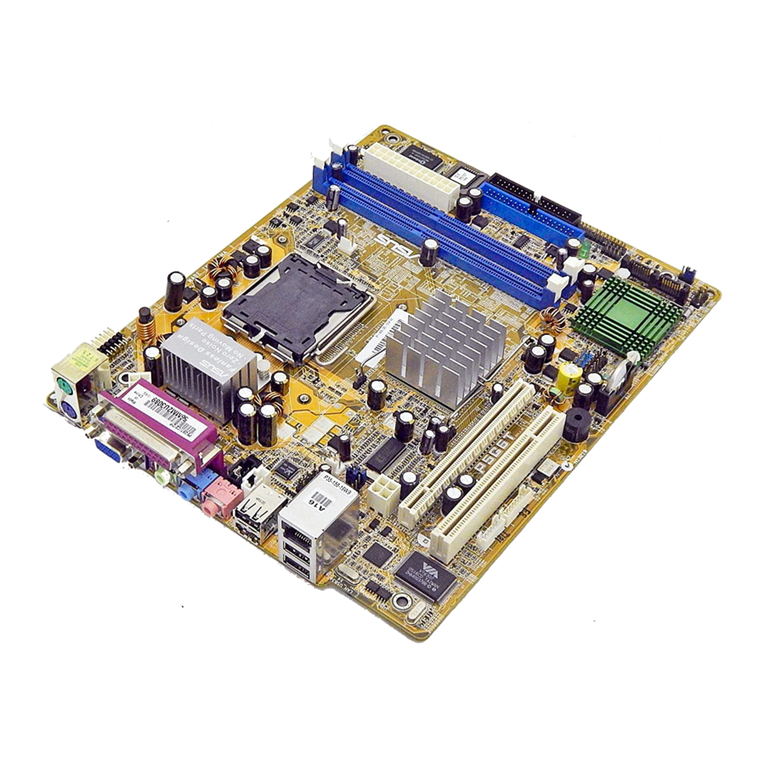

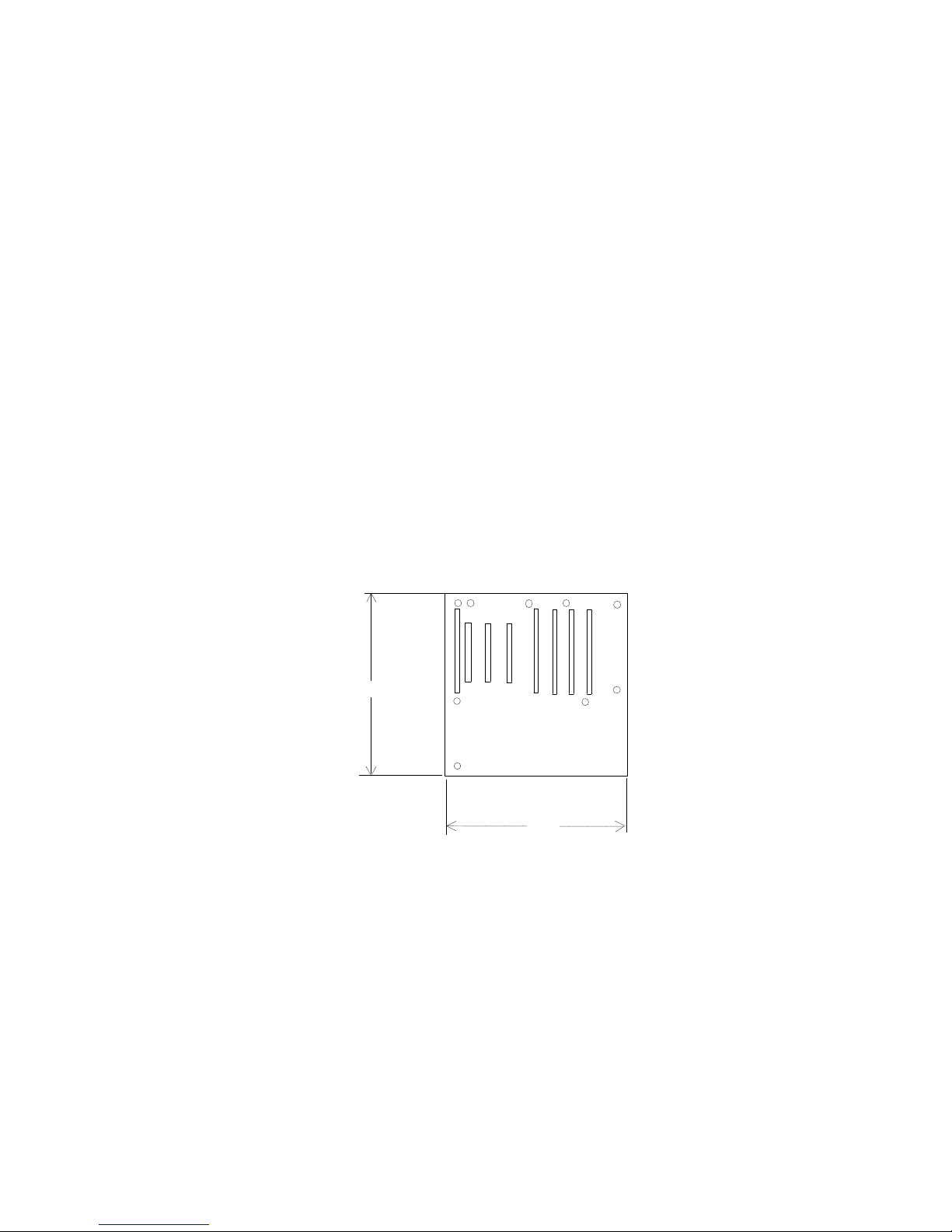

Classic/PCI i486 Baby-AT Motherboard

Preliminary Technical Product Summary

Revision 0.1

Table of Contents

Introduction.........................................................................................................................................4

Baby-AT Form Factor...................................................................................................................4

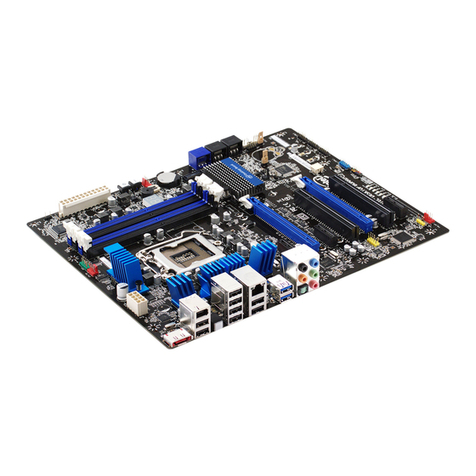

Board Level Features..........................................................................................................................5

CPU..............................................................................................................................................5

Performance Upgrade ...................................................................................................................5

Second Level Cache......................................................................................................................5

System BIOS ................................................................................................................................5

PCI Auto-configuration Capability........................................................................................................ 5

Setup Utility......................................................................................................................................... 6

FLASH Implementation........................................................................................................................ 6

Upgrade Utility.....................................................................................................................................6

Flash User Area.................................................................................................................................... 7

Keyboard (and Mouse) Interface ...................................................................................................7

System Memory............................................................................................................................7

Core Chip Set ...............................................................................................................................7

82424TX Cache/DRAM/Controller (CDC) ...........................................................................................8

82423TX Data Path Unit (DPU)...........................................................................................................8

82378IB System I/O (SIO)....................................................................................................................8

Expansion Slots............................................................................................................................8

SMC 37C663 Super I/O Controller...............................................................................................8

Dallas DS12887 Real Time Clock, CMOS RAM and Battery........................................................8

Front Panel Connectors.................................................................................................................8

Security ........................................................................................................................................9

BIOS Password.....................................................................................................................................9

Setup Enable Jumper............................................................................................................................9

System Integration Features................................................................................................................10

Back panel Connections................................................................................................................10

Power Supply................................................................................................................................10

Appendices ..........................................................................................................................................11

Appendix A −User-Installable Upgrades......................................................................................11

System Memory.................................................................................................................................... 11

Performance Upgrade ...........................................................................................................................12

Qualified DRAM SIMMs .....................................................................................................................12

Appendix B −Jumpers..................................................................................................................13

Appendix C −BIOS Setup Options...............................................................................................14

Appendix D −BIOS Recovery ......................................................................................................15

Using the Upgrade Utility..................................................................................................................... 15

Recovery Mode.....................................................................................................................................15

Appendix E −Memory Map..........................................................................................................16

Appendix F −I/O Map..................................................................................................................17

Appendix G −Board Interrupts & DMA.......................................................................................18

Appendix H −Connectors.............................................................................................................19

AT Style Keyboard Port (J8L1 = Keyboard)..........................................................................................19

Optional PS/2 Style Keyboard, Mouse Ports (J8L2 = Keyboard, J9L1 = Mouse).................................... 19

Turbo LED Connector (J1A1)...............................................................................................................19

Hard Drive LED Connector (J1A2).......................................................................................................19

Key lock/Power LED Connector (J1B1)................................................................................................19

Speaker Connector (J1C1).................................................................................................................... 19

Turbo Switch Connector (J1C1B) .........................................................................................................19

Primary Power Connector (J9K1)..........................................................................................................20

Auxiliary (3.3V) Power Connector (J4H1)............................................................................................20

Parallel Port (J7J1)...............................................................................................................................20

Serial Ports (J7L2 = COM1, J7L1 = COM2)......................................................................................... 20

Reset Connector (J1B2)........................................................................................................................20