Interface Masters TAHOE 8724 User manual

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 1 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

User Guide

TAHOE 8724

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 2 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

TABLE OF CONTENTS

1 INTRODUCTION ............................................................................................................... 6

1.1 STANDARD FEATURES................................................................................................ 6

1.2 FUNCTIONAL DIAGRAM................................................................................................... 7

1.3 PHYSICAL LAYOUT FOR SYSTEM....................................................................................... 9

2 MAJOR COMPONENTS............................................................................................... 12

2.1 CN78XX PROCESSOR.............................................................................................. 12

2.1.1 CN78XX Processor Overview ........................................................................... 12

2.1.2 DDR (LMC)....................................................................................................... 13

2.1.3 SPI ..................................................................................................................... 14

2.1.4 eMMC/SD.......................................................................................................... 15

2.1.5 Boot Bus............................................................................................................. 16

2.1.6 SERDES (QLMs)............................................................................................... 17

2.1.7 I2C (TWSI)......................................................................................................... 18

2.1.8 UART................................................................................................................. 19

2.1.9 USB 3.0.............................................................................................................. 20

2.1.10 MDIO (SMI)................................................................................................... 21

2.1.11 MANAGEMENT PORT ................................................................................................ 22

2.2 CPLD .................................................................................................................... 24

2.2.1 CPLD Overview ............................................................................................... 24

2.2.2 Power Sequencing Control................................................................................ 25

2.2.3 Access Interface................................................................................................. 25

2.2.4 LED Control...................................................................................................... 26

2.2.5 Boot Devices...................................................................................................... 27

2.3.5 Selecting Boot Device........................................................................................ 27

2.4 CS4318 –QUAD RXAUI TO SFI PHY..................................................................... 28

2.5 VSC8221 –SINGLE PORT SGMII TO 1GBASE-T PHY ............................................ 29

2.6 PEX8724 –PCI-E GEN3SWITCH............................................................................ 30

2.7 PCI-E M.2 SSD...................................................................................................... 31

2.8 SERIAL INTERFACE .................................................................................................. 31

3 I2C PERIPHERALS...................................................................................................... 32

3.1 I2C BUS 0PERIPHERALS............................................................................................... 32

3.1.1 DDR4 SPD......................................................................................................... 32

3.2 I2C BUS 1PERIPHERALS ......................................................................................... 33

3.2.2 ADM1032ARZ - Temperature Sensor ............................................................... 33

3.2.3 MCP7940N - Real Time Clock.......................................................................... 33

3.2.4 EEPROM........................................................................................................... 33

4 I/O MODULES.............................................................................................................. 34

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 3 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

4.1 TM13233 I/O MODULE .......................................................................................... 34

4.2 TM13238 I/O MODULE................................................................................................ 35

5 POWER SUPPLY.............................................................................................................. 36

5.1 POWER CONSUMPTION............................................................................................ 36

6 COOLING FAN............................................................................................................. 37

7 ENCLOSURE................................................................................................................ 38

7.1 ENCLOSURE DIMENSION.......................................................................................... 38

7.2 MOUNTING EARS..................................................................................................... 38

7.3 SLIDING GUIDES ..................................................................................................... 39

8 CUSTOMER SUPPORT ............................................................................................... 40

8.1 TECHNICAL ASSISTANCE .......................................................................................... 40

8.2 LIFE SUPPORT POLICY ............................................................................................ 40

8.3 WARRANTY.............................................................................................................. 41

9 ORDERING PART NUMBER....................................................................................... 42

9.1 SYSTEM ORDERING PART NUMBER.................................................................................. 42

9.2 STANDARD CONFIGURATIONS........................................................................................ 43

9.3 MODULE PART NUMBERS......................................................................................... 44

9.4 ACCESSORIES PART NUMBERS.................................................................................. 44

9.5 TRANSCEIVERS ........................................................................................................ 45

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 4 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

TABLE OF FIGURES

Figure 1, TAHOE 8724 Block Diagram................................................................................ 8

Figure 2, 3D Image of TAHOE 8724 with Top view............................................................. 9

Figure 3, 3D Image of TAHOE 8724 with Front View........................................................ 10

Figure 4, 3D Image of TAHOE 8724 with Rear View......................................................... 10

Figure 5, 3D Image of TAHOE 8724 with cover off............................................................ 11

Figure6, DDR(LMC) Block Diagram.................................................................................. 13

Figure 7, SPI Block Diagram.............................................................................................. 14

Figure 8, eMMC Block Diagram......................................................................................... 15

Figure 9, Boot Bus Interface................................................................................................ 16

Figure 10, I2C TWSI Block Diagram.................................................................................. 18

Figure 11, UART Signals to RJ45 ....................................................................................... 19

Figure 12, USB 3.0 Type- A Block Diagram....................................................................... 20

Figure 13, MDIO(SMI) Block Diagram .............................................................................. 21

Figure 14, Management Port............................................................................................... 22

Figure 15, Console Port ...................................................................................................... 23

Figure 16, TAHOE 8724 CPLD Functional Diagram ........................................................ 24

Figure 17, LED Control....................................................................................................... 26

Figure 18, CS4318 RXAUI TO SFI PHY Block Diagram ................................................... 28

Figure 19, Single Port SGMII to 10/100GBASE-T PHY Diagram...................................... 29

Figure 20, PCI-e Gen3 Switch Diagram............................................................................. 30

Figure 21, I2C Peripherals Diagram.................................................................................. 32

Figure 22, TM13233 I/O Module Block Diagram............................................................... 34

Figure 23, TM13238 I/O Module Block Diagram............................................................... 35

Figure 24, Cooling Fan Functional Diagram..................................................................... 37

Figure 25, Mounting Ears of TAHOE 8724 ........................................................................ 38

Figure 26, Sliding Guides of TAHOE 8724......................................................................... 39

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 5 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

TABLE OF Tables

Table 1, Console Port Setting…………………………………………………………………….. 23

Table 2, Boot Device Register……………………………………………………………………. 27

Table 3, Boot Device Bits…………………………………………………………………………. 27

Table 4, Input Power Supply……………………………………………………………………… 36

Table 5, Output Power Supply……………………………………………………………………. 36

Table 6, Dimension of Enclosure………………………………………………………………… 38

Table 7, Ordering Part Numbers………………………………………………………………… 42

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 6 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

1 Introduction

The TAHOE 8724, a highly flexible 1U networking appliance designed for

enterprise Market. TAHOE 8724 is based on Cavium 64-bit MIPS technology.

1.1 Standard Features

TAHOE 8724 is 1U appliance based on the Cavium CN78xx processor.

It provides the following external interfaces:

❖Four 1G/10G SFP+ ports

❖One 10/100/1000 BASE-T RJ45 management port

❖One RJ45 console port

❖One USB 3.0 Host port

❖One SD card slot

❖Two hot-swap power supply bays for redundancy

❖Two hot-swap I/O module bays supporting 8x 1G/10G SFP+ ports or 2x 40G

QSFP ports

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 7 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

Internally, the system provides:

➢Four DDR4 SODIMM sockets

➢eMMC flash (4GB)

➢Two M.2 PCI-e SSD (1TB)

➢SPI flash

➢An I2C TPM module for system authentication

➢An I2C RTC module for time keeping

➢An I2C EEPROM for parameter storage

➢I2C temperature sensors for board and CPU junction

➢A fan control module supporting up to 4 hot-pluggable dual-stack fans, each

speed-controllable via two I2C-connected ADT7470 fan controllers.

1.2 Functional Diagram

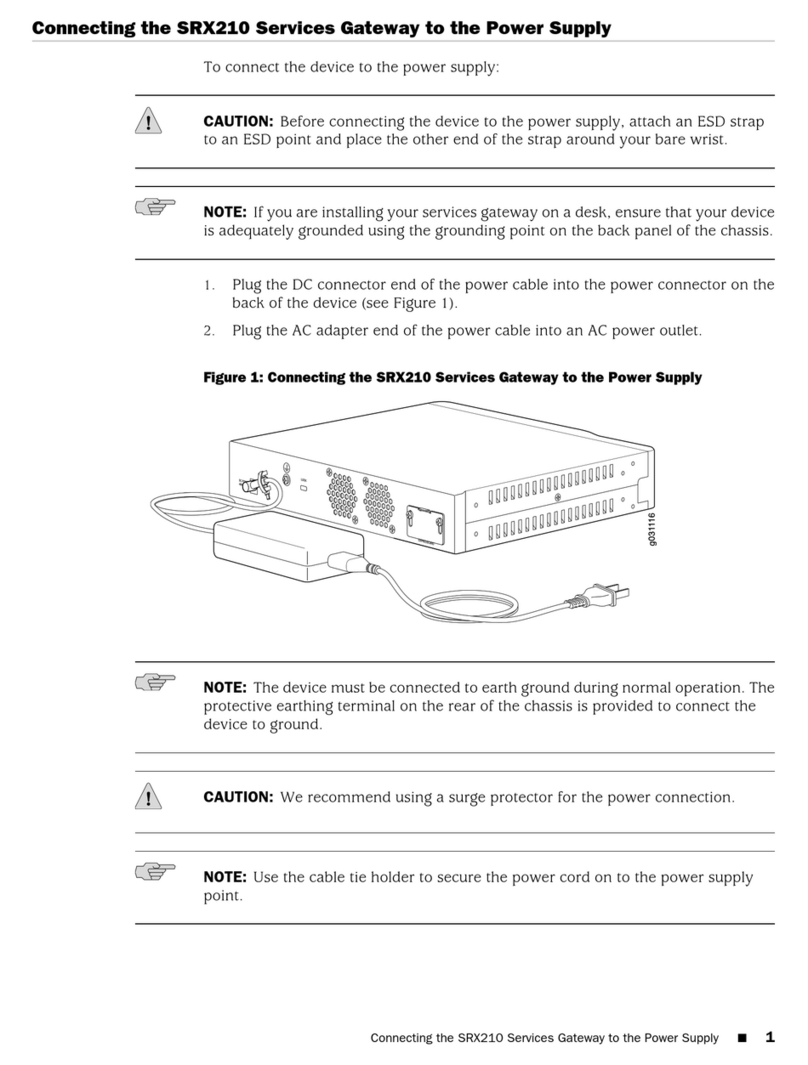

The below block diagram is for TAHOE 8724 Board.

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 8 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

Figure 1, TAHOE 8724 Block Diagram

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 9 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

1.3 Physical Layout for System

Figure 2, 3D Image of TAHOE 8724 with Top view

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 10 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

Figure 3, 3D Image of TAHOE 8724 with Front View

Figure 4, 3D Image of TAHOE 8724 with Rear View

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 11 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

Figure 5, 3D Image of TAHOE 8724 with cover off

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 12 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

2Major Components

2.1 CN78XX Processor

2.1.1 CN78XX Processor Overview

The Cavium OCTEON III CN78XX Multicore MIPS processor is the main

processor used in this system. The CN78XX has Four 72-bit DRAM controllers and

support DDR4 SPD. It includes Eight groups of four SERDES configured for various

Ethernet interfaces or PCI-e 3.0.

The following interfaces are provided by this part:

•Boot bus

•Four x SMI/MDIO bus

•Two x TWSI bus

•Two x UART

•SPI

•eMMC/SD

•USB 3.0 Host

•Eight QLMs SerDes block with four lanes each

•Four 72b DDR4 interface

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 13 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

2.1.2 DDR (LMC)

The CN78XX consists four 72-bit DRAM interfaces with ECC. It can

support DDR4 (up to 2133MHz data rate) and up to 512GB of memory (128GB per

controller).

All controllers obtain equal amount of attached DRAM.

Each controller has four ranks / chips selects and the following configuration are:

➢Up to two dual-rank DIMMs per controller

Figure6, DDR(LMC) Block Diagram

The TAHOE 8724 consist four DRAM interfaces with one DDR4 SODIMM slot

(up to 16GB) per interface.

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 14 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

2.1.3 SPI

Serial Peripheral Interface (SPI) has separate clock and data lines, along with a

select line and chip select. TAHOE 8724 have a SPI Interface connected to SPI Flash

memory.

Figure 7, SPI Block Diagram

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 15 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

2.1.4 eMMC/SD

The CN78XX consist one Embedded Multi-Media Controller (eMMC) interface

that can support up to two flash memory devices- eMMC Interface and SD card.

It supports the transfer rates up to 52MHz and have one, four and eight-bit Data

Bus. The TAHOE 8724 has an eMMC flash memory and SD card connected to eMMC

Interface, eMMC flash is connected to CMDO by default however user can switch

connection CMDO to SD card through the cross switch via CPLD.

Figure 8, eMMC Block Diagram

The eMMC interface also connects to Secure Digital(SD) card connector on the

front panel and could be configured as boot device.

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 16 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

2.1.5 Boot Bus

The CN78XX has general-purpose bus that typically attaches to nonvolatile

memory such as FLASH. It includes eight chip-selects, and 32 address/data lines.

The TAHOE 8724 has the CPLD connected on the Boot Bus interface as well as

this bus will be the main communication path to the CPLD.

Figure 9, Boot Bus Interface

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 17 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

2.1.6 SERDES (QLMs)

The CN78XX has eight Quad Lane Modules (QLM), with each consisting of Four

SERDES that can be configured as different interfaces, such as SGMII, XAUI, RXAUI,

XFI/KR, XLAUI, or PCI-e.

The TAHOE 8724 QLMs are configured as follows:

a) QLM0 –PCI-e 3.0 x4

b) QLM1 –SGMII x1

c) QLM2 –RXAUI x2

d) QLM3 –RXAUI x2

e) QLM4 –XFI/KR x4 or XLAUI x1

f) QLM5 –XFI/KR x4 or XLAUI x1

g) QLM6 –XFI/KR x4 or XLAUI x1

h) QLM7 –XFI/KR x4 or XLAUI x1

a. QLM0 is configured as PIC-e 3.0 RC interface to connect with PEX8724 PCI-e

switch.

b. QLM1 is configured as SGMII interface to connect with a GE PHY VSC8221 to

provide the management port.

c. QLM2/3 is configured as RXAUI interface to connect with CS4318 Quad RAXUI

to SFI PHY to provide four SFP+ ports.

d. QLM4/5/6/7 is configured as XFI or XLAUI interface to connect with the PHY on

the IO module.

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 18 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

2.1.7 I2C (TWSI)

The CN78XX comes with two I2C interfaces. It supports both standard mode

(100kbps) and fast mode (400kbps).

On the TAHOE8724, TWSI0 is connected to the DDR4 modules (SPD), and

TWSI1 is connected to RTC, temperature sensor, and an EEPROM to store configuration

data and MAC address.

TWSI0 I2C interface utilized by CPU to access I2C devices on board. The I2C

devices can be accessed through this interface are DDR3 SPD EEPROM, TLV EEPROM,

RTC controller and Temperature Sensor.

Figure 10, I2C TWSI Block Diagram

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 19 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

2.1.8 UART

The CN78XX comes with two UART interfaces. CN78XX transfers data to and

receive characters from the UART core via 64-bit CSR processor. The UART core

transfers data either by polling or interrupts.

The TAHOE 8724 utilizes UART0 as console port on the front panel. UART1 is

not used.

Figure 11, UART Signals to RJ45

TAHOE 8724 User Guide

Rev: 01

8/10/2017

Page 20 OF 45

Interface Masters Technologies Inc. Confidential & Proprietary

2.1.9 USB 3.0

The CN78XX utilizes USB 3.0 interface that supports Super Speed (5.0Gbps),

High-Speed (480Mbps), Full-Speed (12Mbps), and Low-Speed (1.5Mbps) transmission

rates.

The super speed transaction initiated by the host making a request followed by a

response from the device. In the TAHOE 8724, USB port is utilized as USB3.0 type A port

on the front panel.

Figure 12, USB 3.0 Type- A Block Diagram

Table of contents

Popular Gateway manuals by other brands

Agilent Technologies

Agilent Technologies E5810B user guide

Versa Networks

Versa Networks CSG-W1 user manual

RTA

RTA 460ESMS-N700 Product user guide

Juniper

Juniper SRX 210 instructions

ABB

ABB 83342-500 operating instructions

Planet Networking & Communication

Planet Networking & Communication MH-5000 Quick installation guide