TABLE OF CONTENTS

PREFACE .....................................................................................................................................1

About This Manual.....................................................................................................................1

Manual Contents ....................................................................................................................................1

CHAPTER 1..................................................................................................................................2

Introduction ................................................................................................................................2

Features .................................................................................................................................................2

CHAPTER 2..................................................................................................................................5

ADC - DAC Interface .................................................................................................................5

2.1 ANALOG INPUT...............................................................................................................................5

2.2 Analog Input Connector:...................................................................................................................6

2.3 ANALOG OUTPUT...........................................................................................................................8

2.4 Analog Output Connector:................................................................................................................9

2.6 Stereo Jack Connector:....................................................................................................................9

2.7 Function Generator ........................................................................................................................10

2.8 Potentiometer Adjustments ............................................................................................................10

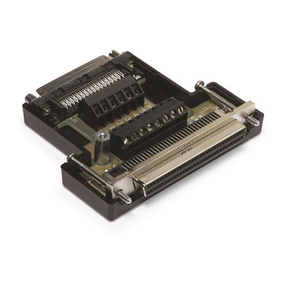

2.9 Jumper Settings of ADC- DAC Interface........................................................................................11

CHAPTER 3................................................................................................................................13

USB Interface ..........................................................................................................................13

3.1 Data Bus Connection .....................................................................................................................14

3.2 Control Lines: .................................................................................................................................14

3.3. FTDI Driver Installation..................................................................................................................15

CHAPTER 4................................................................................................................................17

Serial Interface.........................................................................................................................17

4.1 RS- 232 Interface ...........................................................................................................................17

CHAPTER 5................................................................................................................................19

PS/2 Mouse/Keyboard Interface..............................................................................................19

5.1 PS/2 KEYBOARD...........................................................................................................................20

5.2 Control Signal Connection..............................................................................................................21

CHAPTER 6................................................................................................................................23

VGA Interface ..........................................................................................................................23

6.1 VGA Display Theory.......................................................................................................................24

6.2 VGA signal TIMING........................................................................................................................26

CHAPTER 7................................................................................................................................27

Seven Segment LED Display ..................................................................................................27

CHAPTER 8................................................................................................................................29

Stepper Motor And Relay Interface .........................................................................................29

8.1 Stepper Motor Interface..................................................................................................................29

8.2 Relay Interface ...............................................................................................................................29

CHAPTER 9................................................................................................................................31

LCD Interface...........................................................................................................................31

9.1 Data Lines Connection ...................................................................................................................32

9.2 Control Line Interface: ....................................................................................................................32