NI PXIe-7865 User manual

PXIe-7865

Features

2023-03-31

Contents

NI PXIe-7865 User Manual. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Hardware Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Pinout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Connecting the NI PXIe-7865. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Analog Input. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Analog Output. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Digital I/O. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Field Wiring Considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

+5 V Power Source. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

NI Services. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

ni.com

2

PXIe-7865 Features

NI PXIe-7865 User Manual

This document provides compliance, pinout, connectivity, mounting, and power

information for the NI PXIe-7865.

© 2020National Instruments Corporation. All rights reserved. Refer to the <National

Instruments>\_Legal Information directory for information about NI copyright,

patents, trademarks, warranties, product warnings, and export compliance.

Hardware Overview

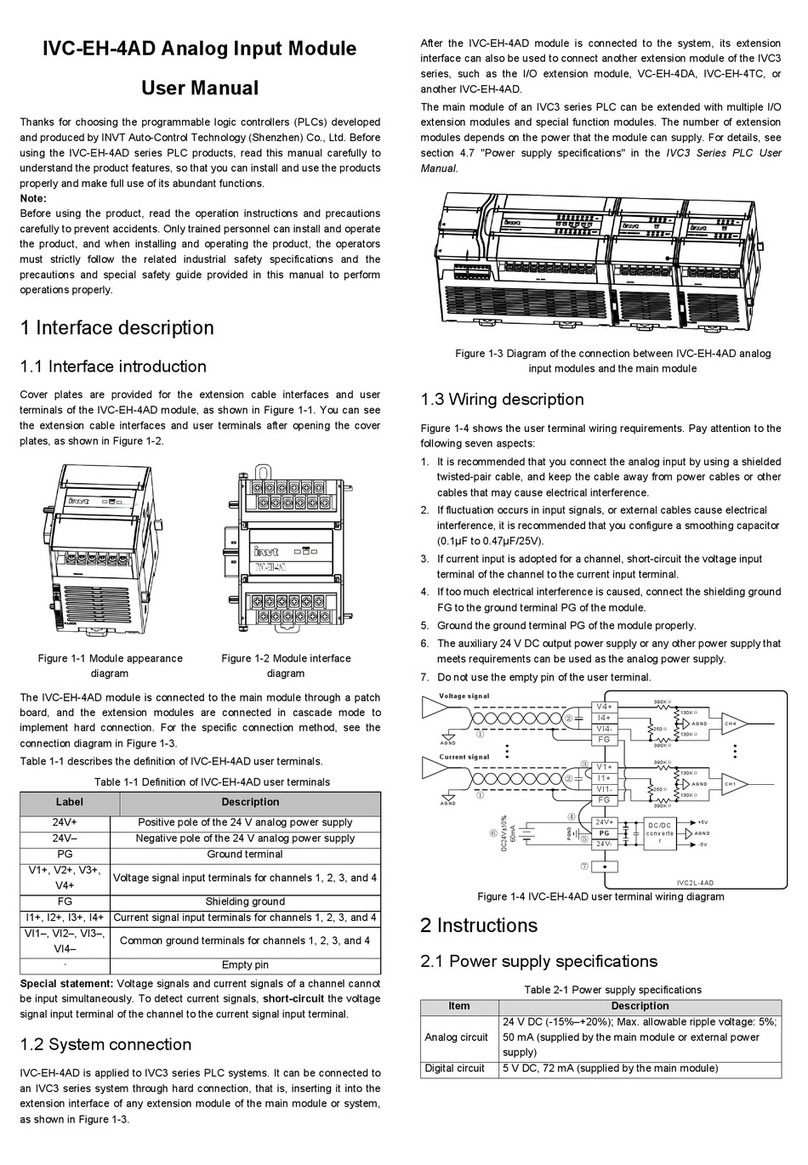

The following high-level block diagram represents the NI PXIe-7865.

Figure 1. NI PXIe-7865 Block Diagram

Device

Temperature

NI ASIC

Flash

Memory

DIO

CONNECTOR 0

(RAIO)

CONNECTOR 1

(RDIO)

Data/

Address/

Control

Overvoltage

Protection

+5 V

Reference

AO

AO (x24)

DAC

ADC AI

AI (x2)

INA

DIO (x32)

DDR3 RAM 100 MHz

OSC

Overvoltage

Protection

Overvoltage

Protection

NI PXIe-7865

CONNECTOR 2

(RAO)

Overvoltage

Protection

(x8)

(x16)

PXIe Connector

Kintex-7

FPGA

Bus

Switch

Pinout

© National Instruments 3

PXIe-7865 Features

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

AO15

AO14

AO13

AO12

AO11

AO10

AO9

AO8

NC

AOCH23

NC

AOCH22

AOCH21

NC

AOCH20

AOCH19

NC

AOCH18

AOCH17

NC

AOCH16

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

AOGND15

AOGND14

AOGND13

AOGND12

AOGND11

AOGND10

AOGND9

AOGND8

NC

AOGND23

NC

AOGND22

AOGND21

NC

AOGND20

AOGND19

NC

AOGND18

AOGND17

NC

AOGND16

68 34

67 33

66 32

65 31

64 30

63 29

62 28

61 27

60 26

59 25

58 24

57 23

56 22

55 21

54 20

53 19

52 18

51 17

50 16

49 15

48 14

47 13

46 12

45 11

44 10

43 9

42 8

41 7

40 6

39 5

38 4

37 3

36 2

35 1

CONNECTOR 2

(RAO)

TERMINAL 68

TERMINAL 34 TERMINAL 1

TERMINAL 35

+5V

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

AO7

AO6

AO5

AO4

AO3

AO2

AO1

AO0

AISENSE

NC

GND

NC

NC

GND

NC

NC

GND

NC

AI1+

AIGND0

AI0+

+5V

GND

GND

GND

GND

GND

GND

GND

GND

NC

NC

NC

NC

AOGND7

AOGND6

AOGND5

AOGND4

AOGND3

AOGND2

AOGND1

AOGND0

NC

NC

GND

NC

NC

GND

NC

NC

GND

NC

AI1–

AIGND1

AI0–

68 34

67 33

66 32

65 31

64 30

63 29

62 28

61 27

60 26

59 25

58 24

57 23

56 22

55 21

54 20

53 19

52 18

51 17

50 16

49 15

48 14

47 13

46 12

45 11

44 10

43 9

42 8

41 7

40 6

39 5

38 4

37 3

36 2

35 1

CONNECTOR 0

(RAIO)

TERMINAL 34 TERMINAL 1

TERMINAL 35

TERMINAL 68

DIO30

GND

DIO28

GND

DIO26

GND

DIO24

GND

DIO22

GND

DIO20

GND

DIO18

GND

DIO16

GND

DIO14

GND

DIO12

GND

DIO10

GND

DIO8

GND

DIO6

GND

DIO4

GND

DIO2

GND

DIO0

GND

EXTCLKIN

GND

DIO31

DIO29

GND

GND

DIO25

GND

DIO23

GND

DIO27

GND

DIO21

GND

DIO19

GND

DIO17

GND

DIO15

GND

DIO13

GND

DIO11

GND

DIO9

GND

DIO7

GND

DIO5

GND

DIO3

GND

DIO1

GND

GND

GND

68 34

67 33

66 32

65 31

64 30

63 29

62 28

61 27

60 26

59 25

58 24

57 23

56 22

55 21

54 20

53 19

52 18

51 17

50 16

49 15

48 14

47 13

46 12

45 11

44 10

43 9

42 8

41 7

40 6

39 5

38 4

37 3

36 2

35 1

CONNECTOR 1

(RDIO)

TERMINAL 68

TERMINAL 34 TERMINAL 1

TERMINAL 35

Table 1. NI PXIe-7865 Signal Descriptions

Signal Description

AI+ Positive analog input signal connection

AI- Negative analog input signal connection

AISENSE Reference connection for NRSE measurements

AIGND Ground reference for the analog input signal

AO Analog output signal connection

AOGND Ground reference for the analog output signal

DIO Digital input/output signal connection

EXTCLKIN External clock input source that can be used for

source synchronous acquisitions. The provided

clock source must be stable and glitch-free.

GND Ground connection

Supply (+5 Vout) 5 V power output connection for external

devices

ni.com

4

PXIe-7865 Features

Signal Description

NC No connection

The NI PXIe-7865 is protected from overvoltage and overcurrent conditions.

Note Refer to the NI PXIe-7865 Specifications, available at ni.com/

manuals for more information.

Note The pinout label on the lid of the SCB-68A accessory is

incompatible with the NI PXIe-7865. Refer to the NI 78xxR Pinout Labels

for the SCB-68A, available at ni.com/manuals for the compatible pinout

labels.

Connecting the NI PXIe-7865

NI recommends using the following cables and accessories with the NI PXIe-7865:

Table 2. Recommended Cables and Accessories

Connector Type Connector Block Cables

Analog I/O Connector 0 (RAIO) SCB-68A Noise Rejecting,

Shielded I/O Connector Block

(782536-01)

■SHC68-68-RMIO

Shielded Cable for the

Reconfigurable MIO

Connector, 68-pinD-Type

to 68-pin VHDCI,

1 m(189588-01)

■SHC68-68-RMIO

Shielded Cable for the

Reconfigurable MIO

Connector, 68-pinD-Type

to 68-pin VHDCI,

2 m(189588-02)

Analog Output Connector 2

(RAO)

Digital Connector 1 (RDIO) SCB-68 HSDIO Shielded 68-Pin

Connector Block for

Reconfigurable DIO & HSDIO

Products (782914-01)

■SHC68-C68-RDIO2

Shielded High Speed

Digital Cable for the

Reconfigurable DIO

Connector,

1 m(156166-01)

© National Instruments 5

PXIe-7865 Features

Connector Type Connector Block Cables

■SHC68-C68-RDIO2

Shielded High Speed

Digital Cable for the

Reconfigurable DIO

Connector,

2 m(156166-02)

Note The SCB-68A DIP switches must be set for Direct Feedthrough mode

for use with R Series devices. Visit ni.com/info and enter the Info Code

scb68acables for more information on the SCB-68A accessory.

Note NI is not liable for connections that exceed any of the maximum

ratings of input or output signals on the NI PXIe-7865 and on the computer

chassis. Refer to the NI PXIe-7865 Specifications, available at ni.com/info

for the maximum input and output ratings for each signal.

Analog Input

The NI PXIe-7865 provides connections for two AI channels. Each channel has an AI+

pin, AI- pin, and AIGND pin to which you can connect both single-ended or

dierential voltage signals. Use the AISENSE pin to connect non-referenced single-

ended signals.

Connecting Single-Ended Voltage Signals

To connect referenced single-ended voltage signals to the NI PXIe-7865, you must

connect the voltage ground signal to AI GND in order to keep the common-mode

voltage in the specified range.

ni.com

6

PXIe-7865 Features

Figure 2. Connecting Referenced Single-Ended Signals to the NI PXIe-7865

PGIA ADC

AI+

NI PXIe-7865

Connection

Accessory

AISENSE

AIGND

V1

+

–

Overvoltage

Protection

AI– Overvoltage

Protection

Overvoltage

Protection

To connect non-referenced single-ended voltage signals to the NI PXIe-7865, you

must connect the voltage ground signal to AI SENSE in order to keep the common-

mode voltage in the specified range.

Figure 3. Connecting Non-Referenced Single-Ended Signals to the NI PXIe-7865

PGIA ADC

AI+

NI PXIe-7865

Connection

Accessory

AISENSE

AIGND

Vcm

V1

+

–

+

–

Overvoltage

Protection

AI– Overvoltage

Protection

Overvoltage

Protection

Connecting Dierential Voltage Signals

You can connect grounded or floating dierential signal sources to the NI PXIe-7865.

Connect the positive voltage signal to the AI+ and the negative voltage signal to AI-.

To connect grounded dierential signals to the NI PXIe-7865, you must also connect

the signal reference to AI GND.

Figure 4. Connecting Grounded Dierential Signals to the NI PXIe-7865

PGIA ADC

AI+

NI PXIe-7865

Connection

Accessory

AISENSE

AIGND

Vcm

V1

+

–

+

–

Overvoltage

Protection

AI– Overvoltage

Protection

Overvoltage

Protection

© National Instruments 7

PXIe-7865 Features

To connect floating dierential signals to the NI PXIe-7865, you must connect the

negative and positive signals to AI GND through 1 MΩ resistors to keep the voltage

within the common-mode voltage range. If the voltage source is outside the

common-mode voltage range, the NI PXIe-7865 does not read data accurately.

Figure 5. Connecting Floating Dierential Signals to the NI PXIe-7865

PGIA ADC

AI+

NI PXIe-7865

Connection

Accessory

AISENSE

AIGND

V1

+

–

Overvoltage

Protection

AI– Overvoltage

Protection

Overvoltage

Protection

Analog Output

The NI PXIe-7865 provides connections for 24 analog output channels. Each channel

has an AO pin and AOGND pin to which you can connect a load.

Figure 6. Connecting a Load

NI PXIe-7865

Connection

Accessory

AOGND

LOAD

AO

DAC

Digital I/O

The NI PXIe-7865 provides connections for 32 digital input/output (DIO) channels.

Connector 1 contains 32 high-speed DIO channels that can run up to 20 MHz signal

frequencies. You can configure each channel as input or output.

Each DIO line on the NI PXIe-7865 are TTL-compatible. When configured as inputs,

they can receive signals from 5 V TTL, 3.3 V LVTTL, and 3.3 V LVCMOS. When

configured as outputs, they can send signals to 5 V TTL, 3.3 V LVTTL, and

3.3 V LVCMOS devices. Because the digital outputs can provide nominal output

swing of 0 V to 3.3 V, which will meet the 5 V TTL threshold for a digital logic high,

despite not being at a 5 V logic level. Refer to the device specifications on ni.com/

manuals for more information.

ni.com

8

PXIe-7865 Features

Figure 7. Connecting to the DIO Channels

NI PXIe-7865

Power

FPGA

Connection

Accessory

DIO0

DIO1

DIO30

DIO31

Connector 1 (DIO)

1

2

1. High-speed signal frequencies up to 20 MHz that is compatible with 5 V TTL,

3.3 V LVTTL, and 3.3 V LVCMOS.

2. LED

The DIO channels connect to the FPGA through digital bus switches, which have

overvoltage and undervoltage protection as well as over current protection with a

Positive Thermal Coeicient (PTC) resistor. Refer to the device specifications on

ni.com/manuals for more information about the maximum voltage and current.

When the system powers on, the DIO channels are set as input low with pull-down

resistors. To set another power-on state, you can configure the NI PXIe-7865 to load

a VI when the system powers on. The VI can then set the DIO lines to any power-on

state. Visit ni.com/info and enter RSeries_PowerUpStates to learn more about

configuring the power-up states for the NI PXIe-7865.

All the high-speed DIO channels on Connector 1 are routed with a 50 Ω characteristic

trace impedance. Route all external circuitry with a similar impedance to ensure

best signal quality. NI recommends performing signal integrity measurements to

test the eect of signal routing with the cable and connection accessory for your

application.

Field Wiring Considerations

Environmental noise can seriously aect the measurement accuracy of the device if

you do not take proper care when running signal wire between signal sources and

the device. The following recommendations mainly apply to AI signal routing to the

device, as well as signal routing in general.

Take the following precautions to minimize noise pickup and maximize

measurement accuracy:

■Use dierential AI connections to reject common-mode noise.

© National Instruments 9

PXIe-7865 Features

■Use individually shielded, twisted-pair wires to connect AI signals to the

device. With this type of wire, the signal attached to the positive and negative

inputs are twisted together and then covered with a shield. You then connect

this shield only at one point to the signal source ground. This kind of

connection is required for signals traveling through areas with large magnetic

fields or high electromagnetic interference.

■Route signals to the device carefully. Keep cabling away from noise sources,

such as video monitors and analog signals.

Use the following recommendations for all signal connections to the NI PXIe-7865:

■Separate NI PXIe-7865 signal lines from high-current or high-voltage lines.

These lines can induce currents in or voltages on the NI PXIe-7865 signal lines

if they run in parallel paths at a close distance. To reduce the magnetic

coupling between lines, separate them by a reasonable distance if they run in

parallel or run the lines at right angles to each other.

■Do not run signal lines through conduits that also contain power lines.

■Protect signal lines from magnetic fields caused by electric motors, welding

equipment, breakers, or transformers by running them through special metal

conduits.

■To minimize signal-to-signal skew within each digital channel, maintain

signal lines' length within 1 inch of dierence.

+5 V Power Source

Use the +5 V terminals on the I/O connector supply +5 V referenced to GND to power

external circuitry.

Caution Never connect the +5 V power terminals to analog or digital

ground or any other voltage source on the NI PXIe-7865 or any other

device. Doing so can damage the device and the computer. National

Instruments is not liable for damage resulting from such a connection.

The power rating is 4.75 to 5.1 V DC at 0.5 A.

NI Services

ni.com

10

PXIe-7865 Features

Visit ni.com/support to find support resources including documentation,

downloads, and troubleshooting and application development self-help such as

tutorials and examples.

Visit ni.com/services to learn about NI service oerings such as calibration options,

repair, and replacement.

Visit ni.com/register to register your NI product. Product registration facilitates

technical support and ensures that you receive important information updates from

NI.

NI corporate headquarters is located at 11500 N Mopac Expwy, Austin, TX,

78759-3504, USA.

© National Instruments 11

PXIe-7865 Features

© 2023 National Instruments Corporation.

Table of contents

Other NI I/O System manuals