NI PXIe-4322 User manual

NI SC Express

NI PXIe-4322 User Manual

NI PXIe-4322 User Manual

April 2013

373754A-01

Support

Worldwide Technical Support and Product Information

ni.com

Worldwide Offices

Visit ni.com/niglobal to access the branch office Web sites, which provide up-to-date

contact information, support phone numbers, email addresses, and current events.

National Instruments Corporate Headquarters

11500 North Mopac Expressway Austin, Texas 78759-3504 USA Tel: 512 683 0100

For further support information, refer to the Technical Support and Professional Services

appendix. To comment on National Instruments documentation, refer to the National

Instruments Web site at ni.com/info and enter the Info Code feedback.

©2013 National Instruments. All rights reserved.

Important Information

Warranty

The NI PXIe-4322 is warranted against defects in materials and workmanship for a period of one year from the date of

shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace

equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions,

due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other

documentation. National Instruments will, at its option, repair or replace software media that do not execute programming

instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not

warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of

the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of

returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this document is accurate. The document has been carefully reviewed

for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to

make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should

consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising

out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY

WARRANTY OF MERCHANTABILITY OR FITNESS FOR APARTICULAR PURPOSE. CUSTOMER’SRIGHT TO RECOVER DAMAGES CAUSED BY FAULT

OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER.

NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL

OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments

will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National

Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any

delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages,

defects, malfunctions, or service failures caused by owner’s failure to follow the National Instruments installation, operation,

or maintenance instructions; owner’s modification of the product; owner’s abuse, misuse, or negligent acts; and power failure

or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical,

including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the

prior written consent of National Instruments Corporation.

National Instruments respects the intellectual property of others, and we ask our users to do the same. NI software is protected

by copyright and other intellectual property laws. Where NI software may be used to reproduce software or other materials

belonging to others, you may use NI software only to reproduce materials that you may reproduce in accordance with the

terms of any applicable license or other legal restriction.

End-User License Agreements and Third-Party Legal Notices

You can find end-user license agreements (EULAs) and third-party legal notices in the following locations:

• Notices are located in the <National Instruments>\_Legal Information and <National Instruments>

directories.

• EULAs are located in the <National Instruments>\Shared\MDF\Legal\license directory.

•Review

<National Instruments>\_Legal Information.txt for more information on including legal information

in installers built with NI products.

Trademarks

Refer to the NI Trademarks and Logo Guidelines at ni.com/trademarks for more information on National Instruments

trademarks.

ARM, Keil, and µVision are trademarks or registered of ARM Ltd or its subsidiaries.

LEGO, the LEGO logo, WEDO, and MINDSTORMS are trademarks of the LEGO Group. ©2013 The LEGO Group.

TETRIX by Pitsco is a trademark of Pitsco, Inc.©2013

FIELDBUS FOUNDATION™and FOUNDATION™are trademarks of the Fieldbus Foundation.

EtherCAT®is a registered trademark of and licensed by Beckhoff Automation GmbH.

CANopen®is a registered Community Trademark of CAN in Automation e.V.

DeviceNet™and EtherNet/IP™are trademarks of ODVA.

Go!, SensorDAQ, and Vernier are registered trademarks of Vernier Software & Technology. Vernier Software & Technology

and vernier.com are trademarks or trade dress.

Xilinx is the registered trademark of Xilinx, Inc.

Taptite and Trilobular are registered trademarks of Research Engineering & Manufacturing Inc.

FireWire®is the registered trademark of Apple Inc.

Linux®is the registered trademark of Linus Torvalds in the U.S. and other countries.

Handle Graphics®, MATLAB®, Real-Time Workshop®, Simulink®, Stateflow®, and xPC TargetBox®are registered

trademarks, and TargetBox™and Target Language Compiler™are trademarks of The MathWorks, Inc.

Tektronix®, Tek, and Tektronix, Enabling Technology are registered trademarks of Tektronix, Inc.

The Bluetooth®word mark is a registered trademark owned by the Bluetooth SIG, Inc.

The ExpressCard™word mark and logos are owned by PCMCIA and any use of such marks by National Instruments is under

license.

The mark LabWindows is used under a license from Microsoft Corporation. Windows is a registered trademark of Microsoft

Corporation in the United States and other countries.

Other product and company names mentioned herein are trademarks or trade names of their respective companies.

Members of the National Instruments Alliance Partner Program are business entities independent from National Instruments

and have no agency, partnership, or joint-venture relationship with National Instruments.

Patents

For patents covering National Instruments products/technology, refer to the appropriate location: Help»Patents in your

software, the patents.txt file on your media, or the National Instruments Patent Notice at ni.com/patents.

Export Compliance Information

Refer to the Export Compliance Information at ni.com/legal/export-compliance for the National Instruments global

trade compliance policy and how to obtain relevant HTS codes, ECCNs, and other import/export data.

WARNING REGARDING USE OF NATIONAL INSTRUMENTS PRODUCTS

(1) NATIONAL INSTRUMENTS PRODUCTS ARE NOT DESIGNED WITH COMPONENTS AND TESTING FOR A

LEVEL OF RELIABILITY SUITABLE FOR USE IN OR IN CONNECTION WITH SURGICAL IMPLANTS OR AS

CRITICAL COMPONENTS IN ANY LIFE SUPPORT SYSTEMS WHOSE FAILURE TO PERFORM CAN

REASONABLY BE EXPECTED TO CAUSE SIGNIFICANT INJURY TO A HUMAN.

(2) IN ANY APPLICATION, INCLUDING THE ABOVE, RELIABILITY OF OPERATION OF THE SOFTWARE

PRODUCTS CAN BE IMPAIRED BY ADVERSE FACTORS, INCLUDING BUT NOT LIMITED TO FLUCTUATIONS

IN ELECTRICAL POWER SUPPLY, COMPUTER HARDWARE MALFUNCTIONS, COMPUTER OPERATING

SYSTEM SOFTWARE FITNESS, FITNESS OF COMPILERS AND DEVELOPMENT SOFTWARE USED TO

DEVELOP AN APPLICATION, INSTALLATION ERRORS, SOFTWARE AND HARDWARE COMPATIBILITY

PROBLEMS, MALFUNCTIONS OR FAILURES OF ELECTRONIC MONITORING OR CONTROL DEVICES,

TRANSIENT FAILURES OF ELECTRONIC SYSTEMS (HARDWARE AND/OR SOFTWARE), UNANTICIPATED

USES OR MISUSES, OR ERRORS ON THE PART OF THE USER OR APPLICATIONS DESIGNER (ADVERSE

FACTORS SUCH AS THESE ARE HEREAFTER COLLECTIVELY TERMED “SYSTEM FAILURES”). ANY

APPLICATION WHERE A SYSTEM FAILURE WOULD CREATE A RISK OF HARM TO PROPERTY OR PERSONS

(INCLUDING THE RISK OF BODILY INJURY AND DEATH) SHOULD NOT BE RELIANT SOLELY UPON ONE

FORM OF ELECTRONIC SYSTEM DUE TO THE RISK OF SYSTEM FAILURE. TO AVOID DAMAGE, INJURY, OR

DEATH, THE USER OR APPLICATION DESIGNER MUST TAKE REASONABLY PRUDENT STEPS TO PROTECT

AGAINST SYSTEM FAILURES, INCLUDING BUT NOT LIMITED TO BACK-UP OR SHUT DOWN MECHANISMS.

BECAUSE EACH END-USER SYSTEM IS CUSTOMIZED AND DIFFERS FROM NATIONAL INSTRUMENTS'

TESTING PLATFORMS AND BECAUSE A USER OR APPLICATION DESIGNER MAY USE NATIONAL

INSTRUMENTS PRODUCTS IN COMBINATION WITH OTHER PRODUCTS IN A MANNER NOT EVALUATED

OR CONTEMPLATED BY NATIONAL INSTRUMENTS, THE USER OR APPLICATION DESIGNER IS

ULTIMATELY RESPONSIBLE FOR VERIFYING AND VALIDATING THE SUITABILITY OF NATIONAL

INSTRUMENTS PRODUCTS WHENEVER NATIONAL INSTRUMENTS PRODUCTS ARE INCORPORATED IN A

SYSTEM OR APPLICATION, INCLUDING, WITHOUT LIMITATION, THE APPROPRIATE DESIGN, PROCESS

AND SAFETY LEVEL OF SUCH SYSTEM OR APPLICATION.

© National Instruments |v

Contents

Chapter 1

Getting Started

Installation ........................................................................................................................ 1-1

Module Specifications ...................................................................................................... 1-1

Module Accessories and Cables ....................................................................................... 1-1

Chapter 2

Using the NI PXIe-4322

Connecting Signals ........................................................................................................... 2-1

Increasing Output Voltage Range in Voltage Output Mode .................................... 2-2

Increasing Output Current Range in Current Output Mode ..................................... 2-3

Device Pinout ...................................................................................................................2-4

I/O Connector Signal Description ............................................................................ 2-6

NI PXIe-4322 Block Diagram.......................................................................................... 2-7

Analog Output Data Generation Methods ........................................................................ 2-7

Software-Timed Generations.................................................................................... 2-7

Hardware-Timed Generations .................................................................................. 2-8

Analog Output Timing Signals......................................................................................... 2-9

AO Sample Clock Signal.......................................................................................... 2-9

Using an Internal Source .................................................................................. 2-9

Using an External Source ................................................................................. 2-10

Routing AO Sample Clock Signal to an Output Terminal ............................... 2-10

Other Timing Requirements ............................................................................. 2-10

AO Sample Clock Timebase Signal ......................................................................... 2-10

Getting Started with AO Applications in Software .......................................................... 2-11

External Reference Clock......................................................................................... 2-11

10 MHz Reference Clock ................................................................................. 2-12

Synchronizing Multiple Devices .............................................................................. 2-13

Triggering ................................................................................................................. 2-13

Digital Input Triggering.................................................................................... 2-13

TB-4322 Accessory .......................................................................................... 2-14

Accessory Auto-Detection................................................................................ 2-14

Isolation ............................................................................................................ 2-14

Chapter 3

NI SC Express Considerations

PXI and NI SC Express Clock and Trigger Signals ......................................................... 3-1

PXIe_CLK100 .......................................................................................................... 3-1

PXIe_SYNC100 ....................................................................................................... 3-1

PXI_CLK10.............................................................................................................. 3-1

PXI Triggers ............................................................................................................. 3-1

PXI_STAR Trigger................................................................................................... 3-2

Contents

vi |ni.com

PXI_STAR Filters..................................................................................................... 3-2

PXIe_DSTAR <A..C> .............................................................................................. 3-2

Data Transfer Methods ..................................................................................................... 3-3

Appendix A

Technical Support and Professional Services

List of Figures

Figure 2-1. Connecting a Load to a Channel Diagram............................................. 2-1

Figure 2-2. Output Circuit Grounding......................................................................2-1

Figure 2-3. Output Circuitry of One Channel Diagram ........................................... 2-2

Figure 2-4. Cascaded Voltage Output Channels Diagram .......................................2-3

Figure 2-5. Cascade Current Output Channels Diagram..........................................2-4

Figure 2-6. NI PXIe-4322 Block Diagram............................................................... 2-7

Figure 2-7. Analog Output Timing Options............................................................. 2-9

Figure 2-8. AO Sample Clock and AO Start Trigger............................................... 2-10

Figure 2-9. External Clock Reference ...................................................................... 2-12

List of Tables

Table 2-1. Front Signal Pin Assignments .............................................................. 2-5

Table 2-2. I/O Connector Signal Descriptions........................................................2-6

Table 2-3. Clock Signal Sourcing ........................................................................... 2-12

Table 3-1. PXIe_DSTAR Line Descriptions .......................................................... 3-2

Compliance

Electromagnetic Compatibility Guidelines

This product was tested and complies with the regulatory requirements and limits for electromagnetic

compatibility (EMC) stated in the product specifications. These requirements and limits provide reasonable

protection against harmful interference when the product is operated in the intended operational

electromagnetic environment.

This product is intended for use in industrial locations. However, harmful interference may occur in some

installations, when the product is connected to a peripheral device or test object, or if the product is used in

residential or commercial areas. To minimize interference with radio and television reception and prevent

unacceptable performance degradation, install and use this product in strict accordance with the instructions

in the product documentation.

Furthermore, any modifications to the product not expressly approved by National Instruments could void

your authority to operate it under your local regulatory rules.

Caution To ensure the specified EMC performance, operate this product only with shielded,

twisted-pair cables and shielded accessories.

Caution To ensure the specified EMC performance, the length of all I/O cables must be no

longer than 30 m (100 ft).

© National Instruments |1-1

1

Getting Started

The NI PXIe-4322 provides eight, simultaneously updated, analog output channels, each with

channel-to-channel and channel-to-earth isolation. Each channel has a 16-bit digital-to-analog

converter (DAC) and can be configured as voltage output mode or current output mode. The

voltage mode has ±16 V output range and the current mode has ±20 mA output range.

Installation

Refer to the NI PXIe-4322 and TB-4322 Installation Guide and Terminal Block Specifications

for step-by-step software and hardware installation instructions.

Module Specifications

Refer to the NI PXIe-4322 Specifications document for module specifications.

Module Accessories and Cables

Refer to the NI PXIe-4322 and TB-4322 Installation Guide and Terminal Block Specifications

document for information about supported accessories and cables.

Caution When hazardous voltages (>30 Vrms/42.4 Vpk/60 VDC) are present on

any terminal, safety low-voltage (≤30 Vrms/42.4 Vpk /60 VDC) cannot be connected

to any other terminal.

Caution Do not supply hazardous voltages (>30 Vrms/42.4 Vpk/60 VDC) to the

terminal block without the terminal block being connected to the NI PXIe-4322.

© National Instruments |2-1

2

Using the NI PXIe-4322

This chapter describes how to make connections to the NI PXIe-4322 module. It also provides

the front signal pin assignments of the module.

Connecting Signals

Note Refer to the NI PXIe-4322 and TB-4322 Installation Guide and Terminal

Block Specifications document for details about signal terminal locations.

You can connect a load to each channel of the NI PXIe-4322. Connect the positive lead of the

load to the AO+ terminal. Connect the ground of the load to the corresponding AO- terminal as

shown in Figure 2-1.

Figure 2-1. Connecting a Load to a Channel Diagram

The analog output channels are floating with respect to earth ground and each other. If you make

a ground-referenced connection between the signal source and the NI PXIe-4322 output, make

sure the voltage on the AO+ and AO- connections are in the safety voltage range to ensure the

proper operation. Refer to the NI PXIe-4322 Specifications for more information about Safety

Vo l t a g e .

Figure 2-2. Output Circuit Grounding

PXIe-4322 TB-4322

AO+

AO–

Load

PXIe-4322 TB-4322

AO+

AO–

Load

Earth Ground

CM

2-2 |ni.com

Chapter 2 Using the NI PXIe-4322

Each channel has a DAC that produces a voltage or current signal. Each channel provides an

independent signal path, enabling you to update all eight channels simultaneously. Each channel

also has overvoltage and short-circuit protection. Refer to the NI PXIe-4322 Specifications for

more information about the overvoltage and short-circuit protection. The output circuitry for one

channel of the NI PXIe-4322 is shown in Figure 2-3.

Figure 2-3. Output Circuitry of One Channel Diagram

Increasing Output Voltage Range in Voltage Output

Mode

Each channel of the NI PXIe-4322 has a nominal output voltage range of ±16 V and can drive

up to ±20 mA of current. If you want to increase the nominal output voltage range, you can

cascade up to eight output channels, as shown in Figure 2-4, for a maximum of ±128 V nominal.

Caution Cascading more than eight output channels of multiple NI PXIe-4322

modules violates overvoltage protection ratings.

Note The NI PXIe-4322 outputs can source and sink current; therefore, it is not

possible to increase the current drive by connecting voltage output channels in

parallel, as shown in the lower portion of Figure 2-4 and is indicated by being crossed

out.

PXIe-4322 TB-4322

Overvoltage/

Short-Circuit

Protection

Amp

Isolated

DAC

AO+

AOS+

AO–

AO+

AO–

AOS–

© National Instruments |2-3

NI PXIe-4322 User Manual

Figure 2-4. Cascaded Voltage Output Channels Diagram

Increasing Output Current Range in Current Output

Mode

Each channel of the NI PXIe-4322 has a nominal output current range of ±20 mA within its

nominal compliance voltage of ±16 V. If you want to increase the nominal output current range,

you can connect up to eight current mode output channels in parallel, as shown in Figure 2-5, for

a maximum of ±160 mA nominal.

Note The NI PXIe-4322 output channels cannot be connected in series when they

are in current mode, as shown in the lower portion of Figure 2-5 and is indicated by

being crossed out.

PXIe-4322 TB-4322

AO0+

AO0–

AO1+

AO1–

AO2+

AO6–

AO7+

AO7–

Load

PXIe-4322

AO0+

AO0–

AO1+

AO1–

AO2+

AO6–

AO7+

AO7–

Load

TB-4322

2-4 |ni.com

Chapter 2 Using the NI PXIe-4322

Figure 2-5. Cascade Current Output Channels Diagram

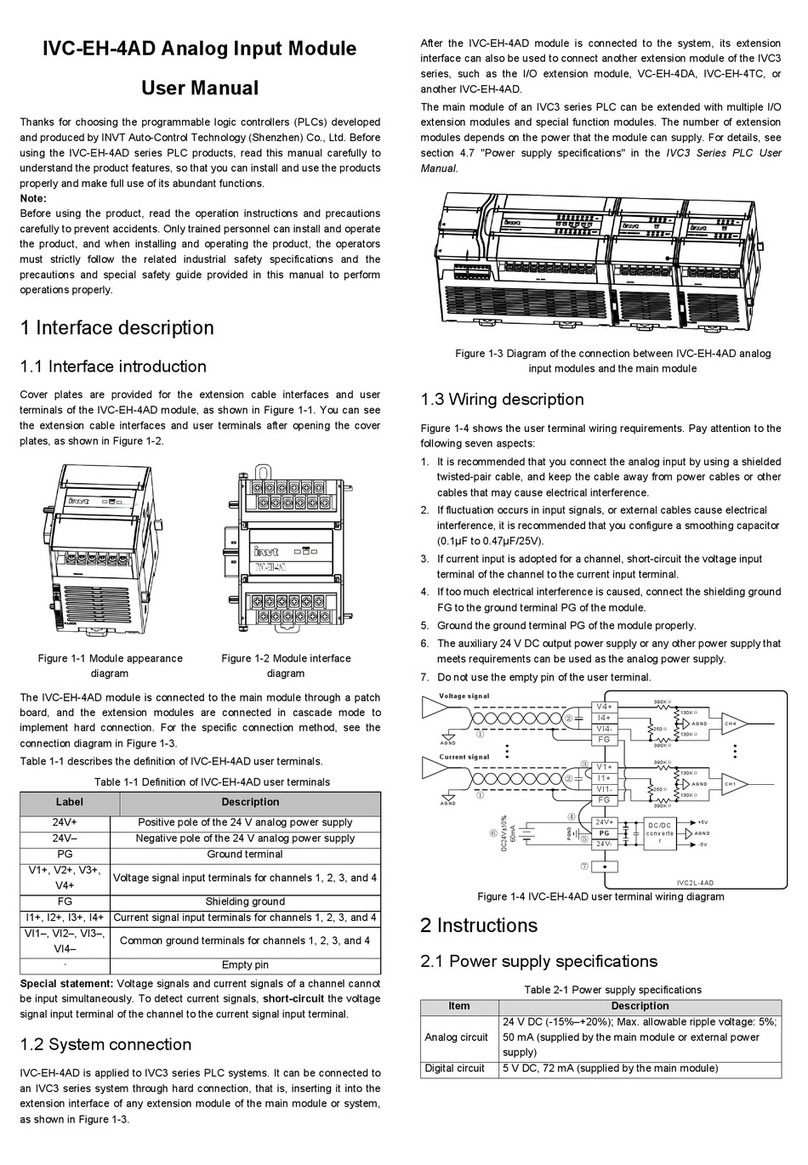

Device Pinout

This is the pinout represented on the front connector of the NI PXIe-4322. Refer to the I/O

Connector Signal Description section for definitions of each signal. Refer to the terminal block

installation guide for signal locations on the terminal block.

PXIe-4322 TB-4322

PXIe-4322 TB-4322

AO0+

AO0–

AO1+

AO1–

AO2+

AO6–

AO7+

AO7–

Load

Load

AO0+

AO0–

AO1+

AO1–

AO2+

AO6–

AO7+

AO7–

© National Instruments |2-5

NI PXIe-4322 User Manual

Table 2-1. Front Signal Pin Assignments

Front Connector Diagram Pin Number Column A Column B Column C Channel

32 —AO 0+ AOS 0+ 0

31 —AO 0- AOS 0-

30 — — —

29 —AO 1+ AOS 1+ 1

28 —AO 1- AOS 1-

27 — — —

26 —AO 2+ AOS 2+ 2

25 —AO 2- AOS 2-

24 — — —

23 —AO 3+ AOS 3+ 3

22 —AO 3- AOS 3-

21 — — —

20 —AO 4+ AOS 4+ 4

19 —AO 4- AOS 4-

18 — — —

17 —AO 5+ AOS 5+ 5

16 —AO 5- AOS 5-

15 — — —

14 —AO 6+ AOS 6+ 6

13 —AO 6- AOS 6-

12 — — —

11 —AO 7+ AOS 7+ 7

10 —AO 7- AOS 7-

9 — — —

8 — — — No

Channel

7 — — —

6 — — —

5 — — —

4 — — —

3 — — —

2RSVD RSVD RSVD

1RSVD RSVD RSVD

— is no connection, RSVD is reserved

Column

A B C

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

2-6 |ni.com

Chapter 2 Using the NI PXIe-4322

I/O Connector Signal Description

Table 2-2 describes the signals found on the I/O connectors.

Table 2-2. I/O Connector Signal Descriptions

Signal Names

NI-DAQmx

Signal Name Description

AO <0..7>+,

AO <0..7>-

AO <0..7> Analog Output Channels 0 to 7. AO+ is the positive

output terminal and AO- is the negative output

terminal.

AOS <0..7>+,

AOS <0..7>-

—The sense lines of analog output channel 0 to 7.

AOS+ is the positive sense line and AOS- is the

negative sense line.

RSVD —These pins are reserved for communication with the

accessory.

Notes: AOS± is connected to AO± at the terminal block user connector.

When using a custom terminal block, connect AOS± to AO± at the terminal block.

© National Instruments |2-7

NI PXIe-4322 User Manual

NI PXIe-4322 Block Diagram

Figure 2-6 shows the block diagram of the NI PXIe-4322 module.

Figure 2-6. NI PXIe-4322 Block Diagram

Analog Output Data Generation Methods

When performing an analog output operation, you can perform software-timed or

hardware-timed generations.

Software-Timed Generations

With a software-timed generation, software controls the rate at which data is generated. Software

sends a separate command to the hardware to initiate each DAC conversion. In NI-DAQmx,

software-timed generations are referred to as on-demand timing. Software-timed generations are

also referred to as immediate or static operations. They are typically used for writing a single

value out, such as a constant DC voltage.

AO0+

AOS0+

AOS0–

AO0–

AO6+

AOS6+

AOS6–

AO6–

AO7+

AOS7+

AOS7–

AO7–

PXIe

Bus Interface PXIe Bus

Analog Output

Circuit 6

300 VrmsIsolation

300 VrmsIsolation

IsolatorIsolator

300 VrmsIsolation

300 VrmsIsolation

Isolator

Analog Output

Circuit 7

Analog Output

Circuit 0

2-8|ni.com

Chapter 2 Using the NI PXIe-4322

Hardware-Timed Generations

With a hardware-timed generation, a digital hardware signal controls the rate of the generation.

This signal can be generated internally on your device or provided externally.

Hardware-timed generations have several advantages over software-timed generations:

• The time between samples can be much shorter.

• The timing between samples can be deterministic.

• Hardware-timed acquisitions can use hardware triggering.

Hardware-timed operations can be buffered or hardware-timed single point (HWTSP). A buffer

is a temporary storage in computer memory for to-be-transferred samples.

•Hardware-timed single point (HWTSP)—Typically, HWTSP operations are used to

write single samples at known time intervals. While buffered operations are optimized for

high throughput, HWTSP operations are optimized for low latency and low jitter. In

addition, HWTSP can notify software if it falls behind hardware. These features make

HWTSP ideal for real-time control applications. HWTSP operations, in conjunction with

the wait for next sample clock function, provide tight synchronization between the software

layer and the hardware layer. Refer to the NI Developer Zone document, NI-DAQmx

Hardware-Timed Single Point Lateness Checking, for more information. To access this

document, go to ni.com/info and enter the Info Code daqhwtsp.

•Buffered—In a buffered generation, data is moved from a PC buffer to the onboard FIFO

of the DAQ device using DMA before it is written to the DACs one sample at a time.

Buffered generation typically allows for much faster transfer rates than non-buffered

acquisitions because data is moved in large blocks, rather than one point at a time.

One property of buffered I/O operations is the sample mode. The sample mode can be either

finite or continuous:

– Finite sample mode generation refers to the generation of a specific, predetermined

number of data samples. Once the specified number of samples has been written out,

the generation stops.

– Continuous generation refers to the generation of an unspecified number of samples.

Instead of generating a set number of data samples and stopping, a continuous

generation continues until you stop the operation. There are several different methods

of continuous generation that control what data is written. These methods are

regeneration, FIFO regeneration and non-regeneration modes:

• Regeneration is the repetition of the data that is already in the buffer. Standard

regeneration is when data from the PC buffer is continually downloaded to the

FIFO to be written out. New data can be written to the PC buffer at any time

without disrupting the output. Use the NI-DAQmx write property RegenMode to

allow (or not allow) regeneration. The NI-DAQmx default is to allow

regeneration.

© National Instruments |2-9

NI PXIe-4322 User Manual

• With FIFO regeneration, the entire buffer is downloaded to the FIFO and

regenerated from there. Once the data is downloaded, new data cannot be written

to the FIFO. To use FIFO regeneration, the entire buffer must fit within the FIFO

size. The advantage of using FIFO regeneration is that it does not require

communication with the main host memory once the operation is started, thereby

preventing any problems that may occur due to excessive bus traffic. Use the

NI-DAQmx AO channel property, UseOnlyOnBoardMemory to enable or

disable FIFO regeneration.

• With non-regeneration, old data is not repeated. New data must be continually

written to the buffer. If the program does not write new data to the buffer at a fast

enough rate to keep up with the generation, the buffer underflows and causes an

error.

Analog Output Timing Signals

Figure 2-7 summarizes all of the timing options provided by the analog output timing engine.

Figure 2-7. Analog Output Timing Options

The NI PXIe-4322 features the following analog output (waveform generation) timing signals:

•AO Sample Clock Signal (digital filtering supported)

•AO Sample Clock Timebase Signal (digital filtering not supported)

AO Sample Clock Signal

Use the AO Sample Clock (ao/SampleClock) signal to initiate AO samples. Each sample

updates the outputs of all of the DACs. You can specify an internal or external source for AO

Sample Clock. You also can specify whether the DAC update begins on the rising edge or falling

edge of AO Sample Clock.

Using an Internal Source

The AO Sample Clock Timebase (divided down) internal signal can drive AO Sample Clock.

PXI_Trig

PXI_STA R

20 MHz Timebase

100 kHz Timebase

PXI_CLK10

Programmable

Clock

Divider

AO Sample Clock

Timebase

PXI_Trig

PXI_STA R

100 MHz Timebase

DSTAR <A..B>

DSTAR <A..B>

AO Sample Clock

2-10 |ni.com

Chapter 2 Using the NI PXIe-4322

A programmable internal counter divides down the AO Sample Clock Timebase signal.

Several other internal signals can be routed to AO Sample Clock through internal routes. Refer

to Device Routing in MAX in the NI-DAQmx Help or the LabVIEW Help for more information.

Using an External Source

Use one of the following external signals as the source of AO Sample Clock:

• PXI_Trig <0..7>

• PXI_STAR

• PXIe-DSTAR<A,B>

Routing AO Sample Clock Signal to an Output Terminal

You can route AO Sample Clock (as an active low signal) out to any PXI_Trig <0..7>, or

PXIe-DSTARC terminal.

Other Timing Requirements

The AO timing engine on your device internally generates AO Sample Clock unless you select

some external source. AO Start Trigger starts the timing engine and either the software or

hardware can stop it once a finite generation completes. When using the AO timing engine, you

also can specify a configurable delay from AO Start Trigger to the first AO Sample Clock pulse.

By default, this delay is two ticks of AO Sample Clock Timebase.

Figure 2-8 shows the relationship of AO Sample Clock to AO Start Trigger.

Figure 2-8. AO Sample Clock and AO Start Trigger

AO Sample Clock Timebase Signal

The AO Sample Clock Timebase (ao/SampleClockTimebase) signal is divided down to provide

a source for AO Sample Clock.

You can route any of the following signals to be the AO Sample Clock Timebase signal:

• 100 MHz Timebase (default)

AO Sample Clock Timebase

AO Start Trigger

AO Sample Clock

Delay

From

Start

Trigger

© National Instruments |2-11

NI PXIe-4322 User Manual

•20MHzTimebase

• 100 kHz Timebase

• PXI_CLK10

• PXI_Trig <0..7>

• PXI_STAR

• PXIe-DSTAR<A,B>

AO Sample Clock Timebase is not available as an output on the I/O connector.

You might use AO Sample Clock Timebase if you want to use an external sample clock signal,

but need to divide the signal down. If you want to use an external sample clock signal, but do

not need to divide the signal, then you should use AO Sample Clock rather than AO Sample

Clock Timebase.

Getting Started with AO Applications in Software

You can use the NI PXIe-4322 modules in the following analog output applications:

• Single-point (on-demand) generation

• Finite generation

• Continuous generation

• Waveform generation

You can perform these generations through programmed I/O or DMA data transfer mechanisms.

Some of the applications also use start triggers and pause triggers.

Note For more information about programming analog output applications and

triggers in software, refer to the NI-DAQmx Help in NI-DAQmx 9.7 or later, or the

LabVIEW Help in LabVIEW 2009 or later.

NI PXIe-4322 modules use the NI-DAQmx driver. NI-DAQmx includes a collection of

programming examples to help you get started developing an application. You can modify

example code and save it in an application. You can use examples to develop a new application

or add example code to an existing application.

To locate LabVIEW, LabWindows™/CVI™, Measurement Studio, Visual Basic, and ANSI C

examples, refer to the KnowledgeBase document, Where Can I Find NI-DAQmx Examples?, by

going to ni.com/info and entering the Info Code daqmxexp.

For additional examples, refer to zone.ni.com.

External Reference Clock

An external reference clock can be used as a source for the internal timebase on the

NI PXIe-4322. This clock can be sourced using the signals shown in Table 2-3. Since the clock

2-12 |ni.com

Chapter 2 Using the NI PXIe-4322

is the input of a PLL, it must be 5 MHz, 10 MHz, 20 MHz, or 100 MHz. A PLL locks to the

signal and produces a 100 MHz output, which is then divided down to produce the three

timebases of 100 MHz, 20 MHz and 100 kHz. These timebases can then be used to generate

sample clocks on the device. This circuit also enables the output of a 10 MHz RefClk that can

be routed to PXI_Trig <0..7> and used by another device as its own External Reference Clock

as shown in Figure 2-9.

Figure 2-9. External Clock Reference

Caution Do not disconnect an external reference clock once the modules have been

synchronized or are used by a task. Doing so may cause NI-DAQmx to return an

error. Make sure that all tasks using a reference clock are stopped before

disconnecting it.

10 MHz Reference Clock

The 10 MHz reference clock can be used to synchronize other devices to the NI PXIe-4322

module. The 10 MHz reference clock can be routed to the PXI_Trig <0..7> terminals. Other

devices connected to the PXI_Trig bus can use this signal as a clock input.

The 10 MHz reference clock is generated by dividing down the onboard oscillator.

Table 2-3. Clock Signal Sourcing

Signal Description

PXI_Trig<0..7> Bi-Directional bus connecting each board in the chassis.

PXIe_Clk100 100 MHz clock routed to all slots in the chassis.

PXI_STAR Point-to-point route from the System Timing Slot to all other slots.

PXIe_DSTAR <A, B> Point-to-point differential routes from the System Timing Slot to

all other slots.

External

Reference

Clock

÷ 200

Onboard

100 MHz

Oscillator

PLL

÷ 5

÷ 10

PXI_Trig <0..7>

PXIe_CLK100

PXI_STA R

PXIe_DSTAR<A,B>

10 MHz RefClk (To PXI_Trig <0..7>

Output Selectors)

100 MHz

Timebase

20 MHz

Timebase

100 kHz

Timebase

Table of contents

Other NI I/O System manuals