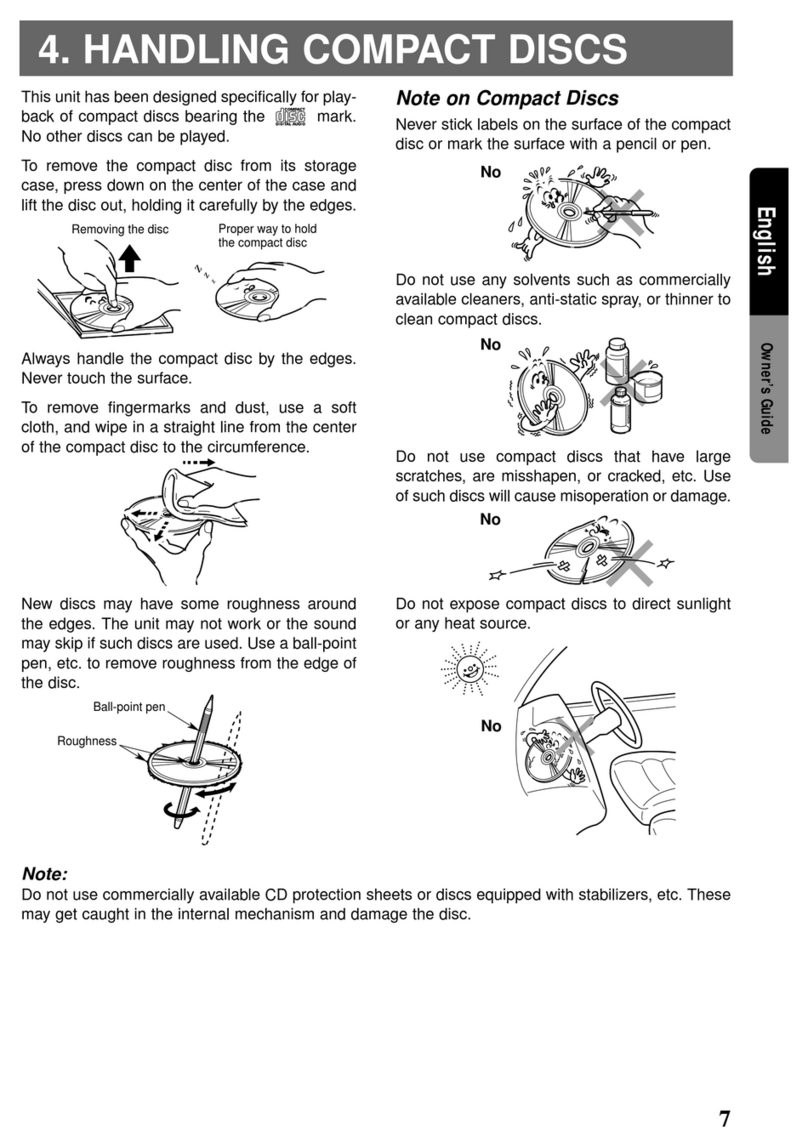

3.3 HANDLING ESD-SENSITIVE COMPONENTS

3.3.1 Personal safety

The testing, handling and replacing

of

ESD-sensitve

components requires special attention

for

personal

safety. A person dealing with ESD-sensitive

components should, normally speaking. be connected

via a resistance to the same potential as the chassis

of

the set to protect him against direct contact with

the supply voltage.

This resistance is often applied

in

the connection lead

of

wrist wraps. If necessary, make use

of

an isolating

transformer.

3.3.2 Storage and transport

Transport and store the circuits and PCBs

in

their

original packages.

As

an

alternative to the original package one may use

a conductive material

or

special

IC

package which

short-circuits all the pins

of

the

component

with one

another. ·

Always discharge the package before opening

it

3.3.3 Testing or handling

Work on a conductive surface when testing loose

circuits and components

or

when transferring

components and circuits from one package

to

another.

Use a conductive

wrist

wrap

with lead

to

make an

electrical connection between the conductive surface

and yourself via a resistance

in

the connection lead

of

the wrist wrap.

Connect equipment and tools also with this conductive

surface.

Do not connect any signals to inputs as long

as

the

power supply

of

the set to be tested is off.

All the inputs that are not used should

be

connected

either to ground or to the supply voltage. When

testing, do not use any freon sprays

for

under-cooling

of

sensitive components.

3.3.4 Mounting ESD-sensitive components

Mount ESD-sensitive components only

after

all

other

components have been mounted.

Make sure that the components themselves, the metal

parts

of

the PCB, mounting equipment and mounting

operator are at the same potential level as the chassis

of the set.

If it is impossible to ground the PCB, the mounting

operator should pick the PCB up before bringing it

into contact with the components

to

be replaced.

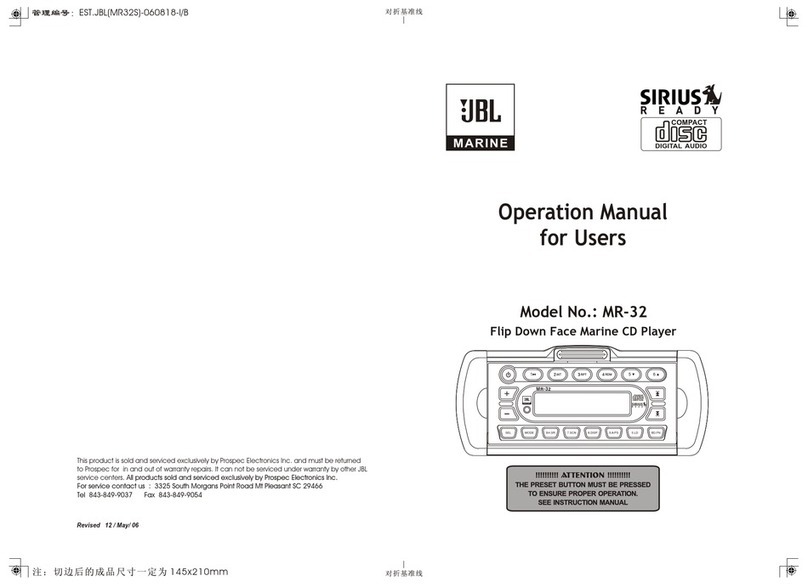

Conductive sheet

Soldering iron

Bit

3.3.5 Soldering

Soldering iron tips, also

those

of

low-voltage soldering

stations, should be

kept

at

the same potential

as

the

components

and the PCB.

It is

better

to

use solder-removing braid than solder

suckers.

3.3.6 Electrostatic charges

One should stick to the precautionary measures also

after the ESD-sensitive

components

have been

mounted on the PCB. Until the sub-PCBs have been

incorporated into a complete system on which the

correct

supply voltages are connected, the PCB is

nothing more than an extension

of

the

conductors

of

the

components

on this PCB. To prevent electrostatic

discharges from passing to the

components

via the

terminals, we recommend

that

you apply conductive

clips

or

conductive tape on the terminals

of

the PCB.

3.3.7 Transients (switch-on phenomena)

To prevent permanent

damages

as a

result

of

switch-on phenomena, no ESD-sensitive components,

or

PCBs populated with these components, should be

inserted

in

or

removed

from

test-sockets

or

systems

with the supply voltage on.

Prevent switching

peeks

on the mains as a

consequence

of

switching electric equipment, relay

and DC lines on and off.

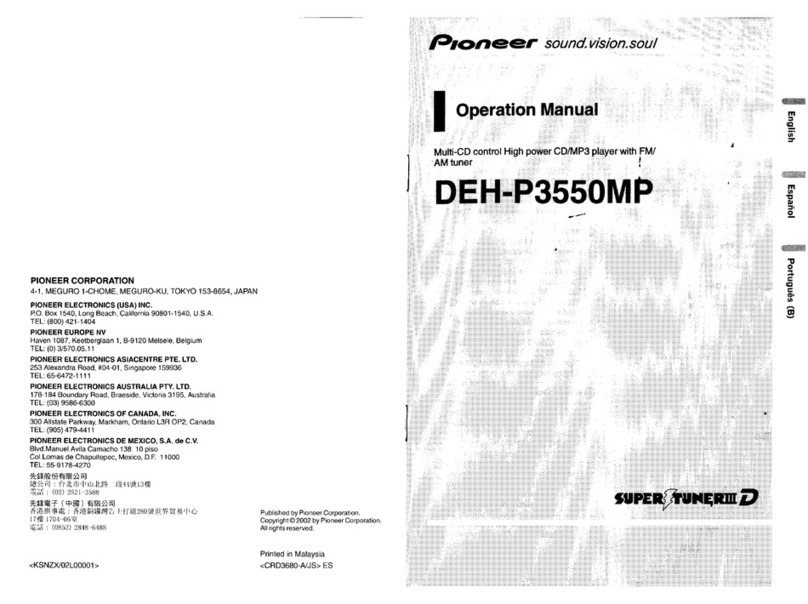

3.3.8 Working environment

The

work

bench

for

the service technician should look

like the one shown

in

the figure.

3.3.9 Replacement of the Flat Pack IC's

For replacing a

component

see Fig. 6 Dismounting

and Mounting. Also a

number

of

precautions and

examples is given.

When replacing a flat pack, rosin flux applied to the

device leads will ensure a

good

soldered joint.

Since rosin flux, when

not

properly heated by the

soldering process, is sticky, it will attract

dust

which

will result

in

component

degeneration

over

a period

of

time.

The removal

of

excess flux with a cleaner will not

solve this problem because the flux

is

then even

spread

over

a greater area by the cleaner. Drying

of

the flux can be accomplished by blowing the area with

a

common

hair dryer

for

1

or

2 minutes

at

a distance'

of

approx. 1

O

centimeters.

I•

Safety isolating transformer

Plug/socket

Wrist wrap

Special attention should be paid

in

regions having a

dry atmosphere and when the floor is covered with a

nylon carpet or such.