PDP-V402

146

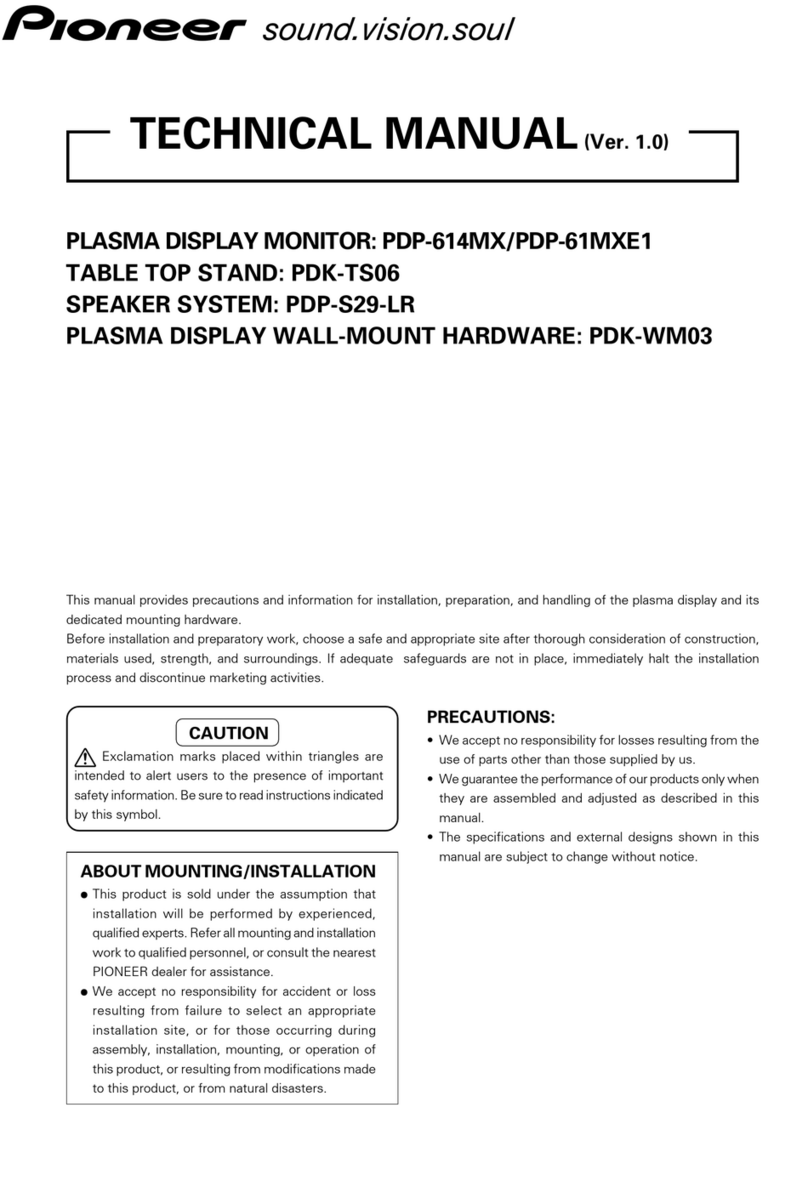

Observe Pin 7 (CBLK) of IC2801, adjust ∆tV shown in Fig. 1 to

150mS ± 20mS, and ∆tH to 1.7mS ± 200nS.

Note: When this adjustment is not performed properly, the black

level correction circuit does not operate. The 100% white

signal waveform does not fall towards the black side, and

emission points become inconsistent on the screen.

AdjustTP 7651so that theDC voltageof pointAof thewaveform

in Fig. 2 becomes 5V ± 0.1V.

Note: When this adjustment is not performed properly, the

screen flows slantingly when NTSC signals are input.

1. Connect TP K7503 to TP K7502 (GND).

2. Check the waveform of TP 7655 in Fig. 3, and adjust so that

the frequency becomes 43.0Hz ± 0.5 Hz.

3. Then disconnect the TP K7503 and TP K7502 (GND), and

check that the frequency is 52.5 Hz ± 3 Hz.

Note: When this adjustment is not performed properly, the

screen moves or flows up and down when NTSC signals

are input.

VSUS (sustain power supply voltage)

Check the drive voltage label value (Note 4), adjust VR3301 so

that value between TP3301 (VSUS) and TP3302 (SUS. GND)

becomes this value.

VADR (address power supply voltage)

Check the drive voltage label value, adjust VR3401 so that value

between TP3401 (VADR) and TP3402 (ADR. GND) becomes

this value.

VOFS (offset power supply voltage)

Check the drive voltage label value, adjust VR3601 so that value

between TP3601 (VOFS) and TP3602 (OFS. GND) becomes

this value.

Note: When the V sus voltage adjustments are not performed

properly, dot-like blinking luminance points appear. If

deviated greatly from the right adjustment, PDP will stop

discharging.

When the VADR and VOFS voltage adjustments are not

performed properly, dot-like blinking luminance points

appear. If deviated greatly from the right adjustment,

these will become white.

VR2802 (VBLK)

VR2803 (HBLK)

(ANALOG VIDEO

ASSY)

L7650

(CONTROL

ASSY)

VR7650

(CONTROL

ASSY)

VR3301

(VSUS)VR3401

(VADR)

VR3601 (VOFS)

(MAIN POWER

Assy)

Procedure

Adjustment Input Signal

Adjusting Point

Adjusting Method

Blanking pulse width

adjustment (CBLK)

VCO control voltage

adjustment

Vertical sync

freerunning

frequency

adjustment

VADR, VSUS, VOFS

voltage adjustment

100% white signal

No-input

(NO SYNC

displayed on screen)

No-input

(NO SYNC

displayed on screen)

100% white signal

1

2

3

4

150µs±20µs

tV

C BLK

V blanking

period

C BLK

H blanking

period

1.7µs±200µs

tH

5V

GND

H : 20µs/div V : 2V/div

A

Fig. 1

Fig. 2

Fig. 3

GND

H : 2ms/div V : 2V/div

ADJUSTMENTS OF PARTS