Redpine Signals, Inc. Proprietary and Confidential

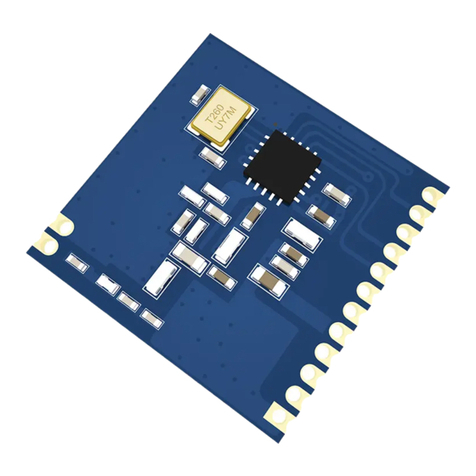

1Reference Sc ematics

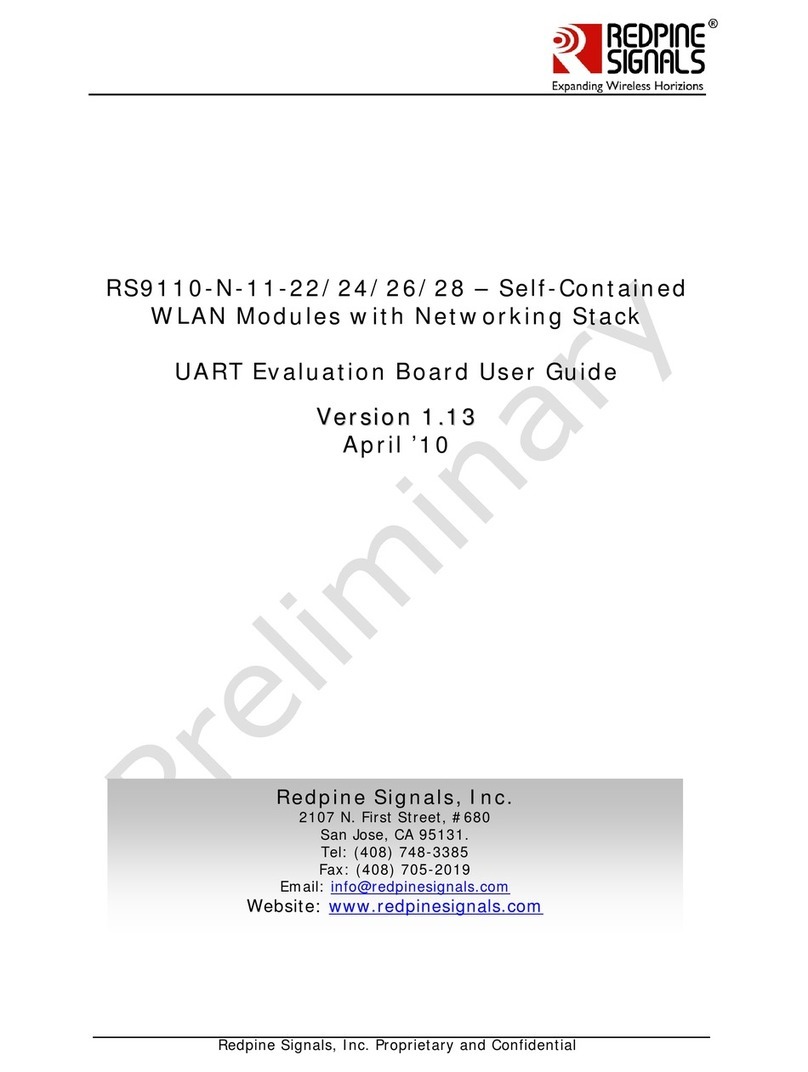

The following is a reference circuit schematic of an Evaluation Board using RS-9110-N-11-02 WLAN Module. The schematics

show both SDIO and SPI Host Interface options. The layout corresponding to this schematic is also shown in this document

as a reference

1.1 SDIO Interface

C3

0.1uF

PSPI_CSN1

PSPI_MISO

PSPI_MOSI

PSPI_CLK

Microwave switch is used for evaluating

the standalone Transmit/Receive

performance of the WLAN module by

providing direct connectivity to Signal

generator/Analyzer through RF cable

D1LED

UART2_IN

SLEE P_CLK _X1SLEE P_CLK _X1

Z1 , Z2, Z3 form the tuning network

for matching the impedance of the

Antenna. The values depend upon

the layout. In case tuning network is

not implemented Z1 should be

placed as .2pF as default

XTAL_EN

Redpine Signals Confidential

C11

0.1uF

11

2

2

FB4

BEAD

VDD_EXT

C6

1uF

VRF33

11

2

2

FB2

BEAD PSPI_MISO

GPIO_0

BT_PRIORITY

PSPI_MOSI

VIN33

SPI Serial Flash

NOTE::If required C7 can be increased to

22uF for furt er improving t e Transmit

EVM

WLAN_ACTIVE

BT_ACTIVE

PSPI_CLK

CE#

1SCK

6SI

5SO

2

VDD 8

HOLD 7

WP# 3

VSS 4

U3

SST25VF016B-75-4I-QAF-T

L1

4.7uH

VDD_EXT

C14

10uF

PSPI_CSN1

VDD_EXT

OPTIONAL

SDIO_DATA0

DVDD33

VMOD

SDIO_CMD

SDIO_CLK

SDIO_DATA3

C8

0.1uF

SDIO_DATA2

SDIO_DATA1

VRF33

Power Supply Filter Section

C10

0.1uF

Tantalum

R8

4.7K

Tantalum

11

2

2

FB3

BEAD

11

2

2

FB5

BEAD

Mating Connector Part No::MXHS83QH3000

C13

0.1uF

ANT1 1

ANT2

2

ANT1

ANT-2.45G

I2C_SDA

ANTIN 3

ANTOUT

4

GND

1GND

2

GND

5GND

6

J2

MM8430-2610RA1

C5

8.2pF

I2C_SCL

R3 820E

CLK_REF

UART1_RTS

UART1_CTS

XTAL_IP_EN

GPIO_1

RESET_n

HOST_WAKEUP_INT

UART1_OUT

UART1_IN

UART2_OUT

VMOD

C4

10uF

802.11bgn WLAN Module

C12

22uF(CASE B)

VDD_EXT

C7

10uF(CASE B)

RESET_n

C9

0.1uF

VIN33

RESET Circuitry

R7 100K

CLK_REF

Make:: TXC

OE 1

GND

2

OUT

3VDD 4

U1

7C40000192

C1

2.2uF

XTAL_ENXTAL_ENXTAL_ENXTAL_EN

R1 33E

VRF28

11

2

2

FB1

BEAD

Reference Clock Circuitry

TP1

Place Z1-Z3 Close

together and near to

ANT1

SDIO_CLK

SDIO_DATA1

SDIO_DATA3

SDIO_DATA0

CD/DAT3

1CMD 2

VSS1

3VDD 4

CLK

5VSS2 6

DAT0

7DAT1 8

DAT2

9

J1

SDIO Interface Connector

SDIO_DATA2

SDIO_CMD

VIN33

C2

10uF

R25**

SLEE P_CLK _X2

R25** v alueshould be adjustedbased

on driver output impedanceand PCB

TraceImpedance,,(33E isNominal)

TDO

R61K

Z1

TBD

Z3

TBD DVDD33

Z2

TBD

Title

Size DocumentNumber Rev

Date: Sheet of

<Doc>

RS9110-N-11-02 SDIO - Reference Sc ematics

Custom

2 2Tuesday, September 20,2011

R51K

50 Ohm RF li ne

CMS02D2

R41K

Note:

Microwave coaxial

connector with s witch

Rev6.1

Ver6.1

VRF28

RF Out Circuitry

AGND

56

RF_OUT

57

AGND

58

GND 25

NC

1

DVDD33 17

PSPI_CS N0 40

LED_ON 24

MODE_SEL_1

51

VRF28

52

XTAL_EN 23

REF_CLK

14

PSPI_CSN1

46

SLEE P_CLK _X1 35

SLEE P_CLK _X2 34

I2C_SCL

6

I2C_SDA

7

GND 30

GND 26

RESETn

15

NC 41

WLAN_ACTIVE 31

BT_PRIORITY 29

SLEE P_CLK _IN 32

HOST_WAKEUP_INT

53

NC 42

VRF33 43

VRF33 44

SDIO_DATA3/SD3

13

SDIO_DATA2/SP I_INTR

12

SDIO_DATA1/SP I_MISO

11

SDIO_DATA0/SP I_MOSI

10

SDIO_CMD/SPI_CS

9

SDIO_CLK/SP I_CLK

8

GPIO_1

55

GND

16

VINBCKDC 27

VINLDOP12 3 39

FBDC1P3 38

VOUTBCKDC1P 3 37

UART2_IN 36

UART1_RTS 22

UART1_CTS 21

UART1_OUT 18

UART1_IN 19

TCK

2

TDI

3

TMS

4

TDO

5

XTAL_EN_IP

54

GPIO_0 28

BT_ACTIVE 33

UART2_OUT 20

PSPI_MISO

47

GND 45

MODE_SEL_0

50

PSPI_CLK

49

PSPI_MOSI

48

U2

RS9110-N-11-02

Figure 1 SDIO Interface Integration

NOTE: Pull up resistors should be present on SDIO CMD & SDIO Data lines according to the section 6.6.5 of SD physical layer

specification, version 2.00