Redpine Signals, Inc. Proprietary and Confidential Page 4

M

Mo

od

du

ul

le

e

I

In

nt

te

eg

gr

ra

at

ti

io

on

n

G

Gu

ui

id

de

e

V

Ve

er

rs

si

io

on

n

2

2.

.2

2

Table Of Contents

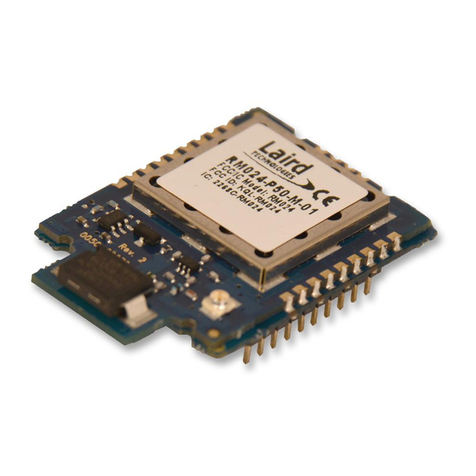

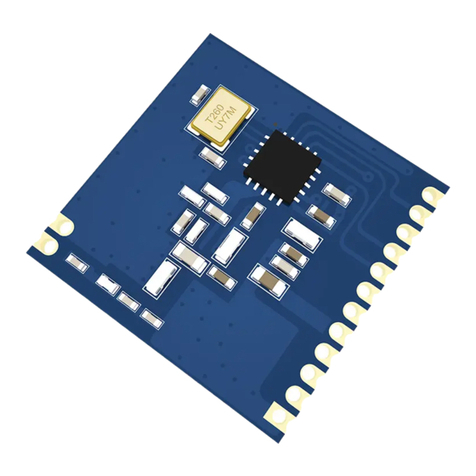

1RS9113 module with integrated antenna...................... 7

1.1 System Block Diagram .................................................. 7

1.2 Reference Schematics and BOM .................................... 8

1.2.1 SDIO mode Interface Schematic (Input supply –1.8V) ............... 9

1.2.1.1 Bill of Materials for SDIO mode (Input supply –1.8V).......... 10

1.2.2 SDIO mode Interface Schematic (Input supply –3.3V) ............. 12

1.2.2.1 Bill of Materials for SDIO mode (Input supply –3.3V).......... 13

1.2.3 SPI mode Interface Schematic ............................................... 15

1.2.3.1 Bill of Materials for SPI mode............................................ 17

1.2.4 USB mode Interface Schematic .............................................. 19

1.2.4.1 Bill of Materials for USB mode........................................... 20

1.2.5 USB CDC mode Interface Schematic ....................................... 22

1.2.5.1 Bill of Materials for USB CDC mode.................................... 23

1.2.6 UART mode Interface Schematic............................................. 25

1.2.6.1 Bill of Materials for UART Mode ......................................... 26

1.3 Recommended PCB Landing Pattern ........................... 28

1.4 Circuit and Layout Guidelines ..................................... 29

1.5 Sample Layout in SDIO mode...................................... 30

1.5.1 Top Layer ............................................................................ 30

1.5.2 Bottom Layer ....................................................................... 31

1.5.3 Component Placement .......................................................... 32

1.6 u.FL Connector for External Antenna ......................... 33

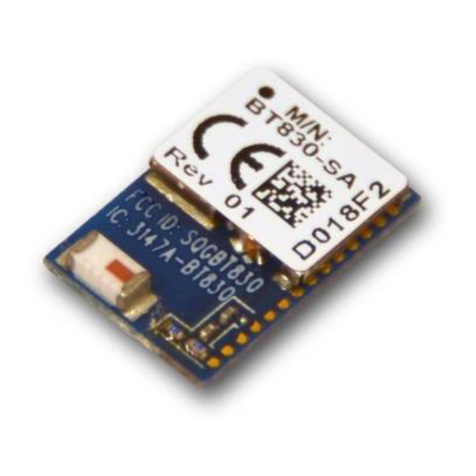

2RS9113 module without integrated antenna............... 35

2.1 System Block Diagram ................................................ 35

2.2 Reference Schematics and BOM .................................. 36

2.2.1 SDIO mode Interface Schematic (Input supply –1.8V) ............. 37

2.2.1.1 Bill of Materials for SDIO mode (Input supply –1.8V).......... 38

2.2.2 SDIO mode Interface Schematic (Input supply –3.3V) ............. 40

2.2.2.1 Bill of Materials for SDIO mode (Input supply –3.3V).......... 41

2.2.3 SPI mode Interface Schematic ............................................... 43

2.2.3.1 Bill of Materials for SPI mode............................................ 44

2.2.4 USB mode Interface Schematic .............................................. 46

2.2.4.1 Bill of Materials for USB mode........................................... 47

2.2.5 USB CDC mode Interface Schematic ....................................... 49

2.2.5.1 Bill of Materials for USB CDC mode.................................... 50

2.2.6 UART mode Interface Schematic............................................. 52

2.2.6.1 Bill of Materials in UART Mode .......................................... 53

2.3 Recommended PCB Landing Pattern ........................... 55

2.4 Circuit and Layout Guidelines ..................................... 56

2.5 Antenna Layout Recommendations............................. 56

2.6 Sample layout in SDIO mode ...................................... 58

2.6.1 Top Layer ............................................................................ 58

2.6.2 Layer2 ................................................................................ 58

2.6.3 Layer3 ................................................................................ 59

2.6.4 Bottom Layer ....................................................................... 59

2.6.5 Component Placement .......................................................... 60