IEMAN000001

R003

2 of 22

CAN Interface pHAT User Manual

01/06/2018 2 of 22

Contents

1 Introduction...................................................................................................................... 3

1.1

What is the purpose of this document ........................................................................................... 3

1.2

Who should read this document.................................................................................................... 3

1.3

How is this document organised ................................................................................................... 3

1.4

How do you receive more information........................................................................................... 4

1.5

Document Revision history............................................................................................................ 4

1.6

Supporting documents................................................................................................................... 4

1.6.1

External publications............................................................................................................. 4

1.7

Trademarks ................................................................................................................................... 4

2 Hazards, Warnings and Conformance............................................................................ 5

2.1

Hazardous Voltages ...................................................................................................................... 5

2.2

ESD Precautions ........................................................................................................................... 5

2.3

RoHS ............................................................................................................................................. 5

2.4

CE Marking.................................................................................................................................... 5

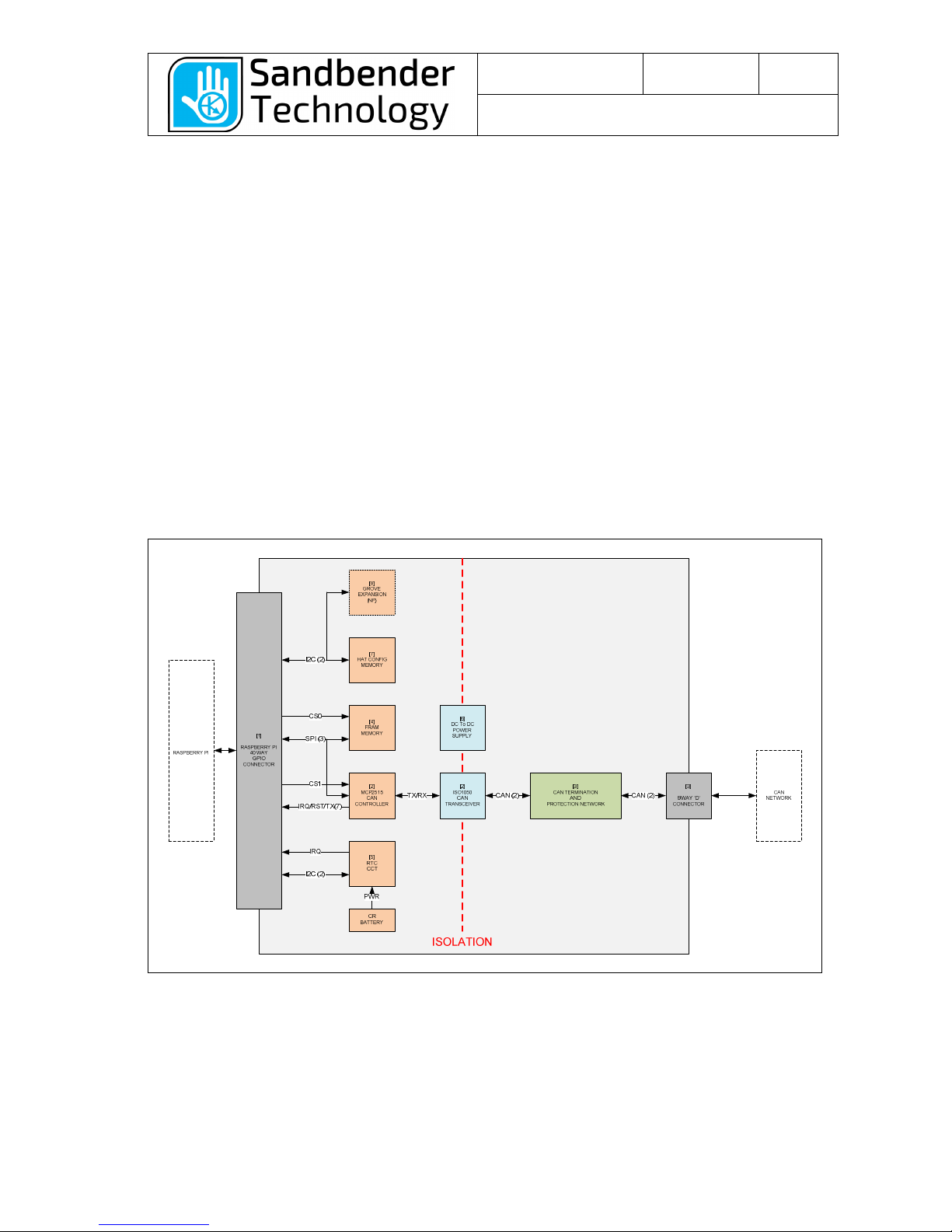

3 Functional Description .................................................................................................... 6

3.1

Overview........................................................................................................................................ 6

3.2

Functional Groups ......................................................................................................................... 7

3.2.1

HAT 40 WAY GPIO CONNECTOR ...................................................................................... 7

3.2.2

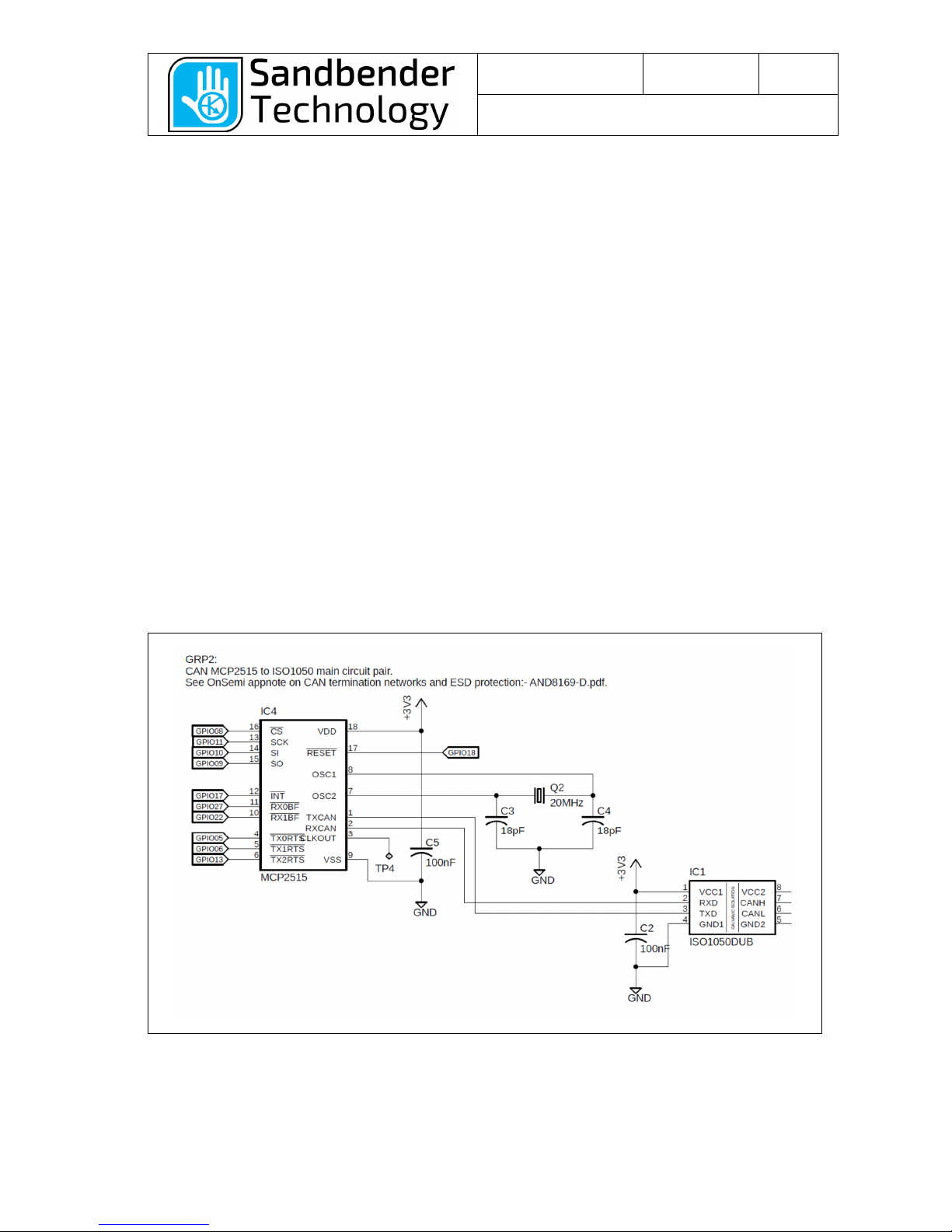

CAN Controller and Transceiver........................................................................................... 8

3.2.3

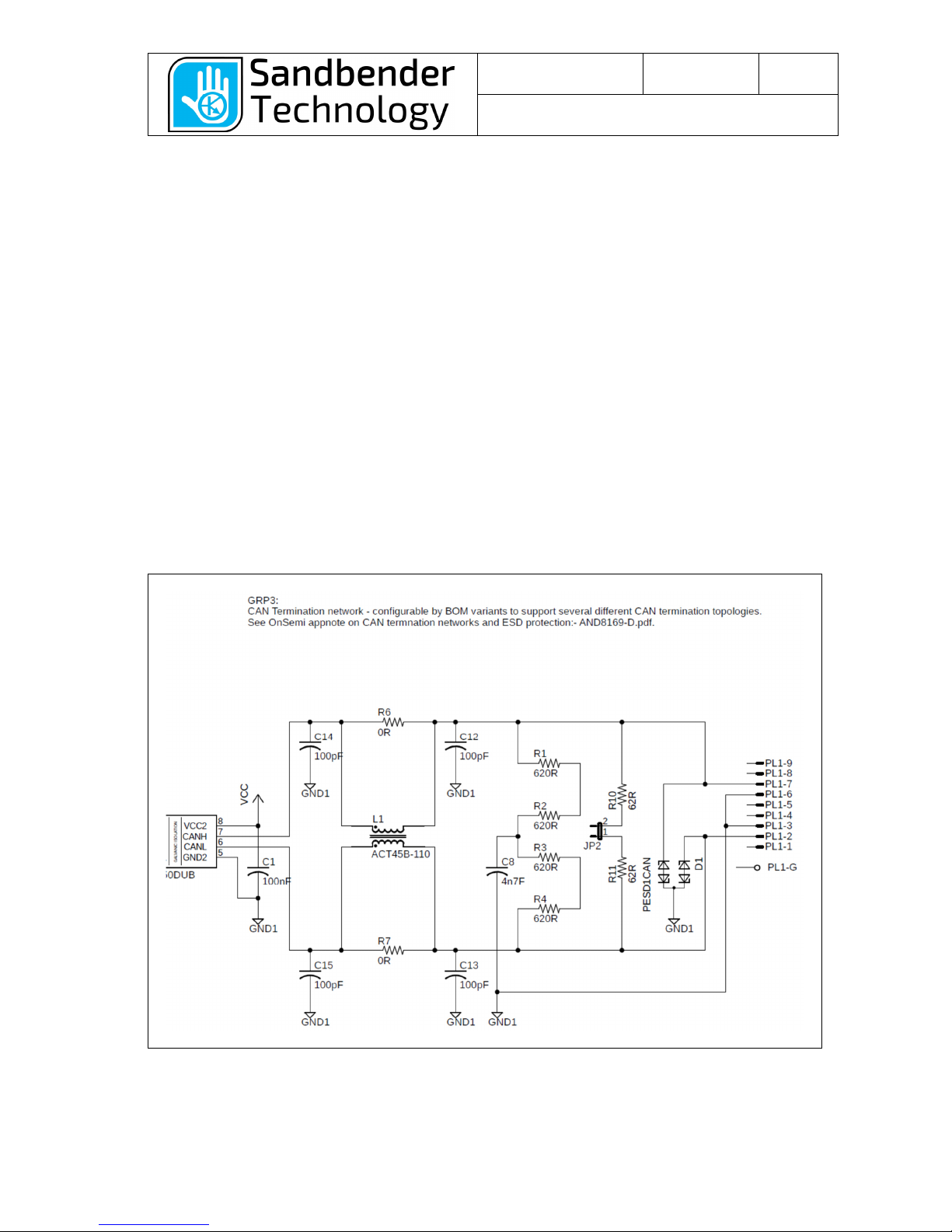

CAN Termination and Connector........................................................................................ 10

3.2.4

FRAM EEPROM ................................................................................................................. 11

3.2.5

RTC and Battery ................................................................................................................. 12

3.2.6

DC to DC Converter............................................................................................................ 13

3.2.7

HAT Configuration EEPROM.............................................................................................. 14

3.2.8

Grove Connector ................................................................................................................ 15

3.2.9

Board Mounting Hardware.................................................................................................. 16

4 Application Use.............................................................................................................. 17

4.1

Dimensions and mounting........................................................................................................... 17

4.1.1

Isolation Barrier................................................................................................................... 17

4.2

RTC Battery G1 ........................................................................................................................... 18

4.2.1

Safe Battery Cell Disposal and Handling............................................................................ 19

4.3

EEPROM Memory Protection Jumper JP1 ................................................................................. 20

4.4

CAN Bus Connection PL1 ........................................................................................................... 21

4.5

CAN Termination Jumper JP2..................................................................................................... 22