Seiko Epson S1C17 Series User manual

CMOS 16-BIT SINGLE CHIP MICROCOMPUTER

S1C17 Core Manual

S1C17 Family

NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission

of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not

assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or

use in any product or circuit and, further, there is no representation that this material is applicable to products requir-

ing high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by

implication or otherwise, and there is no representation or warranty that anything made in accordance with this mate-

rial will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain

technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade

Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval

from another government agency.

© SEIKO EPSON CORPORATION 2007, All rights reserved.

Devices

S1 C 17xxx F 00E1

Packing specifications

00 : Besides tape & reel

0A : TCP BL 2 directions

0B : Tape & reel BACK

0C : TCP BR 2 directions

0D : TCP BT 2 directions

0E : TCP BD 2 directions

0F : Tape & reel FRONT

0G: TCP BT 4 directions

0H : TCP BD 4 directions

0J : TCP SL 2 directions

0K : TCP SR 2 directions

0L : Tape & reel LEFT

0M: TCP ST 2 directions

0N : TCP SD 2 directions

0P : TCP ST 4 directions

0Q: TCP SD 4 directions

0R : Tape & reel RIGHT

99 : Specs not fixed

Specification

Package

D: die form; F: QFP, B: BGA

Model number

Model name

C: microcomputer, digital products

Product classification

S1: semiconductor

Development tools

S5U1 C 17000 H2 1

Packing specifications

00: standard packing

Version

1: Version 1

Tool type

Hx : ICE

Dx : Evaluation board

Ex : ROM emulation board

Mx: Emulation memory for external ROM

Tx : A socket for mounting

Cx : Compiler package

Sx : Middleware package

Corresponding model number

17xxx: for S1C17xxx

Tool classification

C: microcomputer use

Product classification

S5U1: development tool for semiconductor products

00

00

Configuration of product number

CONTENTS

S1C17 FAMILY S1C17 CORE MANUAL EPSON i

– Contents –

1 Summary .......................................................................................................................1-1

1.1 Features ...........................................................................................................................1-1

2 Registers .......................................................................................................................2-1

2.1 General-Purpose Registers (R0–R7) ...............................................................................2-1

2.2 Program Counter (PC) .....................................................................................................2-1

2.3 Processor Status Register (PSR) .....................................................................................2-2

2.4 Stack Pointer (SP) ............................................................................................................2-4

2.4.1 About the Stack Area .........................................................................................2-4

2.4.2 SP Operation at Subroutine Call/Return ............................................................2-4

2.4.3 SP Operation when an Interrupt Occurs ............................................................2-5

2.4.4 Saving/Restoring Register Data Using a Load Instruction ................................2-6

2.5 Register Notation and Register Numbers ........................................................................2-7

2.5.1 General-Purpose Registers ...............................................................................2-7

2.5.2 Special Registers ...............................................................................................2-7

3 Data Formats .................................................................................................................3-1

3.1 Data Formats Handled in Operations Between Registers ...............................................3-1

3.1.1 Unsigned 8-Bit Transfer (Register → Register) ..................................................3-1

3.1.2 Signed 8-Bit Transfer (Register → Register) ......................................................3-1

3.1.3 16-Bit Transfer (Register → Register) ................................................................3-2

3.1.4 24-Bit Transfer (Register → Register) ................................................................3-2

3.2 Data Formats Handled in Operations Between Memory and a Register .........................3-2

3.2.1 Unsigned 8-Bit Transfer (Memory → Register) ..................................................3-3

3.2.2 Signed 8-Bit Transfer (Memory → Register) ......................................................3-3

3.2.3 8-Bit Transfer (Register → Memory) ..................................................................3-3

3.2.4 16-Bit Transfer (Memory → Register) ................................................................3-3

3.2.5 16-Bit Transfer (Register → Memory) ................................................................3-4

3.2.6 32-Bit Transfer (Memory → Register) ................................................................3-4

3.2.7 32-Bit Transfer (Register → Memory) ................................................................3-4

4 Address Map .................................................................................................................4-1

4.1 Address Space .................................................................................................................4-1

4.2 Processor Information in the Core I/O Area ....................................................................4-2

4.2.1 Trap Table Base Register (TTBR, 0xffff80) .........................................................4-2

4.2.2 Processor ID Register (IDIR, 0xffff84) ...............................................................4-2

4.2.3 Debug RAM Base Register (DBRAM, 0xffff90) ..................................................4-2

5 Instruction Set ..............................................................................................................5-1

5.1 List of Instructions ............................................................................................................5-1

5.2 Addressing Modes (without ext extension) .....................................................................5-5

5.2.1 Immediate Addressing .......................................................................................5-5

5.2.2 Register Direct Addressing ................................................................................5-5

5.2.3 Register Indirect Addressing ..............................................................................5-6

5.2.4

Register Indirect Addressing with Post-increment/decrement or Pre-decrement ...

5-6

5.2.5 Register Indirect Addressing with Displacement ...............................................5-7

5.2.6 Signed PC Relative Addressing ........................................................................5-7

5.2.7 PC Absolute Addressing ....................................................................................5-7

CONTENTS

ii EPSON S1C17 FAMILY S1C17 CORE MANUAL

5.3 Addressing Modes with ext .............................................................................................5-8

5.3.1 Extension of Immediate Addressing ..................................................................5-8

5.3.2 Extension of Register Direct Addressing ...........................................................5-9

5.3.3 Extension of Register Indirect Addressing ........................................................5-10

5.3.4 Extension of Register Indirect Addressing with Displacement ..........................5-11

5.3.5 Extension of Signed PC Relative Addressing ...................................................5-11

5.3.6 Extension of PC Absolute Addressing ..............................................................5-12

5.4 Data Transfer Instructions ...............................................................................................5-13

5.5 Logical Operation Instructions .........................................................................................5-14

5.6 Arithmetic Operation Instructions ....................................................................................5-15

5.7 Shift and Swap Instructions .............................................................................................5-16

5.8 Branch and Delayed Branch Instructions ........................................................................5-17

5.8.1 Types of Branch Instructions .............................................................................5-17

5.8.2 Delayed Branch Instructions .............................................................................5-21

5.9 System Control Instructions ............................................................................................5-22

5.10 Conversion Instructions .................................................................................................5-23

5.11 Coprocessor Instructions ..............................................................................................5-24

6 Functions ......................................................................................................................6-1

6.1 Transition of the Processor Status ....................................................................................6-1

6.1.1 Reset State ........................................................................................................6-1

6.1.2 Program Execution State ...................................................................................6-1

6.1.3 Interrupt Handling ..............................................................................................6-1

6.1.4 Debug Interrupt ..................................................................................................6-1

6.1.5 HALT and SLEEP Modes ...................................................................................6-1

6.2 Program Execution ...........................................................................................................6-2

6.2.1 Instruction Fetch and Execution .........................................................................6-2

6.2.2 Execution Cycles and Flags ...............................................................................6-3

6.3 Interrupts ..........................................................................................................................6-6

6.3.1 Priority of Interrupts ...........................................................................................6-6

6.3.2 Vector Table ........................................................................................................6-7

6.3.3 Interrupt Handling ..............................................................................................6-7

6.3.4 Reset .................................................................................................................6-7

6.3.5 Address Misaligned Interrupt .............................................................................6-8

6.3.6 NMI ....................................................................................................................6-8

6.3.7 Maskable External Interrupts .............................................................................6-8

6.3.8 Software Interrupts ............................................................................................6-9

6.3.9 Interrupt Masked Period .....................................................................................6-9

6.4 Power-Down Mode ..........................................................................................................6-10

6.5 Debug Circuit ..................................................................................................................6-11

6.5.1 Debugging Functions ........................................................................................6-11

6.5.2 Resource Requirements and Debugging Tools .................................................6-11

6.5.3 Registers for Debugging ...................................................................................6-12

7 Details of Instructions ..................................................................................................7-1

adc %rd, %rs ............................................................................................................................. 7-2

adc/c %rd, %rs ............................................................................................................................. 7-2

adc/nc %rd, %rs ............................................................................................................................. 7-2

adc %rd, imm7 .......................................................................................................................... 7-3

add %rd, %rs ............................................................................................................................. 7-4

add/c %rd, %rs ............................................................................................................................. 7-4

add/nc %rd, %rs ............................................................................................................................. 7-4

add %rd, imm7 .......................................................................................................................... 7-5

add.a %rd, %rs ............................................................................................................................. 7-6

CONTENTS

S1C17 FAMILY S1C17 CORE MANUAL EPSON iii

add.a/c %rd, %rs ............................................................................................................................. 7-6

add.a/nc %rd, %rs ............................................................................................................................. 7-6

add.a %rd, imm7 .......................................................................................................................... 7-7

add.a %sp, %rs ............................................................................................................................ 7-8

add.a %sp, imm7 ......................................................................................................................... 7-9

and %rd, %rs ............................................................................................................................ 7-10

and/c %rd, %rs ............................................................................................................................ 7-10

and/nc %rd, %rs ............................................................................................................................ 7-10

and %rd, sign7 ......................................................................................................................... 7-11

brk ........................................................................................................................................... 7-12

call %rb .................................................................................................................................... 7-13

call.d %rb .................................................................................................................................... 7-13

call sign10 ................................................................................................................................ 7-14

call.d sign10 ................................................................................................................................ 7-14

calla %rb .................................................................................................................................... 7-15

calla.d %rb .................................................................................................................................... 7-15

calla imm7 .................................................................................................................................. 7-16

calla.d imm7 .................................................................................................................................. 7-16

cmc %rd, %rs ............................................................................................................................ 7-17

cmc/c %rd, %rs ............................................................................................................................ 7-17

cmc/nc %rd, %rs ............................................................................................................................ 7-17

cmc %rd, sign7 ......................................................................................................................... 7-18

cmp %rd, %rs ............................................................................................................................ 7-19

cmp/c %rd, %rs ............................................................................................................................ 7-19

cmp/nc %rd, %rs ............................................................................................................................ 7-19

cmp %rd, sign7 ......................................................................................................................... 7-20

cmp.a %rd, %rs ............................................................................................................................ 7-21

cmp.a/c %rd, %rs ............................................................................................................................ 7-21

cmp.a/nc %rd, %rs ............................................................................................................................ 7-21

cmp.a %rd, imm7 ......................................................................................................................... 7-22

cv.ab %rd, %rs ............................................................................................................................ 7-23

cv.al %rd, %rs ............................................................................................................................ 7-24

cv.as %rd, %rs ............................................................................................................................ 7-25

cv.la %rd, %rs ............................................................................................................................ 7-26

cv.ls %rd, %rs ............................................................................................................................ 7-27

di ........................................................................................................................................... 7-28

ei ........................................................................................................................................... 7-29

ext imm13 ................................................................................................................................ 7-30

halt ........................................................................................................................................... 7-31

int imm5 .................................................................................................................................. 7-32

intl imm5, imm3 ...................................................................................................................... 7-33

jpa %rb .................................................................................................................................... 7-34

jpa.d %rb .................................................................................................................................... 7-34

jpa imm7 .................................................................................................................................. 7-35

jpa.d imm7 .................................................................................................................................. 7-35

jpr %rb .................................................................................................................................... 7-36

jpr.d %rb .................................................................................................................................... 7-36

jpr sign10 ................................................................................................................................ 7-37

jpr.d sign10 ................................................................................................................................ 7-37

jreq sign7 .................................................................................................................................. 7-38

jreq.d sign7 .................................................................................................................................. 7-38

jrge sign7 .................................................................................................................................. 7-39

jrge.d sign7 .................................................................................................................................. 7-39

jrgt sign7 .................................................................................................................................. 7-40

jrgt.d sign7 .................................................................................................................................. 7-40

jrle sign7 .................................................................................................................................. 7-41

jrle.d sign7 .................................................................................................................................. 7-41

jrlt sign7 .................................................................................................................................. 7-42

CONTENTS

iv EPSON S1C17 FAMILY S1C17 CORE MANUAL

jrlt.d sign7 .................................................................................................................................. 7-42

jrne sign7 .................................................................................................................................. 7-43

jrne.d sign7 .................................................................................................................................. 7-43

jruge sign7 .................................................................................................................................. 7-44

jruge.d sign7 .................................................................................................................................. 7-44

jrugt sign7 .................................................................................................................................. 7-45

jrugt.d sign7 .................................................................................................................................. 7-45

jrule sign7 .................................................................................................................................. 7-46

jrule.d sign7 .................................................................................................................................. 7-46

jrult sign7 .................................................................................................................................. 7-47

jrult.d sign7 .................................................................................................................................. 7-47

ld %rd, %rs ............................................................................................................................ 7-48

ld %rd, [%rb] ......................................................................................................................... 7-49

ld %rd, [%rb]+ ....................................................................................................................... 7-49

ld %rd, [%rb]- ........................................................................................................................ 7-49

ld %rd, -[%rb] ........................................................................................................................ 7-49

ld %rd, [%sp + imm7] ........................................................................................................... 7-51

ld %rd, [imm7] ....................................................................................................................... 7-52

ld %rd, sign7 ......................................................................................................................... 7-53

ld [%rb], %rs ......................................................................................................................... 7-54

ld [%rb]+, %rs ....................................................................................................................... 7-54

ld [%rb]-, %rs ........................................................................................................................ 7-54

ld -[%rb], %rs ........................................................................................................................ 7-54

ld [%sp + imm7], %rs ........................................................................................................... 7-56

ld [imm7], %rs ....................................................................................................................... 7-57

ld.a %rd, %pc ........................................................................................................................... 7-58

ld.a %rd, %rs ............................................................................................................................ 7-59

ld.a %rd, %sp ........................................................................................................................... 7-60

ld.a %rd, [%rb] ......................................................................................................................... 7-61

ld.a %rd, [%rb]+ ....................................................................................................................... 7-61

ld.a %rd, [%rb]- ........................................................................................................................ 7-61

ld.a %rd, -[%rb] ........................................................................................................................ 7-61

ld.a %rd, [%sp] ......................................................................................................................... 7-63

ld.a %rd, [%sp]+ ....................................................................................................................... 7-63

ld.a %rd, [%sp]- ........................................................................................................................ 7-63

ld.a %rd, -[%sp] ........................................................................................................................ 7-63

ld.a %rd, [%sp + imm7] ........................................................................................................... 7-65

ld.a %rd, [imm7] ....................................................................................................................... 7-66

ld.a %rd, imm7 ......................................................................................................................... 7-67

ld.a %sp, %rs ........................................................................................................................... 7-68

ld.a %sp, imm7 ........................................................................................................................ 7-69

ld.a [%rb], %rs ......................................................................................................................... 7-70

ld.a [%rb]+, %rs ....................................................................................................................... 7-70

ld.a [%rb]-, %rs ........................................................................................................................ 7-70

ld.a -[%rb], %rs ........................................................................................................................ 7-70

ld.a [%sp], %rs ......................................................................................................................... 7-72

ld.a [%sp]+, %rs ....................................................................................................................... 7-72

ld.a [%sp]-, %rs ........................................................................................................................ 7-72

ld.a -[%sp], %rs ........................................................................................................................ 7-72

ld.a [%sp + imm7], %rs ........................................................................................................... 7-74

ld.a [imm7], %rs ....................................................................................................................... 7-75

ld.b %rd, %rs ............................................................................................................................ 7-76

ld.b %rd, [%rb] ......................................................................................................................... 7-77

ld.b %rd, [%rb]+ ....................................................................................................................... 7-77

ld.b %rd, [%rb]- ........................................................................................................................ 7-77

ld.b %rd, -[%rb] ........................................................................................................................ 7-77

ld.b %rd, [%sp + imm7] ........................................................................................................... 7-79

ld.b %rd, [imm7] ....................................................................................................................... 7-80

ld.b [%rb], %rs ......................................................................................................................... 7-81

CONTENTS

S1C17 FAMILY S1C17 CORE MANUAL EPSON v

ld.b [%rb]+, %rs ....................................................................................................................... 7-81

ld.b [%rb]-, %rs ........................................................................................................................ 7-81

ld.b -[%rb], %rs ........................................................................................................................ 7-81

ld.b [%sp + imm7], %rs ........................................................................................................... 7-83

ld.b [imm7], %rs ....................................................................................................................... 7-84

ld.ca %rd, %rs ............................................................................................................................ 7-85

ld.ca %rd, imm7 ......................................................................................................................... 7-86

ld.cf %rd, %rs ............................................................................................................................ 7-87

ld.cf %rd, imm7 ......................................................................................................................... 7-88

ld.cw %rd, %rs ............................................................................................................................ 7-89

ld.cw %rd, imm7 ......................................................................................................................... 7-90

ld.ub %rd, %rs ............................................................................................................................ 7-91

ld.ub %rd, [%rb] ......................................................................................................................... 7-92

ld.ub %rd, [%rb]+ ....................................................................................................................... 7-92

ld.ub %rd, [%rb]- ........................................................................................................................ 7-92

ld.ub %rd, -[%rb] ........................................................................................................................ 7-92

ld.ub %rd, [%sp + imm7] ........................................................................................................... 7-94

ld.ub %rd, [imm7] ....................................................................................................................... 7-95

nop ........................................................................................................................................... 7-96

not %rd, %rs ............................................................................................................................ 7-97

not/c %rd, %rs ............................................................................................................................ 7-97

not/nc %rd, %rs ............................................................................................................................ 7-97

not %rd, sign7 ......................................................................................................................... 7-98

or %rd, %rs ............................................................................................................................ 7-99

or/c %rd, %rs ............................................................................................................................ 7-99

or/nc %rd, %rs ............................................................................................................................ 7-99

or %rd, sign7 ........................................................................................................................ 7-100

ret .......................................................................................................................................... 7-101

ret.d .......................................................................................................................................... 7-101

retd .......................................................................................................................................... 7-102

reti .......................................................................................................................................... 7-103

reti.d .......................................................................................................................................... 7-103

sa %rd, %rs ........................................................................................................................... 7-104

sa %rd, imm7 ........................................................................................................................ 7-105

sbc %rd, %rs ........................................................................................................................... 7-106

sbc/c %rd, %rs ........................................................................................................................... 7-106

sbc/nc %rd, %rs ........................................................................................................................... 7-106

sbc %rd, imm7 ........................................................................................................................ 7-107

sl %rd, %rs ........................................................................................................................... 7-108

sl %rd, imm7 ........................................................................................................................ 7-109

slp .......................................................................................................................................... 7-110

sr %rd, %rs ........................................................................................................................... 7-111

sr %rd, imm7 ........................................................................................................................ 7-112

sub %rd, %rs ........................................................................................................................... 7-113

sub/c %rd, %rs ........................................................................................................................... 7-113

sub/nc %rd, %rs ........................................................................................................................... 7-113

sub %rd, imm7 ........................................................................................................................ 7-114

sub.a %rd, %rs ........................................................................................................................... 7-115

sub.a/c %rd, %rs ........................................................................................................................... 7-115

sub.a/nc %rd, %rs ........................................................................................................................... 7-115

sub.a %rd, imm7 ........................................................................................................................ 7-116

sub.a %sp, %rs .......................................................................................................................... 7-117

sub.a %sp, imm7 ....................................................................................................................... 7-118

swap %rd, %rs ........................................................................................................................... 7-119

xor %rd, %rs ........................................................................................................................... 7-120

xor/c %rd, %rs ........................................................................................................................... 7-120

xor/nc %rd, %rs ........................................................................................................................... 7-120

xor %rd, sign7 ........................................................................................................................ 7-121

1 SUMMARY

S1C17 FAMILY S1C17 CORE MANUAL EPSON 1-1

1 Summary

The S1C17 Core is a Seiko Epson original 16-bit RISC-type processor.

It features low power consumption, high-speed operation with a maximum 60 MHz to 90 MHz clock, large address

space up to 16M bytes addressable, main instructions executable in one clock cycle, and a small sized design. The

S1C17 Core is suitable for embedded applications that do not need a lot of data processing power like the S1C33

Cores the high-end processors, such as controllers and sequencers for which an eight-bit CPU is commonly used.

The S1C17 Core incorporates a coprocessor interface allowing implementation of additional computing features.

Furthermore, Seiko Epson provides a software development environment similar to the S1C33 Family that includes

an IDE work bench, a C compiler, a serial ICE and a debugger, for supporting the developer to develop application

software.

1.1 Features

Processor type

• Seiko Epson original 16-bit RISC processor

• 0.35–0.15 µm low power CMOS process technology

Operating-clock frequency

• 90 MHz maximum (depending on the processor model and process technology)

Instruction set

• Code length: 16-bit fixed length

• Number of instructions: 111 basic instructions (184 including variations)

• Execution cycle: Main instructions executed in one cycles

• Extended immediate instructions: Immediate extended up to 24 bits

• Compact and fast instruction set optimized for development in C language

Register set

• Eight 24-bit general-purpose registers

• Two 24-bit special registers

• One 8-bit special register

Memory space and bus

• Up to 16M bytes of memory space (24-bit address)

• Harvard architecture using separated instruction bus (16 bits) and data bus (32 bits)

Interrupts

• Reset, NMI, and 32 external interrupts supported

• Address misaligned interrupt

• Debug interrupt

• Direct branching from vector table to interrupt handler routine

• Programmable software interrupts with a vector number specified (all vector numbers specifiable)

Power saving

• HALT (halt instruction)

• SLEEP (slp instruction)

Coprocessor interface

• ALU instructions can be enhanced

1 SUMMARY

1-2 EPSON S1C17 FAMILY S1C17 CORE MANUAL

THIS PAGE IS BLANK.

2 REGISTERS

S1C17 FAMILY S1C17 CORE MANUAL EPSON 2-1

2 Registers

The S1C17 Core contains eight general-purpose registers and three special registers.

R4

R5

R6

R7

R3

R2

R1

R0

bit 23 bit 0

General-purpose registers

PC

bit 23

7

6

5

4

3

2

1

0

bit 0

PSR

SP

Special registers

IL[2:0]

765

IE

4

C

3

V

2

Z

1

N

0

Figure 2.1 Registers

2.1 General-Purpose Registers (R0–R7)

Symbol

R0–R7

Size

24 bits

Initial value

0x000000 or indeterminate

Register name

General-Purpose Register

R/W

R/W

The eight registers R0–R7 (r0–r7) are 24-bit general-purpose registers that can be used for data manipulation, data

transfer, memory addressing, or other general purposes. The contents of all of these registers are handled as 24-bit

data or addresses. 8- or 16-bit data can be sign- or zero-extended to a 24-bit quantity when it is loaded into one of

these registers using a load instruction or a conversion instruction. When these registers are used for address refer-

ences, 24-bit memory space can be accessed directly.

At initial reset, the contents of the general-purpose registers are set to 0 (may be indeterminate without initialization

depending on the configuration).

2.2 Program Counter (PC)

Symbol

PC

Size

24 bits

Initial value

(Reset vector)

Register name

Program Counter

R/W

R

The Program Counter (hereinafter referred to as the “PC”) is a 24-bit counter for holding the address of an instruc-

tion to be executed. More specifically, the PC value indicates the address of the next instruction to be executed.

As the instructions in the S1C17 Core are fixed at 16 bits in length, the LSB (bit 0) of the PC is always 0.

Although the S1C17 Core allows the PC to be referenced in a program, the user cannot alter it. Note, however, that

the value actually loaded into the register when a ld.a %rd,%pc instruction (can be executed as a delayed in-

struction) is executed is the “PC value for the ld instruction + 2.”

At an initial reset, the reset vector (address) written at the top of vector table indicated by TTBR is loaded into the

PC, and the processor starts executing a program from the address indicated by the PC.

Effective address 0

0123

Figure 2.2.1 Program Counter (PC)

2 REGISTERS

2-2 EPSON S1C17 FAMILY S1C17 CORE MANUAL

2.3 Processor Status Register (PSR)

Symbol

PSR

Size

8 bits

Initial value

0x00

Register name

Processor Status Register

R/W

R/W

The Processor Status Register (hereinafter referred to as the “PSR”) is an 8-bit register for storing the internal status

of the processor.

The PSR stores the internal status of the processor when the status has been changed by instruction execution. It is

referenced in arithmetic operations or branch instructions, and therefore constitutes an important internal status in

program composition. The PSR does not allow the program to directly alter its contents except for the IE bit.

As the PSR affects program execution, whenever an interrupt occurs, the PSR is saved to the stack, except for de-

bug interrupts, to maintain the PSR value. The IE flag (bit 4) in it is cleared to 0. The reti instruction is used to

return from interrupt handling, and the PSR value is restored from the stack at the same time.

IL[2:0]

765

IE

4

C

3

V

2

Z

1

N

0

0 0 0 0 0 0 0 0Initial value

PSR

Figure 2.3.1 Processor Status Register (PSR)

IL[2:0] (bits 7–5): Interrupt Level

These bits indicate the priority levels of the processor interrupts. Maskable interrupt requests are accepted only

when their priority levels are higher than that set in the IL bit field. When an interrupt request is accepted, the

IL bit field is set to the priority level of that interrupt, and all interrupt requests generated thereafter with the

same or lower priority levels are masked, unless the IL bit field is set to a different level or the interrupt handler

routine is terminated by the reti instruction.

IE (bit 4): Interrupt Enable

This bit controls maskable external interrupts by accepting or disabling them. When IE bit = 1, the processor

enables maskable external interrupts. When IE bit = 0, the processor disables maskable external interrupts.

When an interrupt is accepted, the PSR is saved to the stack and this bit is cleared to 0. However, the PSR is not

saved to the stack for debug interrupts, nor is this bit cleared to 0.

C (bit 3): Carry

This bit indicates a carry or borrow. More specifically, this bit is set to 1 when, in an add or subtract instruction

in which the result of operation is handled as an unsigned 16-bit integer, the execution of the instruction result-

ed in exceeding the range of values representable by an unsigned 16-bit integer, or is reset to 0 when the result

is within the range of said values.

The C flag is set under the following conditions:

(1) When an addition executed by an add instruction resulted in a value greater than the maximum value 0xffff

representable by an unsigned 16-bit integer

(2) When a subtraction executed by a subtract instruction resulted in a value smaller than the minimum value

0x0000 representable by an unsigned 16-bit integer

V (bit 2): OVerflow

This bit indicates that an overflow or underflow occurred in an arithmetic operation. More specifically, this bit

is set to 1 when, in an add or subtract instruction in which the result of operation is handled as a signed 16-bit

integer, the execution of the instruction resulted in an overflow or underflow, or is reset to 0 when the result of

the add or subtract operation is within the range of values representable by a signed 16-bit integer. This flag is

also reset to 0 by executing a logical operation instruction.

2 REGISTERS

S1C17 FAMILY S1C17 CORE MANUAL EPSON 2-3

The V flag is set under the following conditions:

(1) When negative integers are added together, the operation produced a 0 (positive) in the sign bit (most sig-

nificant bit of the result)

(2) When positive integers are added together, the operation resulted in a 1 (negative) in the sign bit (most sig-

nificant bit of the result)

(3) When a negative integer is subtracted from a positive integer, the operation resulted in producing a 1 (nega-

tive) in the sign bit (most significant bit of the result)

(4) When a positive integer is subtracted from a negative integer, the operation resulted in producing a 0 (positive)

in the sign bit (most significant bit of the result)

Z (bit 1): Zero

This bit indicates that an operation resulted in 0. More specifically, this bit is set to 1 when the execution of a

logical operation, arithmetic operation, or shift instruction resulted in 0, or is otherwise reset to 0.

N (bit 0): Negative

This bit indicates a sign. More specifically, the most significant bit (bit 15) of the result of a logical operation,

arithmetic operation, or shift instruction is copied to this N flag.

2 REGISTERS

2-4 EPSON S1C17 FAMILY S1C17 CORE MANUAL

2.4 Stack Pointer (SP)

Symbol

SP

Size

24 bits

Initial value

0x000000

Register name

Stack Pointer

R/W

R/W

The Stack Pointer (hereinafter referred to as the “SP”) is a 24-bit register for holding the start address of the stack.

The stack is an area locatable at any place in the system RAM, the start address of which is set in the SP during the

initialization process. The 2 low-order bits of the SP are fixed to 0 and cannot be accessed for writing. Therefore,

the addresses specifiable by the SP are those that lie on 32-bit boundaries.

32-bit boundary address 0 0

01223

Fixed

(read only)

Figure 2.4.1 Stack Pointer (SP)

2.4.1 About the Stack Area

The size of an area usable as the stack is limited according to the RAM size available for the system and the size of

the area occupied by ordinary RAM data. Care must be taken to prevent the stack and data area from overlapping.

Furthermore, as the SP becomes 0x000000 when it is initialized upon reset, “last stack address + 4, with 2 low-

order bits = 0” must be written to the SP in the beginning part of the initialization routine. A load instruction may

be used to write this address. If an interrupt occurs before the stack is set up, it is possible that the PC or PSR will

be saved to an indeterminate location, and normal operation of a program cannot be guaranteed. To prevent such a

problem, NMIs (nonmaskable interrupts) that cannot be controlled in software are masked out in hardware until the

SP is initialized.

2.4.2 SP Operation at Subroutine Call/Return

A subroutine call instruction, call or calla, uses four bytes of the stack. The call/calla instruction saves the

contents of the PC (return address) onto the stack before branching to a subroutine. The saved address is restored

into the PC by the ret instruction, and the program is returned to the address next to that of the call/calla in-

struction.

SP operation by the call/calla instruction

(1) SP = SP - 4

(2) PC → [SP]

SP

7 0

0xffffff

0x000000

SP = SP - 4

7 0

0xffffff

0x00

PC[23:16]

PC[15:8]

PC[7:0]

0x000000

Figure 2.4.2.1 SP and Stack (1)

2 REGISTERS

S1C17 FAMILY S1C17 CORE MANUAL EPSON 2-5

SP operation by the ret instruction

(1) [SP] → PC

(2) SP = SP + 4

SP

7 0

0xffffff

0x000000

SP = SP + 4

7 0

0xffffff

0x00

PC[23:16]

0x00

PC[23:16]

PC[15:8]

PC[7:0]

PC[15:8]

PC[7:0]

0x000000

Figure 2.4.2.2 SP and Stack (2)

2.4.3 SP Operation when an Interrupt Occurs

If an interrupt or a software interrupt resulting from the int/intl instruction occurs, the processor enters an inter-

rupt handling process.

The processor saves the contents of the PC and PSR into the stack indicated by the SP before branching to the rel-

evant interrupt handler routine. This is to save the contents of the two registers before they are altered by interrupt

handling. The PC and PSR data is saved into the stack as shown in the diagram below.

For returning from the handler routine, the reti instruction is used to restore the contents of the PC and PSR from

the stack. In the reti instruction, the PC and PSR are read out of the stack, and the SP address is altered as shown

in the diagram below.

SP operation when an interrupt occurred

(1) SP = SP - 4

(2) PC → [SP]

(3) PSR → [SP + 3]

SP

7 0

0xffffff

0x000000

SP = SP - 4

7 0

0xffffff

0x00

PC[23:16]

PC[15:8]

PC[7:0]

0x000000

Figure 2.4.3.1 SP and Stack (3)

SP operation when the reti instruction is executed

(1) [SP] → PC

(2) [SP+ 3] → PSR

(3) SP = SP + 4

SP

7 0

0xffffff

0x000000

SP = SP + 4

7 0

0xffffff

PSR

PC[23:16]

PSR

PC[23:16]

PC[15:8]

PC[7:0]

PC[15:8]

PC[7:0]

0x000000

Figure 2.4.3.2 SP and Stack (4)

2 REGISTERS

2-6 EPSON S1C17 FAMILY S1C17 CORE MANUAL

2.4.4 Saving/Restoring Register Data Using a Load Instruction

The S1C17 Core provides load instructions to save and restore register data to/from the stack instead of push/pop

instructions.

Saving register data into the stack

Example: ld.a -[%sp],%r0

(1) SP = SP - 4

(2) R0 → [SP]

SP

7 0

0xffffff

0x000000

SP = SP - 4

7 0

0xffffff

0x00

R0[23:16]

R0[15:8]

R0[7:0]

0x000000

Figure 2.4.4.1 SP and Stack (5)

Restoring register data from the stack

Example: ld.a %r0,[%sp]+

(1) [SP] → R0

(2) SP = SP + 4

SP

7 0

0xffffff

0x000000

SP = SP + 4

7 0

0xffffff

0x00

R0[23:16]

0x00

R0[23:16]

R0[15:8]

R0[7:0]

R0[15:8]

R0[7:0]

0x000000

Figure 2.4.4.2 SP and Stack (6)

In addition to the instructions shown above, some other load instructions have been provided for operating the

stack. Refer to Chapter 7, “Details of Instructions,” for more information on those instructions.

2 REGISTERS

S1C17 FAMILY S1C17 CORE MANUAL EPSON 2-7

2.5 Register Notation and Register Numbers

The following describes the register notation and register numbers in the S1C17 Core instruction set.

2.5.1 General-Purpose Registers

In the instruction code, a general-purpose register is specified using a 3-bit field, with the register number entered

in that field. In the mnemonic, a register is specified by prefixing the register name with “%.”

%rs rs is a metasymbol indicating the general-purpose register that holds the source data to be operated on or

transferred. The register is actually written as %r0, %r1, ... or %r7.

%rd rd is a metasymbol indicating the general-purpose register that is the destination in which the result of op-

eration is to be stored or data is to be loaded. The register is actually written as %r0, %r1, ... or %r7.

%rb rb is a metasymbol indicating the general-purpose register that holds the base address of memory to be ac-

cessed. In this case, the general-purpose registers serve as an index register. The register is actually written

as [%r0], [%r1], ... or [%r7], with each register name enclosed in brackets “[]” to denote register indi-

rect addressing.

In register indirect addressing, the post-increment/decrement and pre-decrement functions provided for

continuous memory addresses can be used.

Post-increment function

Example: ld %rd,[%rb]+ ; (1)ld %rd,[%rb] (2)%rb = %rb + 2

The base address is incremented by an amount equal to the accessed size after the memory has been ac-

cessed.

Post-decrement function

Example: ld.a %rd,[%rb]- ; (1)ld.a %rd,[%rb] (2)%rb = %rb - 4

The base address is decremented by an amount equal to the accessed size after the memory has been ac-

cessed.

Pre-decrement function

Example: ld.b -[%rb],%rs ; (1)%rb = %rb - 1 (2)ld.b [%rb],%rs

The base address is decremented by an amount equal to the access size before accessing the memory.

Also any desired value can be specified as the address increment/decrement value using the ext instruc-

tion.

rb is also used as a symbol indicating the register that contains the jump address for the call or jump in-

structions. In this case, the brackets “[]” are unnecessary, and the register is written as %r0, %r1, ... or

%r7.

The bit field that specifies a register in the instruction code contains the code corresponding to a given register

number. The relationship between the general-purpose registers and the register numbers is listed in the table below.

Table 2.5.1.1 General-Purpose Registers

General-purpose register

R0

R1

R2

R3

R4

R5

R6

R7

Register number

0

1

2

3

4

5

6

7

Register notation

%r0

%r1

%r2

%r3

%r4

%r5

%r6

%r7

2.5.2 Special Registers

The special registers that can be directly specified in the S1C17 Core instructions are the SP (Stack Pointer)

and PC (Program Counter) only. The register is actually written as %sp, [%sp], -[%sp], [%sp]+, [%sp]-,

[%sp+imm7], or %pc.

2 REGISTERS

2-8 EPSON S1C17 FAMILY S1C17 CORE MANUAL

THIS PAGE IS BLANK.

Table of contents

Other Seiko Epson Computer Hardware manuals

Popular Computer Hardware manuals by other brands

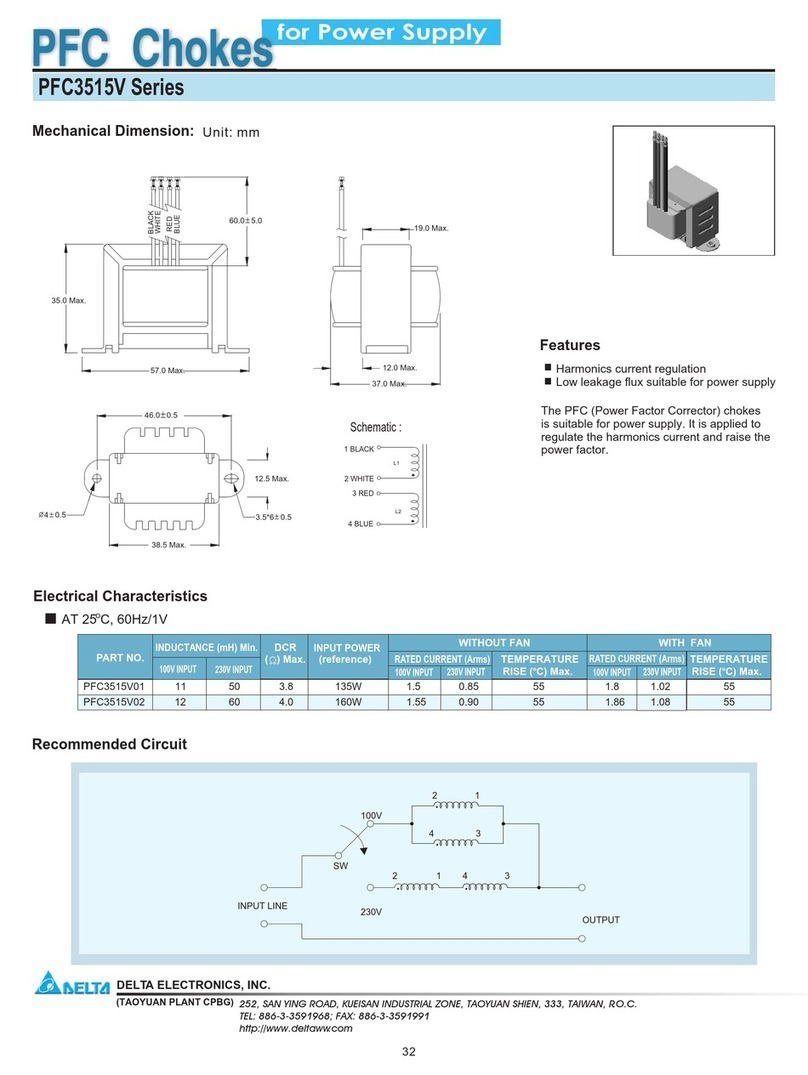

Delta Electronics

Delta Electronics PFC Chokes PFC3515V Series Specification sheet

Renesas

Renesas HSG2005 Specifications

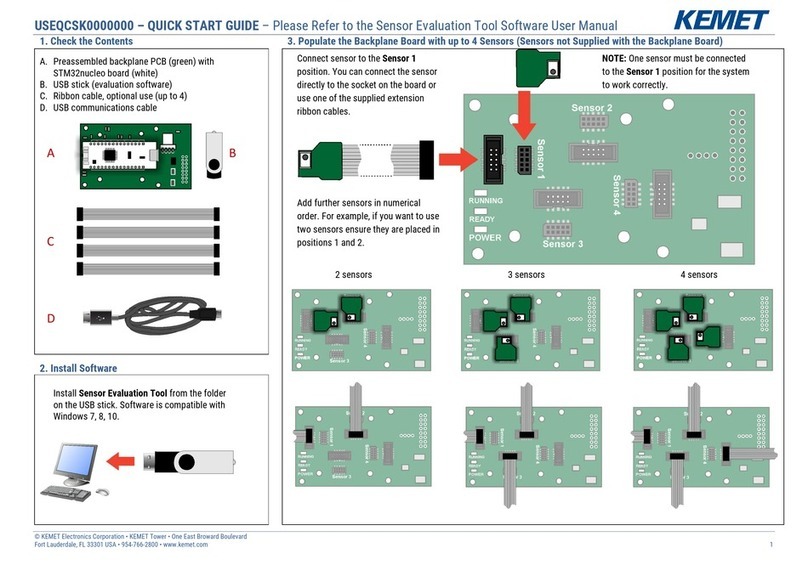

KEMET

KEMET USEQCSK0000000 quick start guide

Lattice Semiconductor

Lattice Semiconductor LatticeMico GPIO manual

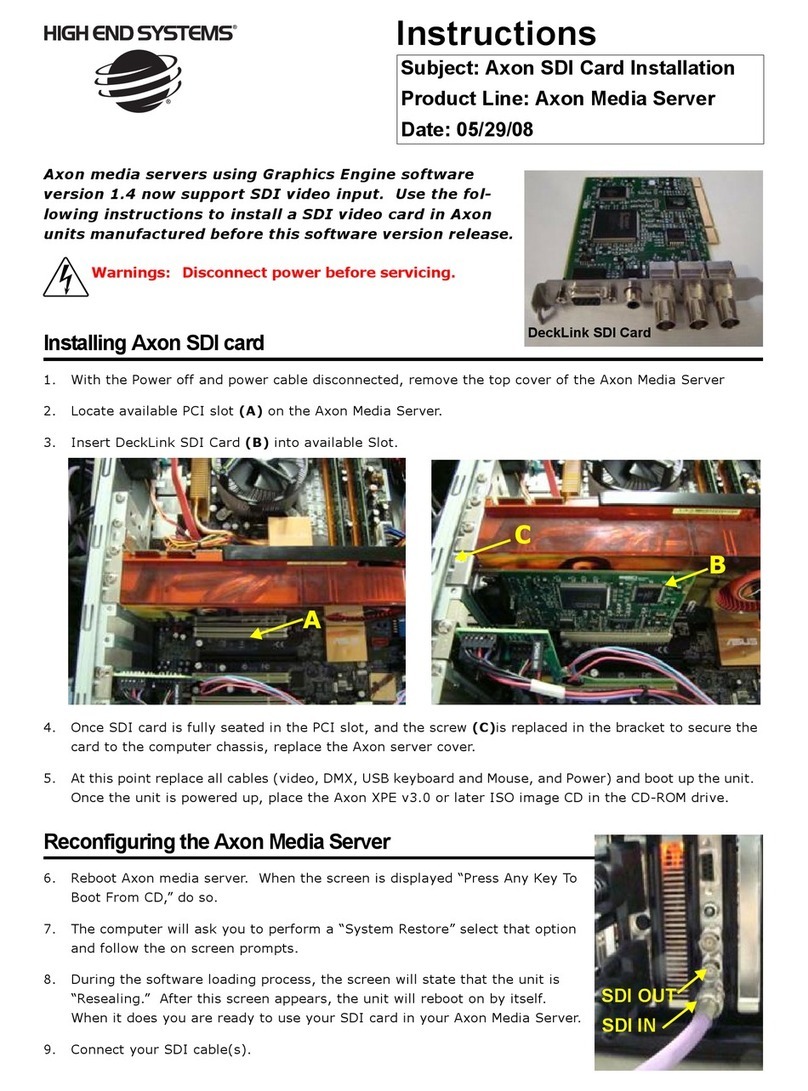

High End Systems

High End Systems Axon Axon SDI Card installation instructions

CraftyMech

CraftyMech BITKIT manual