15-Dec.2017 Ver.1.4

TAIYO YUDEN CO., LTD.

TAIYO YUDEN CO., LTD. 8/9

EBSGJN, EKSGJN

EBAGJN, EKAGJN

Important notes

The evaluation board included with the Nordic Development Kit uses a 16MHz clock. Therefore the

sample code from Nordic is designed to be used with a 16MHz clock. On the other hand, the

EYSGJN and EYAGJN series module uses a 32MHz system clock, making it incompatible with the

Nordic sample code (i.e. sample code does not configure HFCLK: XTALFREQ register for 32MHz).

To fix this issue, we need to write the value 0xFFFFFF00 to the UICR (User Information

Configuration Register) at address 0x10001008. Please note that the UICR is erased whenever you

download a SoftDevice.

The UICR can be written by using the debug tools:

nrfjprog.exe --snr <your_jlink_debugger_serial_number> --memwr 0x10001008 --val 0xFFFFFF00

Or the following code can be added to the SystemInit function in the system_nRF51.c file, right

before launching the TASK_HFCLKSTART task:

if (*(uint32_t *)0x10001008 == 0xFFFFFFFF)

{

NRF_NVMC->CONFIG = NVMC_CONFIG_WEN_Wen << NVMC_CONFIG_WEN_Pos;

while (NRF_NVMC->READY == NVMC_READY_READY_Busy){}

*(uint32_t *)0x10001008 = 0xFFFFFF00;

NRF_NVMC->CONFIG = NVMC_CONFIG_WEN_Ren << NVMC_CONFIG_WEN_Pos;

while (NRF_NVMC->READY == NVMC_READY_READY_Busy){}

NVIC_SystemReset();

while (true){}

}

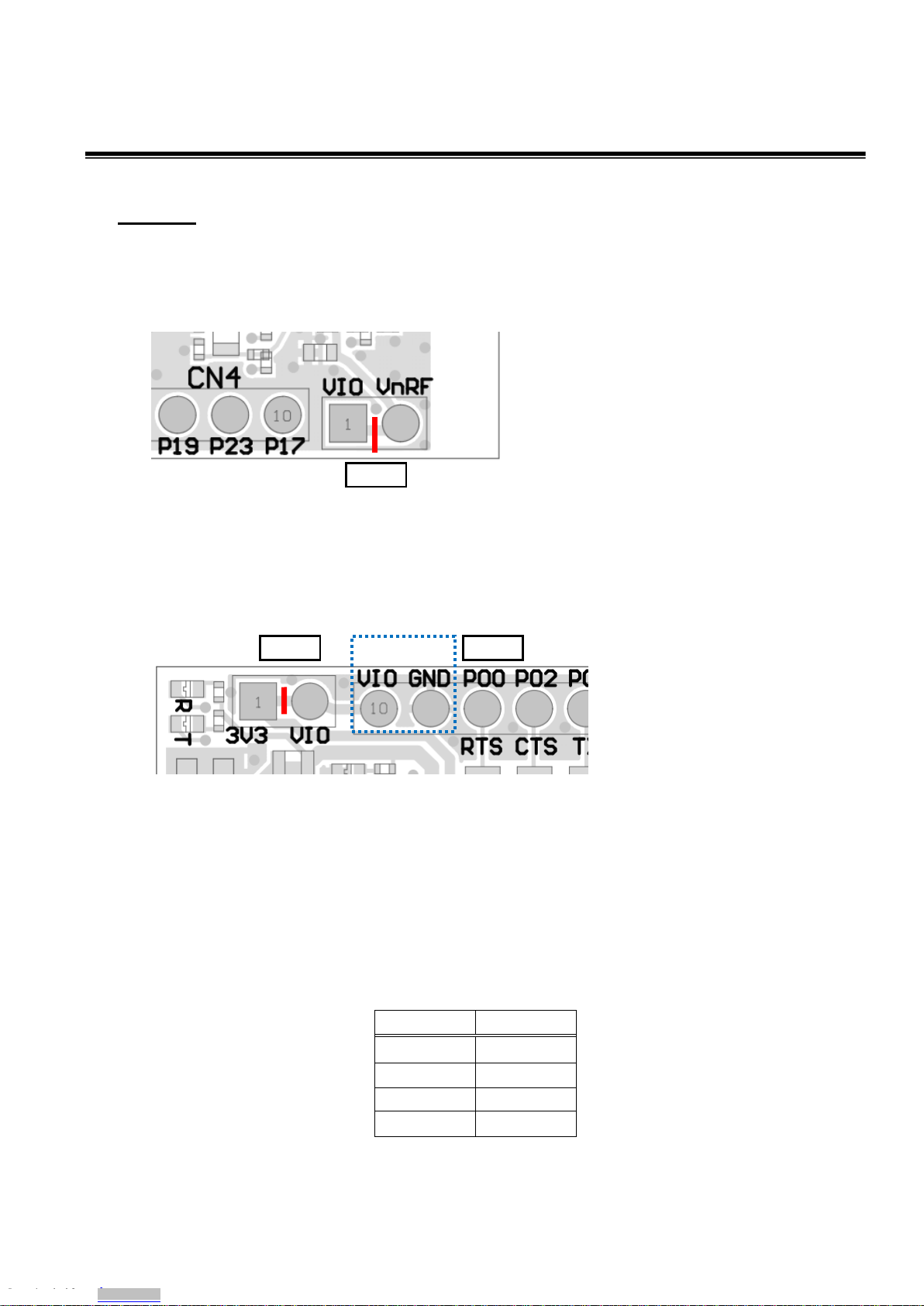

32kHz Clock

This module does not installed 32.768kHz crystal. In case of operating without external crystal,

please use following example code in order to enable internal 32.768kHz RC oscillator (32k

RCOSC).

SOFTDEVICE_HANDLER_INIT(NRF_CLOCK_LFCLKSRC_RC_250_PPM_250MS_CALIBRATION, false);

Note that when you choose to use the RC oscillator, it will add around 10uA average current

consumption compared to a 20ppm external crystal.

Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.