Page| 1

1. Forward

This tutorial is designed for beginners interested in getting started working with FPGA technology. FPGAs offer a very new and

robust way to tackle digital system design. Unfortunately, their power and flexibility, coupled with their multidisciplinary nature,

make them extremely complicated to work with. Consequently, the barrier to entry is quite a bit higher than your everyday

microcontroller or discrete integrated circuit. An FPGA designer really needs to know a lot of information to make an FPGA do

anything at all.

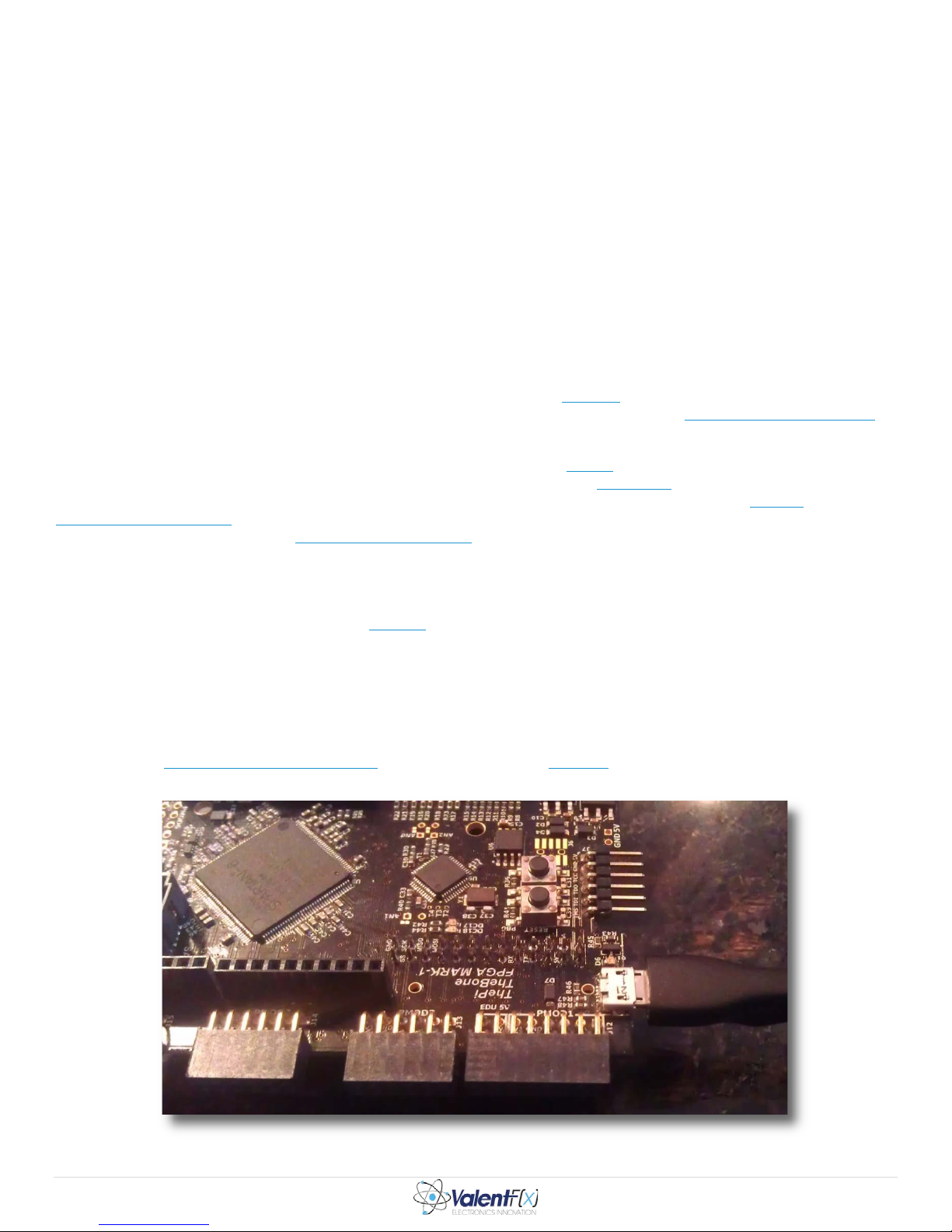

In an effort to ease this FPGA learning curve and get exposure to a wider audience of electronics practitioners, both hobbyist and

professional alike, ValentF(X) has developed the Mark 1 FPGA board. It is a part of the Logi family of boards and is a fantastic

platform to start out on for anyone who wants to learn about FPGA technology. It has many features that make it easy for beginners to

dive quickly into FPGA development as well as IO capabilities and a form factor that a seasoned professional can even appreciate.

The primary goal of this guide is to take an absolute beginner from having a lifeless piece of hardware in front of them, to making it

actually do something in a matter of hours. Therefore, the guide has also been designed to be a concise, goal oriented read. In areas

where verbosity would slow the pace, there are many links to external content provided so you can explore and further your education

on your own time.

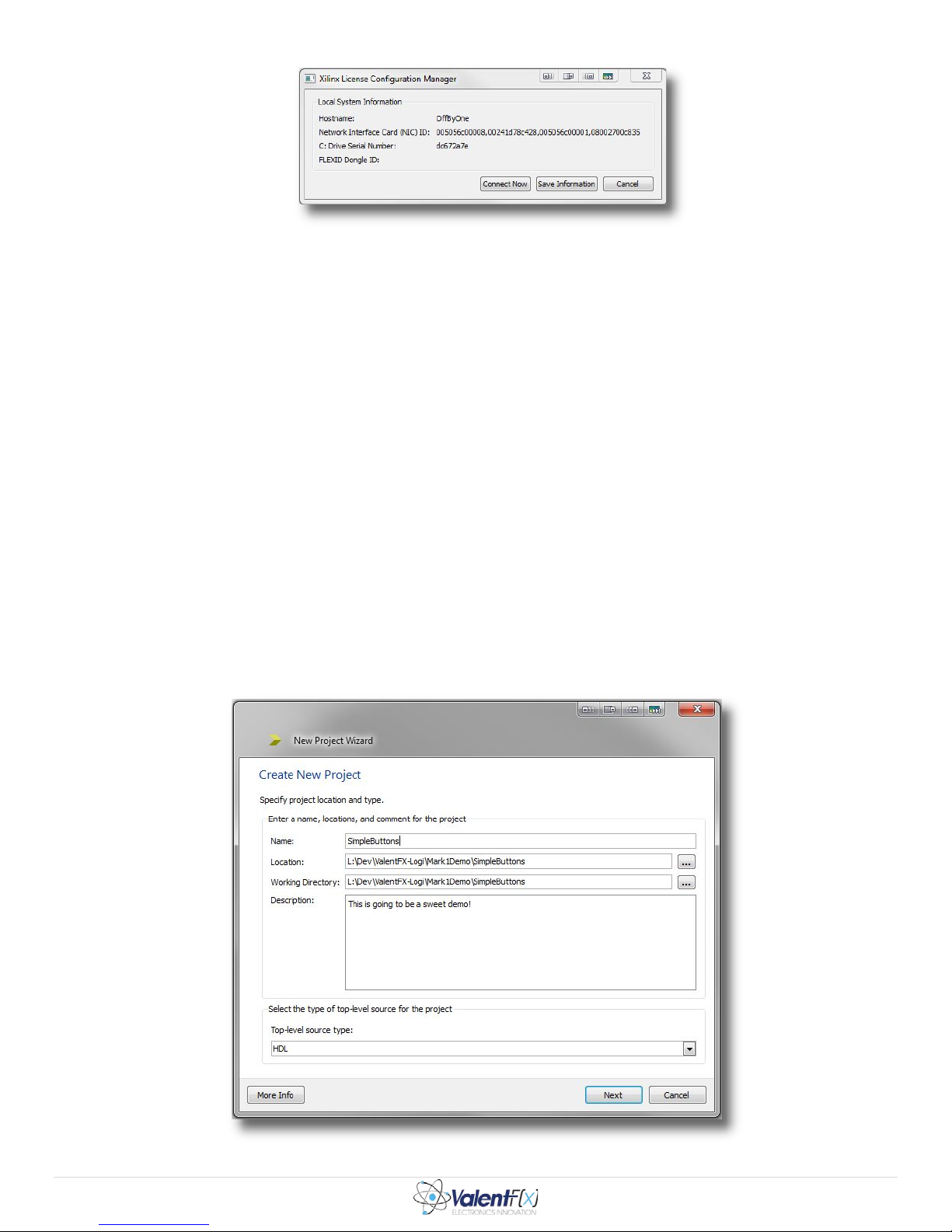

Note, the part of this guide that actually takes the longest is downloading the FPGA development environment from Xilinx – the file is

nearly eight gigabytes.If you’re interested in completing this tutorial in an afternoon, start by getting the download going now! See

the section called Setup Your Development Environment to start downloading the Xilinx “ISE” development software.

2. Background

Field programmable gate arrays (FPGAs) are unique integrated circuits (ICs) whose defining characteristic is that their internal logic

can be reprogrammed indefinitely. They arrived on the scene around 1986 and have grown ever more sophisticated and capable over

the years. Today they are found it many electronics devices such as networking equipment, electromechanical control equipment,

cellular equipment as well as in simpler designs such as your car or maybe even your microwave.

At a fundamental level, the “program” running on an FPGA is actually a digital circuit whose wires are “executing” combinatorial

and/or sequential logic. In FPGAs, the circuits consist of several to many millions of fundamental logic gates such as an OR, AND,

NOT and XOR gate, just to name a few. An FPGA design typically has many inputs and outputs as well as clock signals to keep

things synchronized.

It’s really best to think about the logic on the FPGA’s “fabric” as a physical circuit. In computing applications that run on processors,

people are normally accustomed to thinking about their program as running in a sequential manner. The code executes from top to

bottoms right? Well, in FPGAs this is typically not the case. Everything is happening at once. There can be many parallel “logical

flows” executing at the same time. Furthermore, parallel logical flows can interact with each other. In reality, you’re building a

circuit on the FPGA fabric, not a sequential processor. And, as in any circuit you are free to route any wire or “net,” to any

destination.

The reprogrammable internal logic found in FPGAs is an immensely powerful feature for many other reasons as well. For example,

back in the days before FPGAs if you were designing a printed circuit board (PCB), the final design is what you were stuck with. And

of course, if a mistake was made in the routing of the electrical signals you will have nearly irreversible problems.

Say some data signal from pin P73 of component U8 was wired to pin P27 of component U15 on the PCB; you would lay a copper

trace on the PCB and then you are committed to that signal. If there was a mistake made on this trace or for some reason, after the

PCB was manufactured the design no longer needed that signal, you have no option but to revise the board design and manufacture the

board again. With an FPGA you might not need to do this depending on the circumstances. Component U8 and U15 might actually

be in the FPGA fabric and therefor, all you would need to do is reprogram the FPGA to fix your mistake. Also, with an FPGA you

could potentially add more functionality to the board’s design after the PCB was made just by reprogramming the FPGA fabric!

At a higher level the reprogrammable, digital circuitry found in FPGAs allows designers to put much of the logic found in many

discrete integrated circuits, onto one FPGA chip. This “part consolidation” feature makes for cheaper PCB designs and allows a

greater margin of error in a PCB manufacturing. Imagine a PCB with 30, discrete integrated circuits on it. There would be a very

large number of traces that need to be perfectly placed in order for the design to work. If you took the same design and consolidated

the logic of 25 of these discrete integrated circuits onto the FPGA’s fabric, the PCB would have far fewer traces that could go wrong.

Furthermore, because the FPGA’s internal logic is reprogrammable; the FPGA designers can iterate their logical implementation of

the 25 ICs as many times as they want without incurring any costs of “spinning” a new PCB – the only cost is the programmer’s time.

Also, designs based on FPGAs often have a much shorter time to market than a similar ASIC design and therefore are far more cost

effective for smaller runs of complex custom hardware.