6

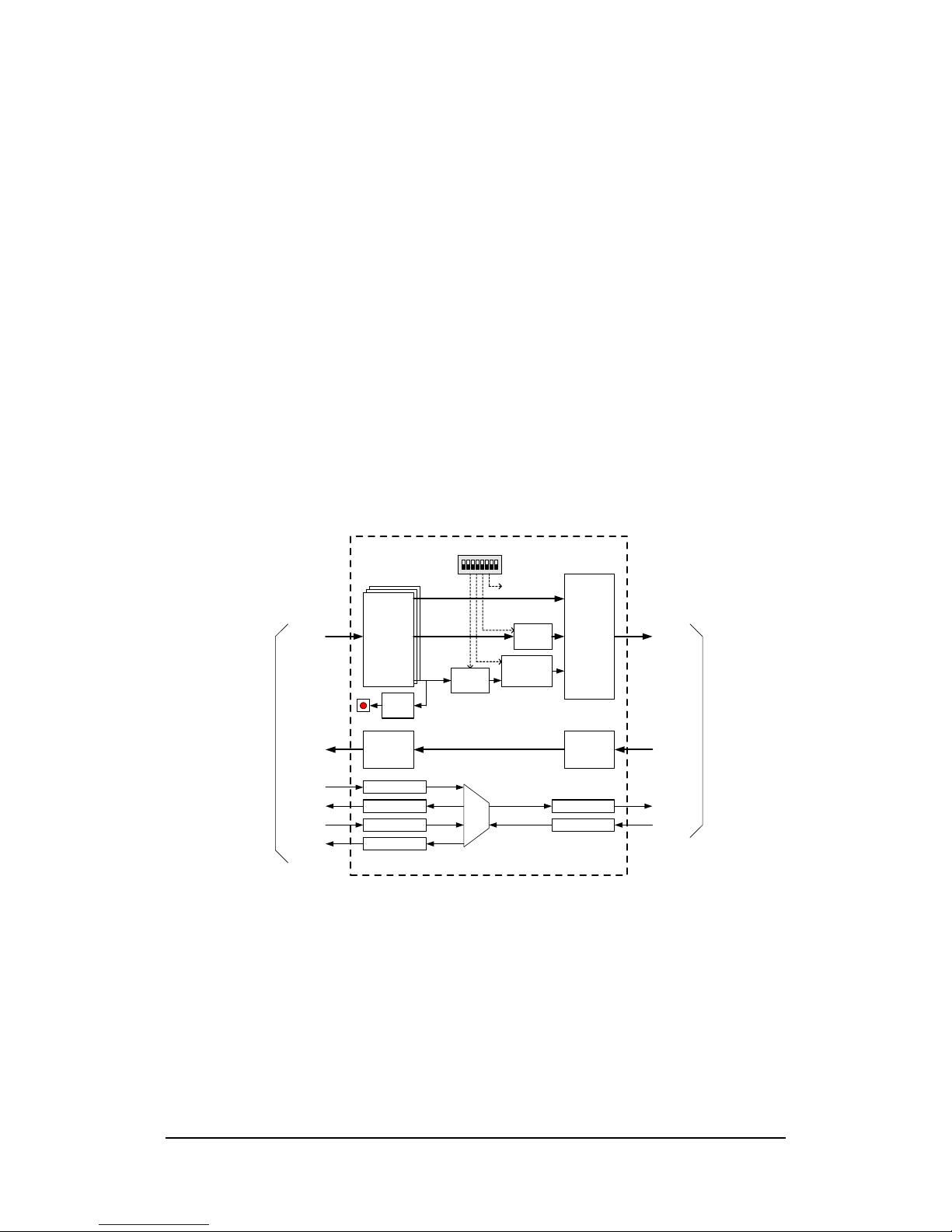

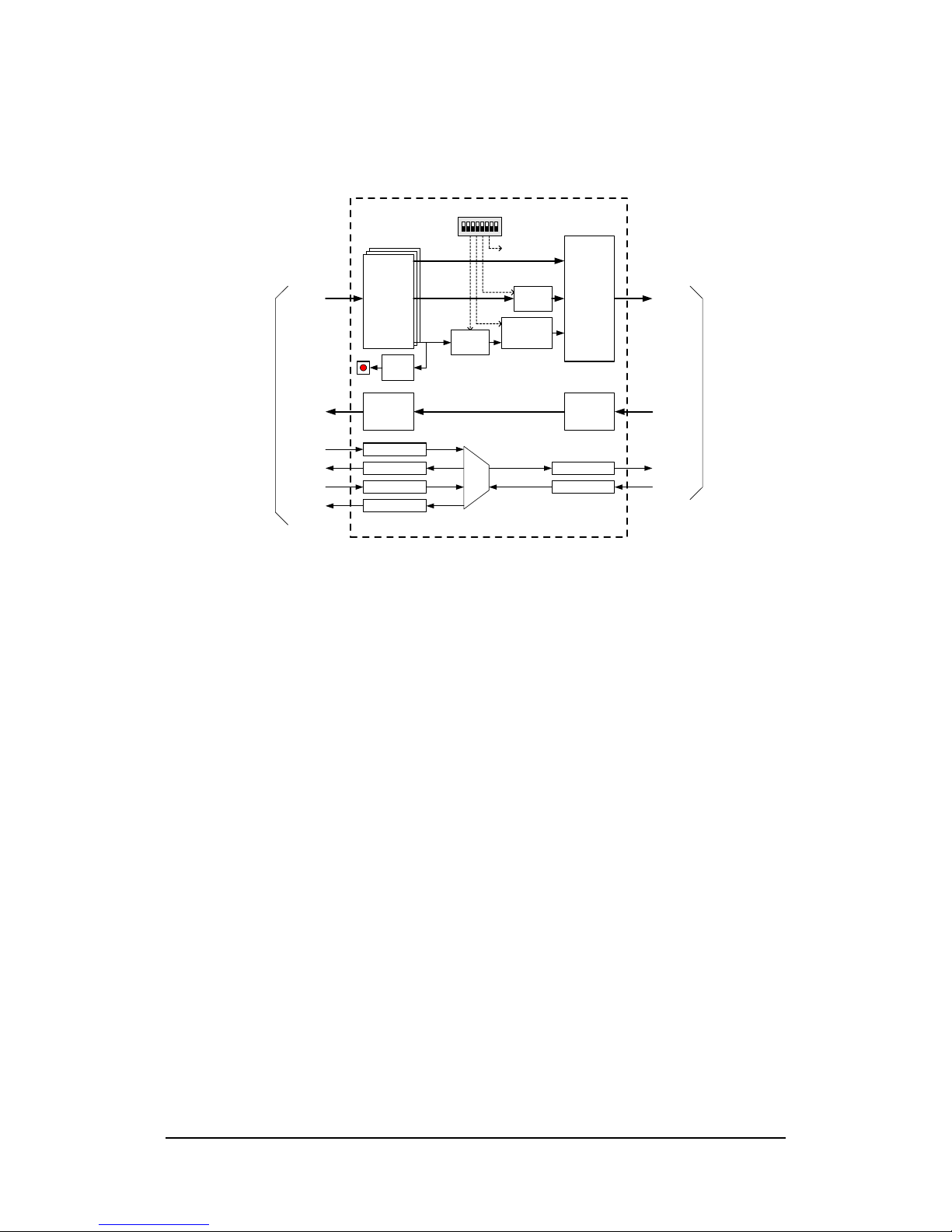

The CLT-302 receives parallel digital camera data on the 100-pin camera connector and

maps the pixel data into the corresponding Camera Link “base” configuration format. The

CLT supports single-channel (monochrome) cameras with 8/10/12/14/16-bit pixels, dual-

channel 8/10/12-bit cameras, and 8-bit color cameras.

The latency (i.e. delay) of the video, control, and communication signals passing through

the CLT-302 is minimal. This is an important criteria in some time-critical application.

The delay for the camera video through the CLT-302 is only a few pixel clock periods.

See Table 1.1 for CLT-302 latency specifications.

Camera timing signal characteristics are selected using the rear-panel mode switch. One

switch position is used to select the polarity of the line valid signal, and a second switch

position is used to select the polarity of the frame valid signal. In most cases, a “high”

state on the line enable and frame enable signals is used to envelope valid lines and

frames of video data, respectively. The settings enable the user to select either active-high

or active-low polarities for each timing signal. Note that the frame enable signal is not

used in line scan applications. Switch settings are defined in Section 1.3.1.

Camera Link incorporates a data valid signal which is used to qualify the video data. This

signal is generated by the CLT-302 and sent to the Camera Link frame grabber. Most

LVDS and RS-422 digital cameras do not incorporate a data valid type signal. The CLT-

302 incorporates a provision for the rare cases in which a data valid is provided by the

camera. When the data valid pass-through dip switch position is raised, the CLT-302

passes the data valid signal from the camera to the frame grabber. The Camera Link data

valid input is active-high, qualifying the incoming video data when the signal is high. A

second dipswitch position, data valid polarity, supports either active-high or active-low

data valid signals from the camera. When the data valid pass-through dipswitch is in the

normal (low) position, the CLT-302 maintains the data valid signal sent to the frame

grabber in the high position. The only exception is when the clock multiplier is being used

which is discussed next.

Camera pixel clock characteristics are selected using the rear-panel mode switch. One

switch position is used to select which pixel clock edge, rising or falling, is used to sample

the data and timing signals received from the camera. Two additional switch positions are

used to enable the CLT-302 clock multiplier circuit. The clock multiplier supports the use

of camera with pixel clock frequency below the Camera Link 20MHz minimum by

“multiplying” the camera clock frequency before it is sent to the Camera Link frame

grabber.. For cameras with pixel clocks in the 10-19.99 MHz range, the clock multiplier is

used to 2x (i.e. double) the clock frequency. For cameras with pixel clocks in the 5-9.99

MHz range, the clock multiplier is used to 4x (i.e. quadruple) the clock frequency. For

cameras with pixel clocks in the 2.5-4.99 MHz range, the clock multiplier is used to 8x the

clock frequency.