VA10800/VA10820 Evaluation Board User’s Manual

V3.0

1

Contents

1 Introduction ............................................................................................................................ 2

1.1 Purpose of Document ..................................................................................................... 2

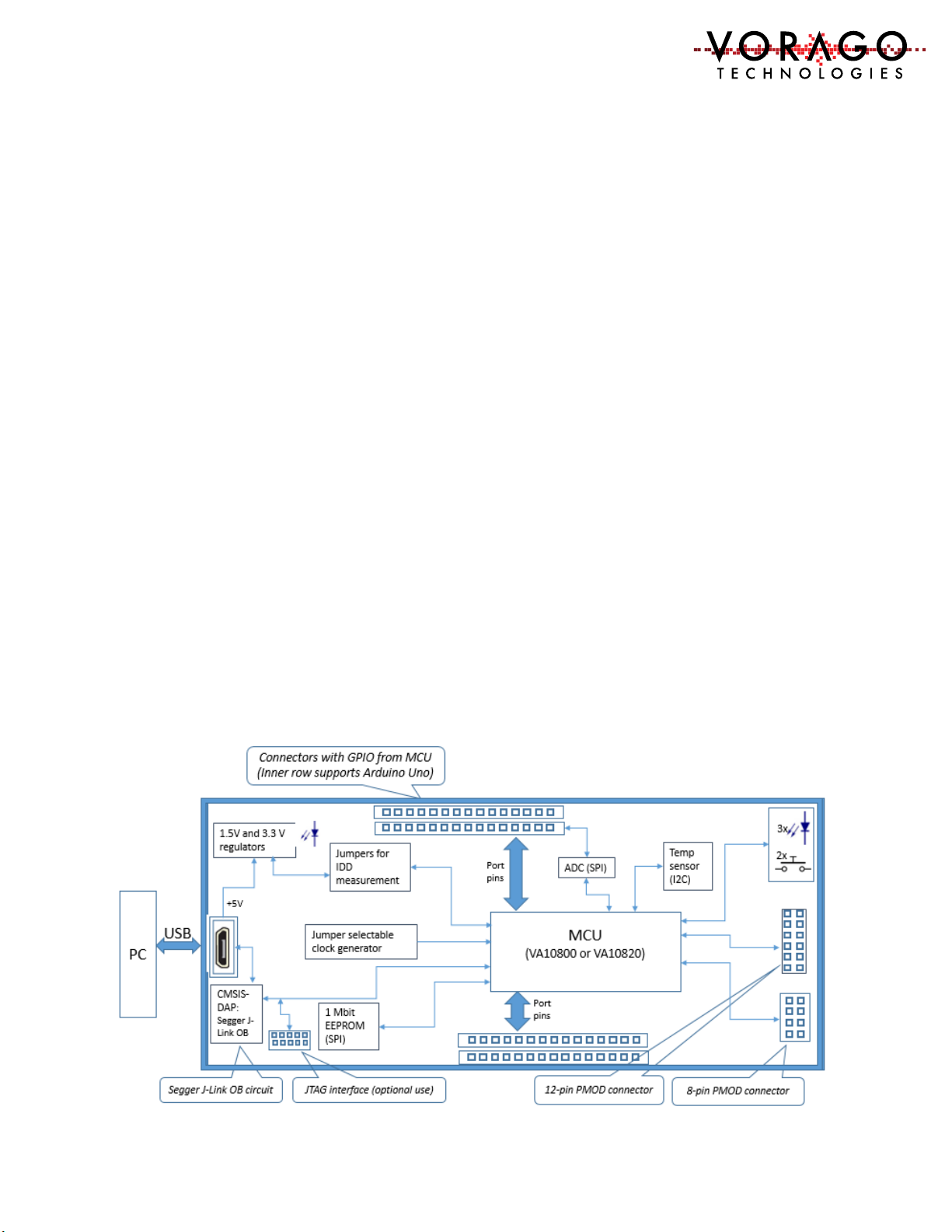

1.2 Overview of Hardware and Software components ........................................................ 2

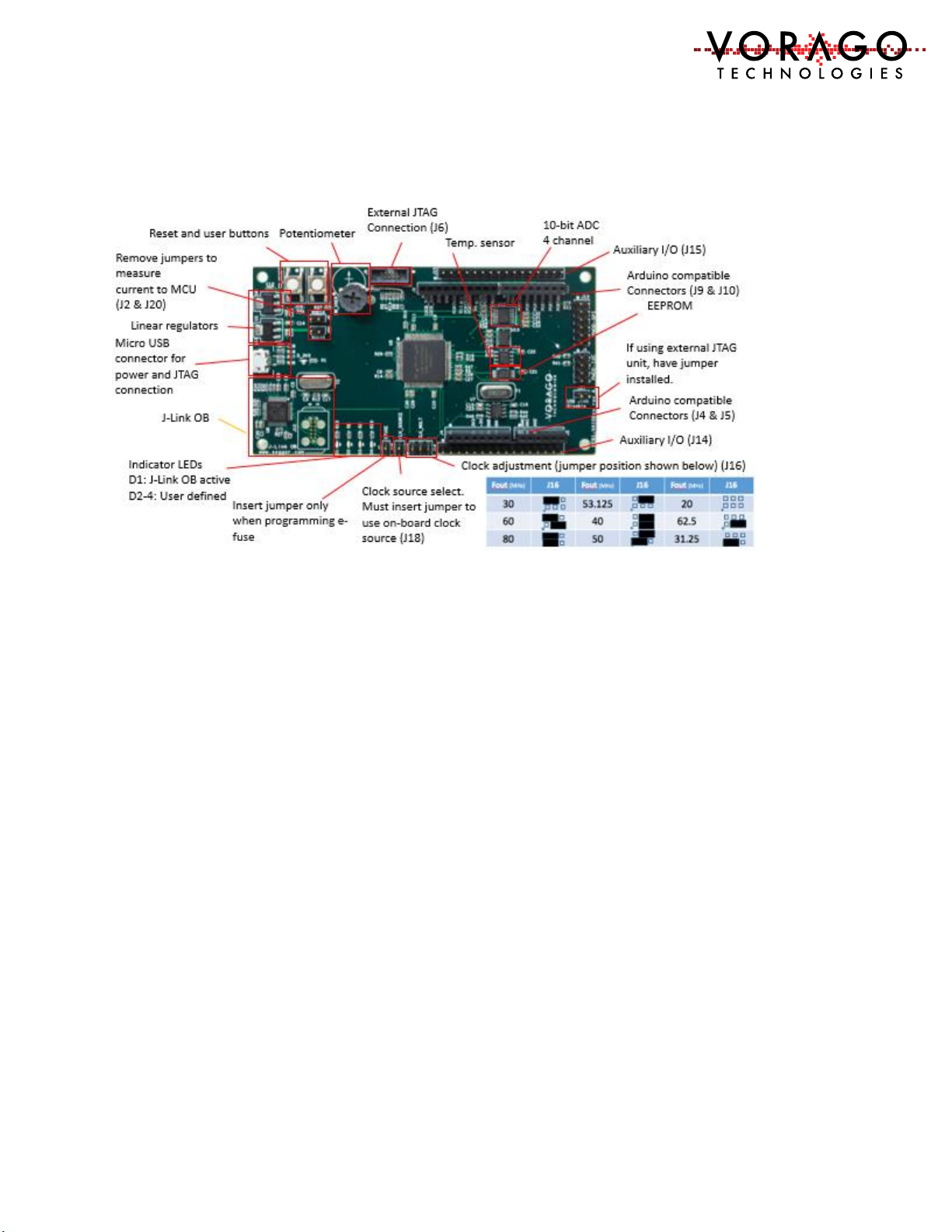

1.3 REB1 board component placement diagram.................................................................. 3

1.4 Connector pin assignment table..................................................................................... 3

1.5 Materials List................................................................................................................... 4

1.6 Support............................................................................................................................ 4

2 Software Setup........................................................................................................................ 4

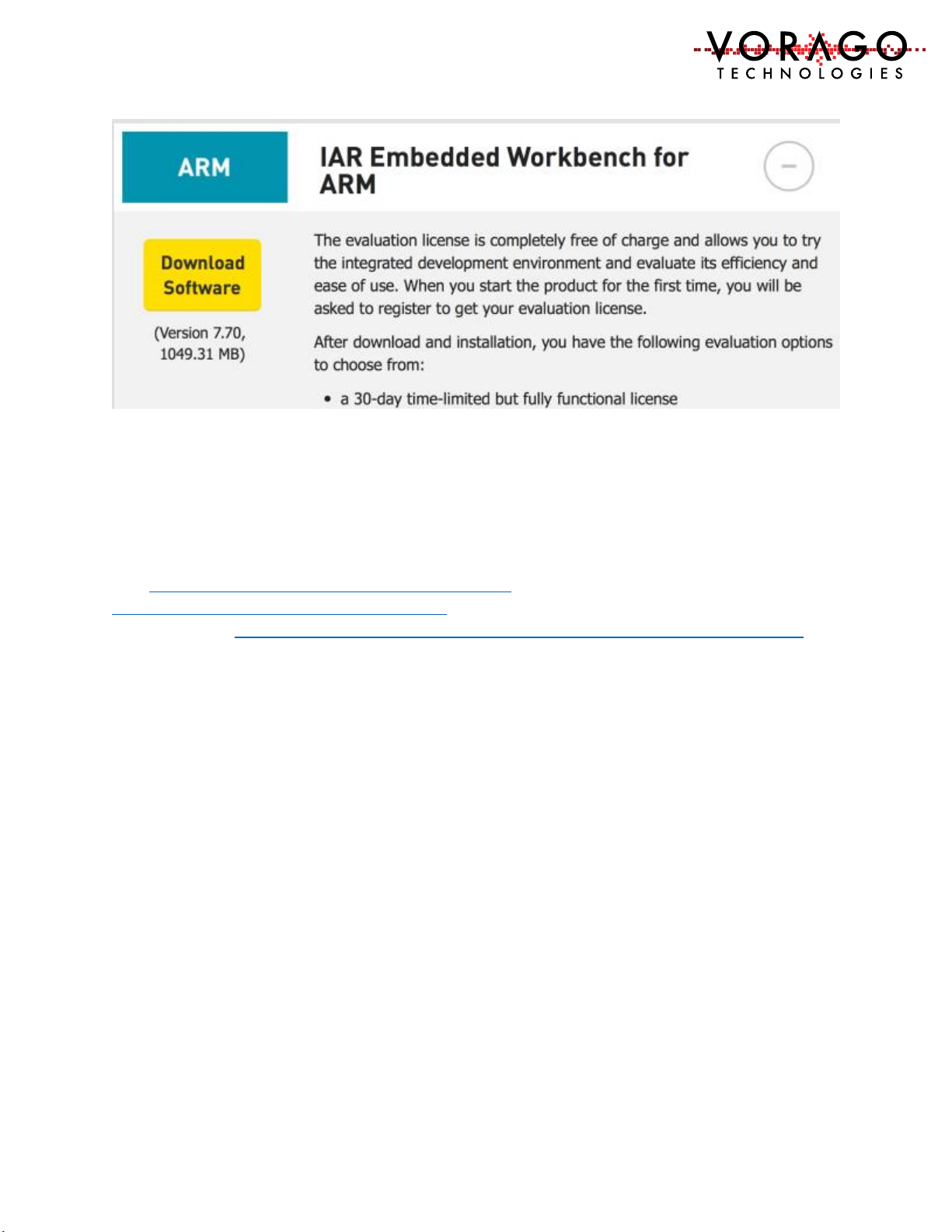

2.1 Required Downloads....................................................................................................... 5

3 Hardware check ...................................................................................................................... 9

3.1 Powering up the board ................................................................................................... 9

4 Starting an IDE and building a program.................................................................................. 9

4.1 Keil IDE –......................................................................................................................... 9

4.2 IAR EWARM IDE –.......................................................................................................... 18

4.3 iSYSTEM winIDEA IDE –................................................................................................. 21

4.4 J-Link OB and RTT (Real Time Terminal) ....................................................................... 25

4.5 Programming procedure (Keil Specific) ........................................................................ 26

5 Software Development Kit.................................................................................................... 28

5.1 Project organization...................................................................................................... 28

5.2 CMSIS compatible driver............................................................................................... 29

5.3 Preprocessor directives................................................................................................. 30

6 Lab exercises ......................................................................................................................... 30

6.1 Lab 1 –Toggling an output pin to blink an LED ............................................................ 30

6.2 LAB2 - Advanced input pin filtering and debounce of switch input. ............................ 32

7 Commonly asked questions .................................................................................................. 32

8 Other resources for VA108x0 code....................................................................................... 33

9 Revision history..................................................................................................................... 33