WECA W6810DK

2727 N First Street, San Jose CA 95134

2

Chapter - 1...................................................................................................................................................... 3

General Description........................................................................................................................................ 3

Introduction: ................................................................................................................................................... 3

W6810DK Features:....................................................................................................................................... 3

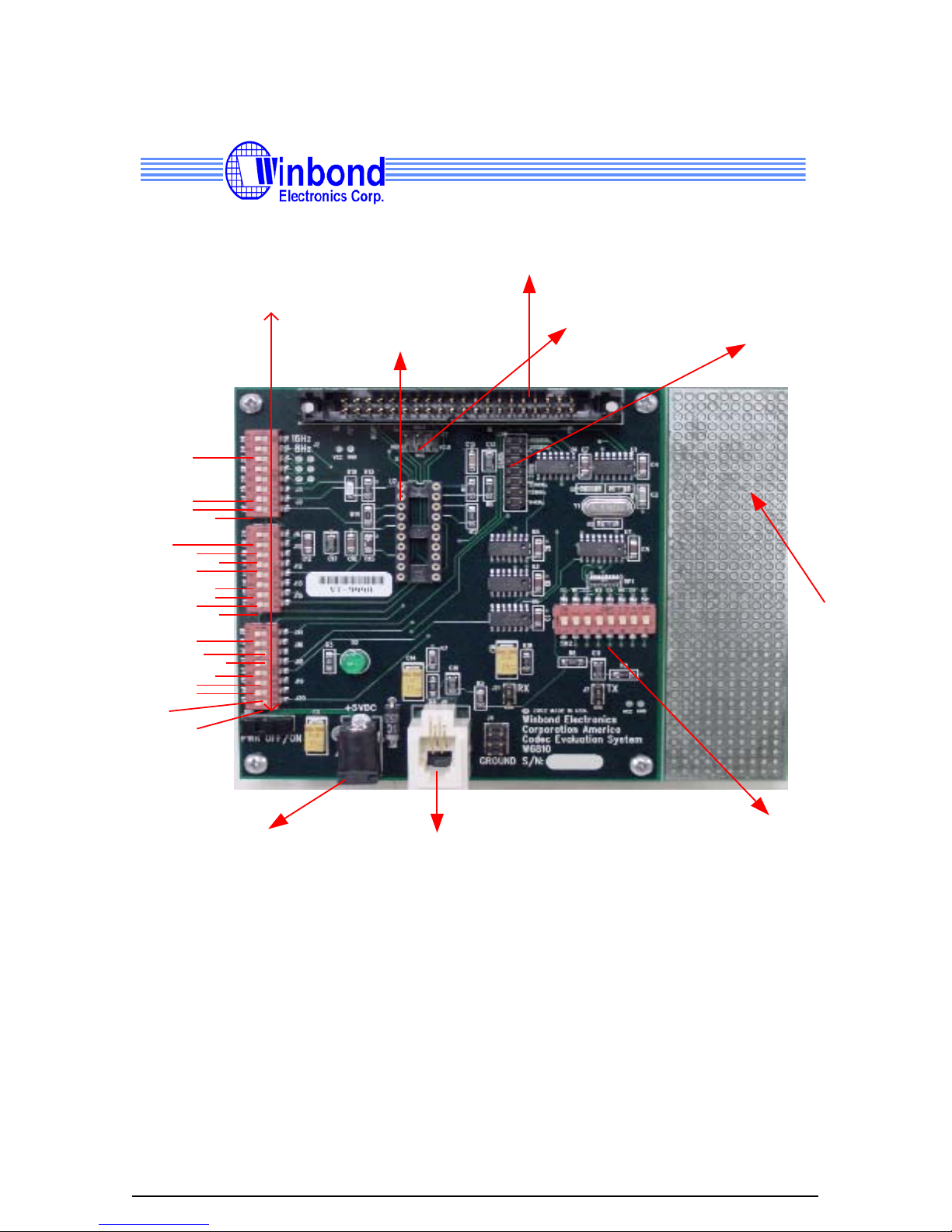

Figure 1: W6810DK Evaluation System Component Placement ............................................................................. 4

Chapter - 2...................................................................................................................................................... 5

Hardware Description..................................................................................................................................... 5

Clock Generator: ............................................................................................................................................ 5

Frame Sync:.................................................................................................................................................... 5

BIT CLOCK:.................................................................................................................................................. 6

256 KHZ:........................................................................................................................................................ 6

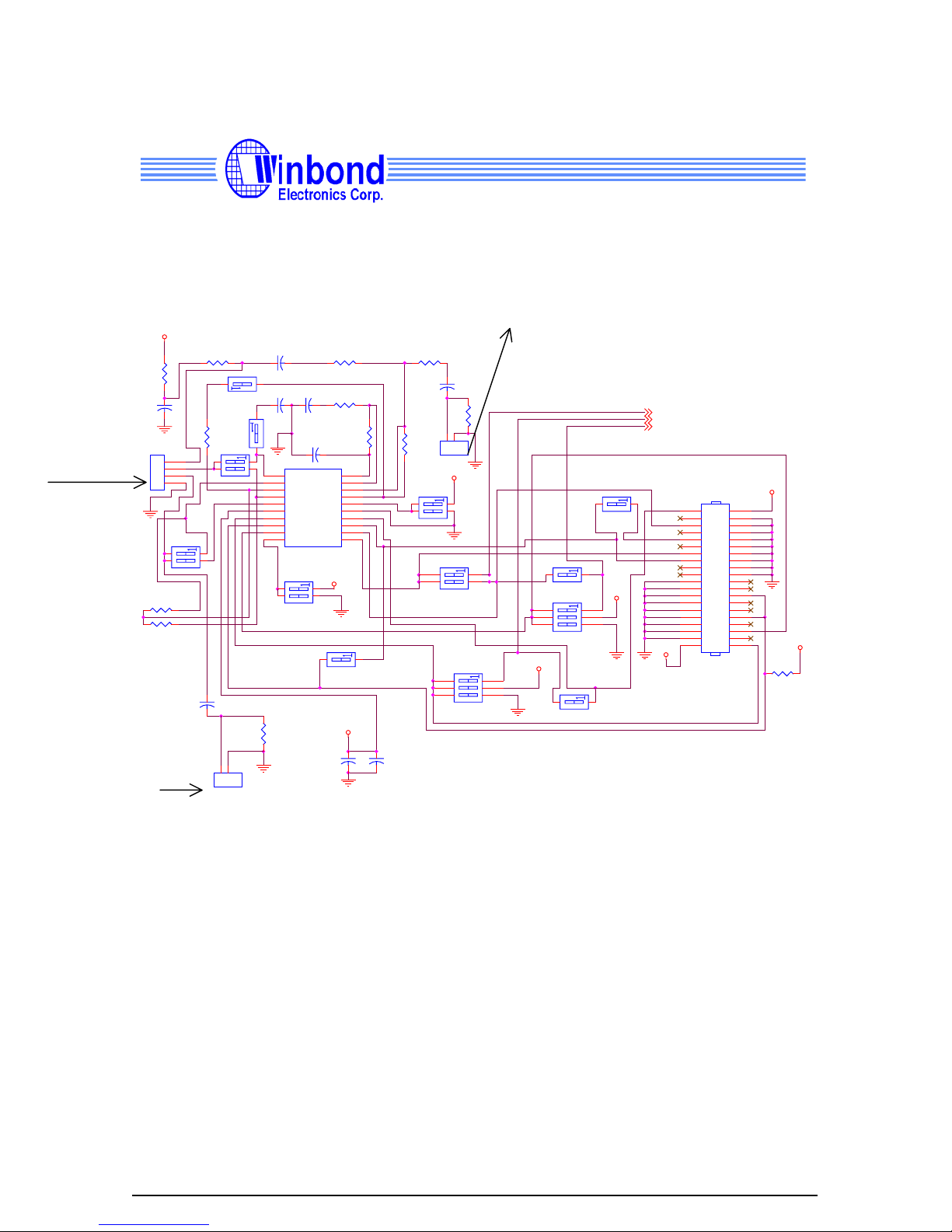

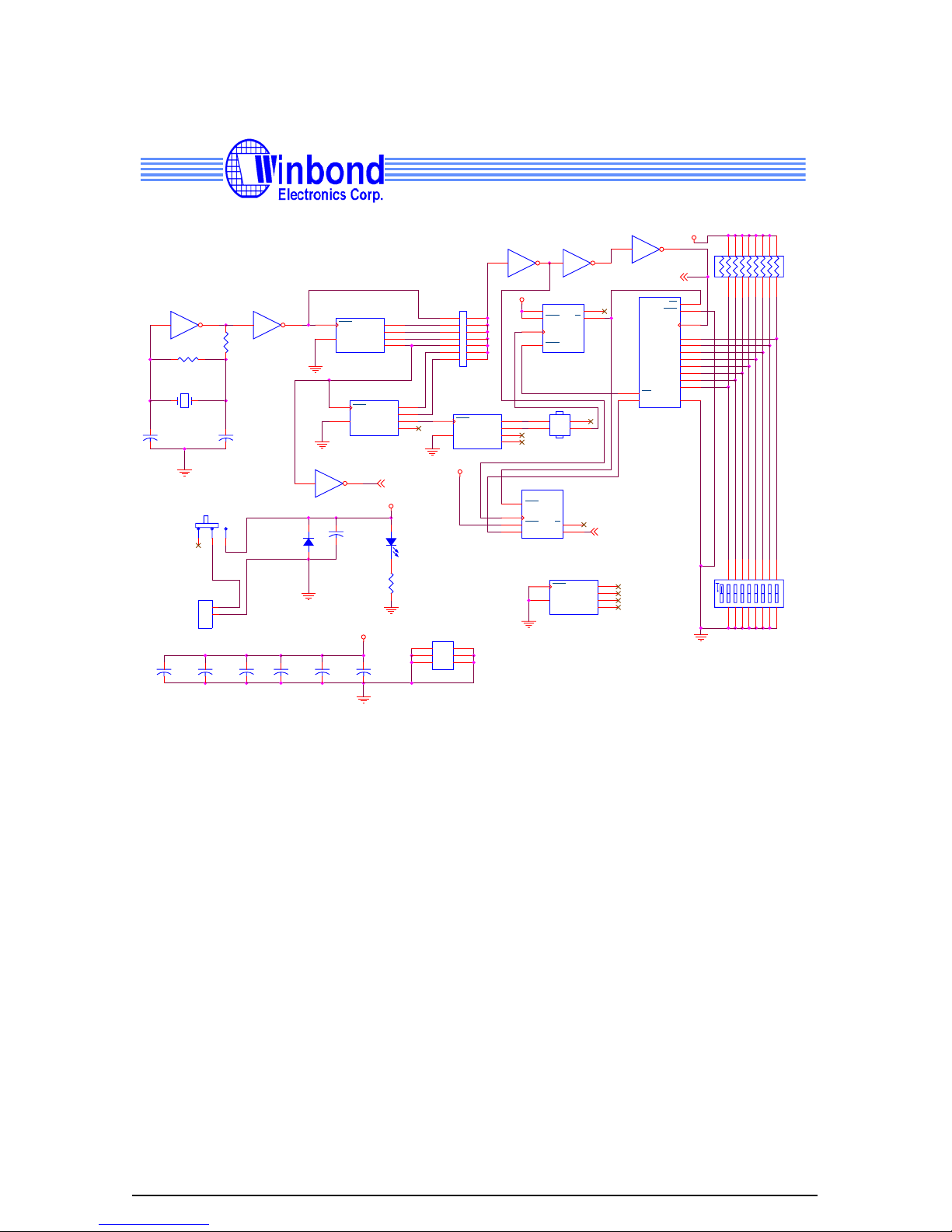

Figure 2: W6810DK Evaluation System Schematics diagram....................................................................... 7

Chapter - 3...................................................................................................................................................... 9

Jumper Descriptions ....................................................................................................................................... 9

J2A: Frame Sync: .................................................................................................................................. 10

J3: Power Supply 5VDC.......................................................................................................................... 10

J4: GND TST points ................................................................................................................................ 10

J5: Side Tone ........................................................................................................................................... 10

J6: VAG CAP ENABLE: ........................................................................................................................ 10

J7: Transmitter......................................................................................................................................... 10

J8: RJ11 Handset connector.................................................................................................................... 10

J9A: 2.5V Reference Voltage ................................................................................................................. 10

J9B: SPKR+ = PAO ................................................................................................................................ 10

J10: A-Law and µ-Law Selection: ........................................................................................................... 10

J11: 2x20 pin Header:.............................................................................................................................. 11

J12A: SPKR- = R0- ................................................................................................................................. 11

J12B: SPKR-=PA0+ ................................................................................................................................ 11

J13: PCMT:.............................................................................................................................................. 11

J14: BCLKT=BCLK................................................................................................................................ 11

J15A: MCLK = 256KHz ......................................................................................................................... 11

J15B: MCLK=BCLK............................................................................................................................... 11

J16A: POWER-UP .................................................................................................................................. 11

J16B: POWER-Down.............................................................................................................................. 11

J17A: BCLKR = BCLK........................................................................................................................... 11

J17B: BCLKR = BCLK........................................................................................................................... 12

J17C: BCLKR = BCLK........................................................................................................................... 12

J18: PCMT = PCMR ............................................................................................................................... 12

J19A: FSR = FSYNC .............................................................................................................................. 12

J19B: FSR = VCC ................................................................................................................................... 12

J19C: FSR = GND................................................................................................................................... 12

J20: FSX= FSYNC .................................................................................................................................. 12

J21: Receiver Path ................................................................................................................................... 12

Chapter - 4.................................................................................................................................................... 13

Operation Modes .......................................................................................................................................... 13

Standalone Operation: .................................................................................................................................. 13

Back-To-Back Operation: ............................................................................................................................ 14