Le51HE0060V2 Eval Board User Guide

4

Zarlink Semiconductor Inc.

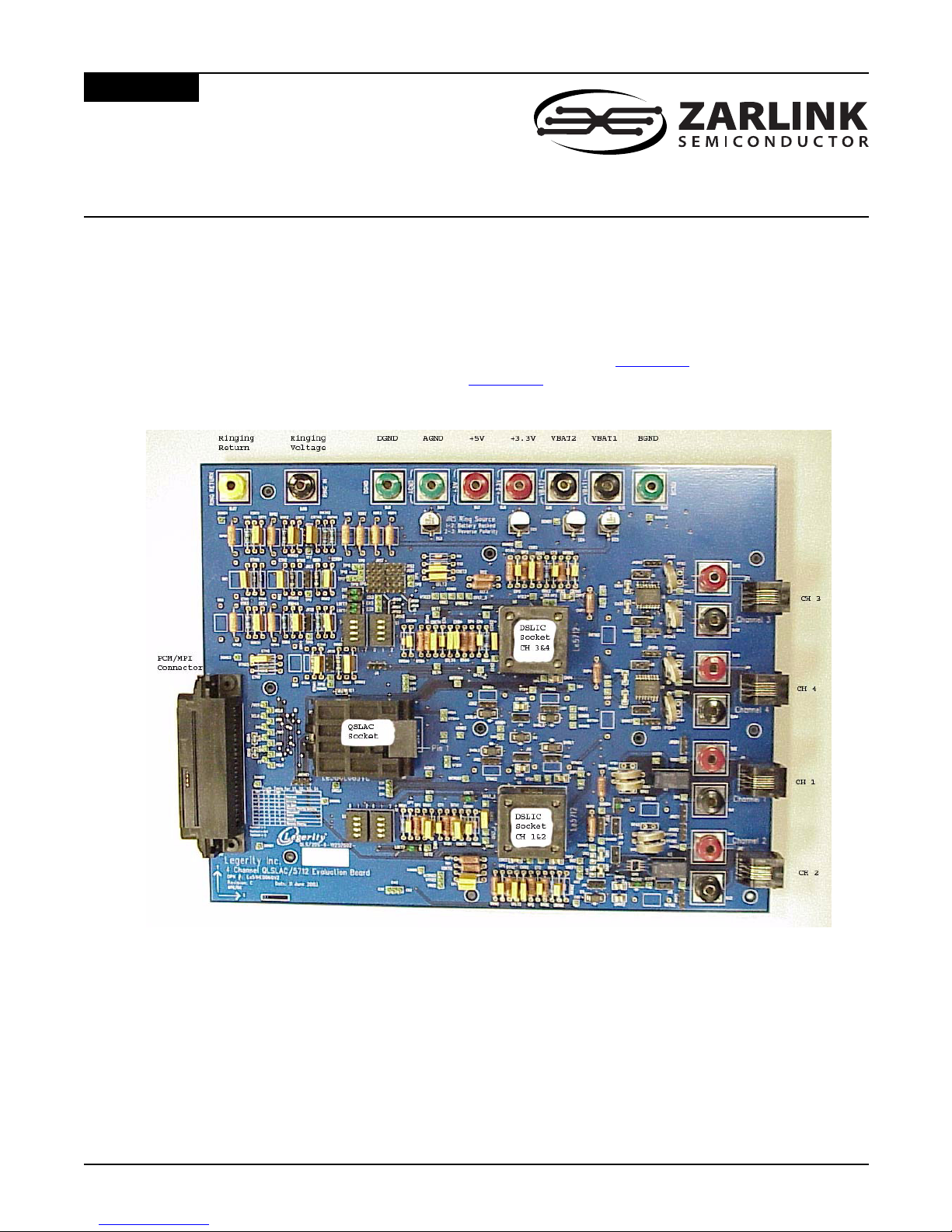

2.2 BOARD CONNECTIONS

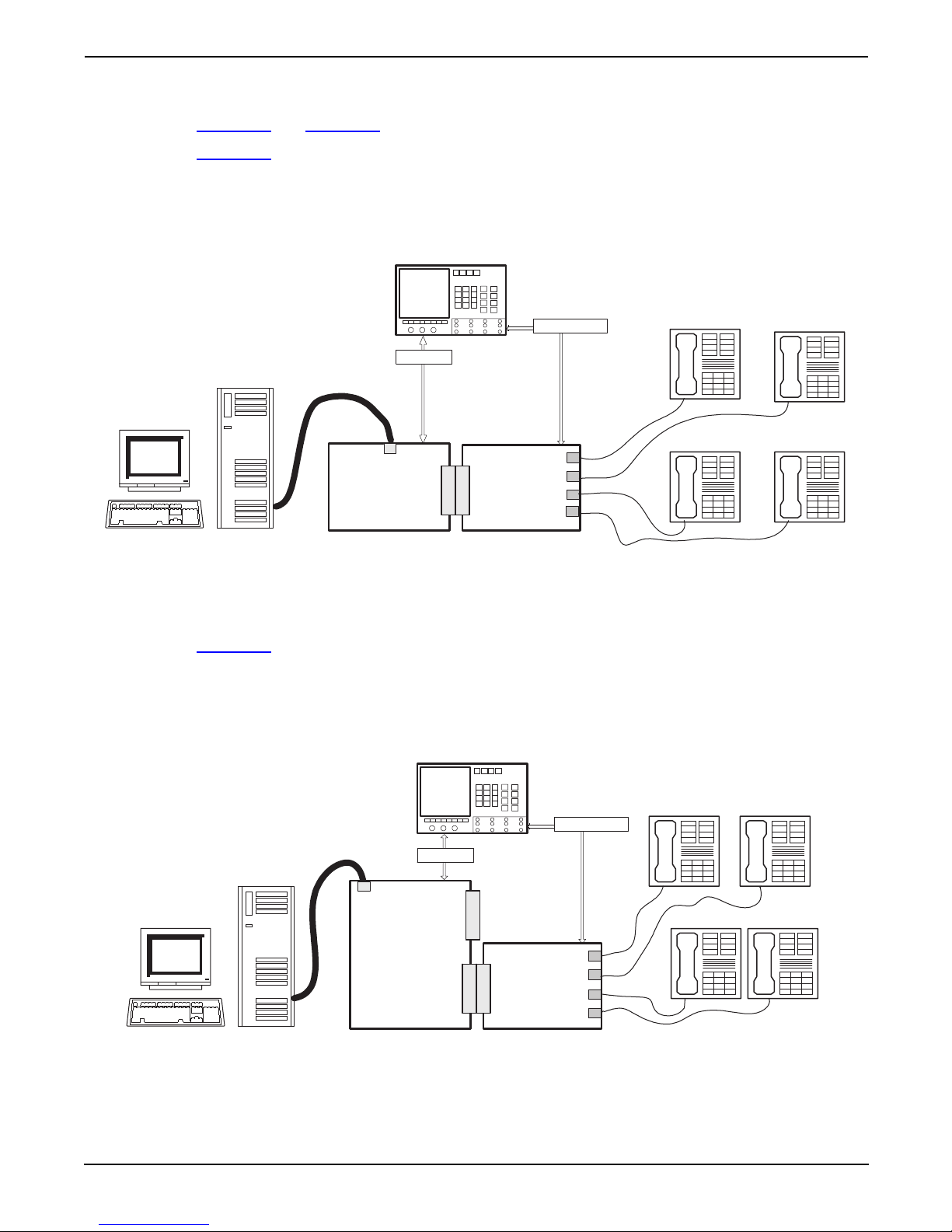

The Le51HE0060V2 can be plugged directly into either a Voice Path Demo (VP Demo) Board or an

Advanced Computer Interface Board (ACIF2-A) via the 50-pin IFB01 connector of the

Le51HE0060V2 evaluation board. All power is supplied via the nine banana jacks across the top of

the board. est points are included for all major signals. Eight banana jacks, labeled TIPXand

RINGX, are located on the right-hand edge of the evaluation board for connection to test equipment

or for connecting to a standard telephone station set. These jacks are also connected in parallel

with an industry standard RJ-11 connector.

2.2.1 Power

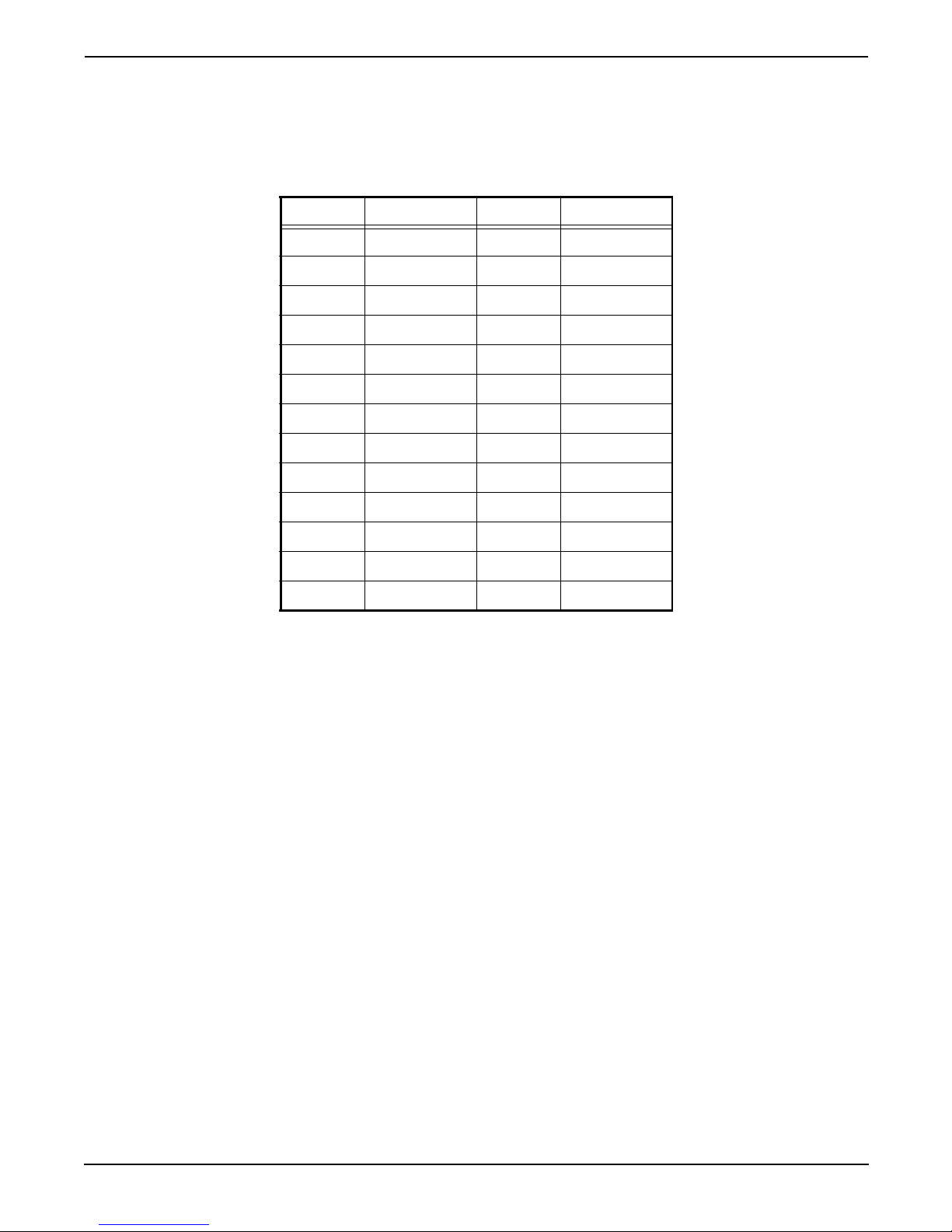

The required power for the board is supplied through nine banana jacks, as detailed in Table 2–1.

Table 2-1 Power Connections

Before connecting a ringing supply, the user should assure that the jumpers used for earth/battery

backed ringing selection are appropriately set. Details are contained in Chapter 3

Power sequencing is recommended, though not required. The suggested power sequencing

scheme is: VBAT1 powered-up first, followed by VBAT2, +3.3 V, and finally the +5-V supply. DGND

and AGND are tied together on the board with zero ohm resistors R9 and R10. BGND is not tied to

either AGND or DGND and care is required to assure that the maximum potential difference

between these points, as defined in the DSLIC data sheet, is not exceeded

2.2.2 Telephone Line Interface

To interface the Le51HE0060V2 evaluation board to a telephone station set, plug the telephone

station set into the TIP and RING banana jack pair (BJ1 and BJ2, BJ3 and BJ4, BJ12 and BJ13 or

BJ14 and BJ15). Alternately, the RJ-11 jacks (J11, J12, J13, J14) can be used.

A tip/ring surge protection circuit is included on the board. The LCAS protection circuits use a fixed

voltage protection scheme while the EMR protection circuits use a battery referenced protection

scheme.

Jack # Signal Description Board Name (PW1)

BJ5 VBAT1 Battery Supply, higher absolute voltage VBAT1

BJ6 VBAT2 Battery Supply, lower absolute voltage VBAT2

BJ7 +5 V Five volt analog supply Vcc

BJ8 +3.3 V 3.3-V digital supply 3.3 V

BJ9 DGND Digital ground, return for the +3.3-V supply DGND

BJ10 AGND Analog ground, return for the +5-V supply. AGND

BJ11 BGND Battery ground BGND

BJ16 Ring In Ringing voltage source Ring in

BJ17 Ring Return Ringing voltage return Ring return