CHAPTER

3

Zarlink Semiconductor Inc.

2JUMPERS AND BOARD OP-

TIONS

2.1 DEVICE SELECTION JUMPER BLOCK

The 44-pin TQFP package evaluation board supports both the Le58QL021 and Le58QL061

QLSLAC devices. The pin-outs of both devices are identical when the being run in the PCM mode.

Therefore, the shunt blocks can be left in their default position on JR1 (i.e., row A shorted to row B).

When in the GCI mode, seven signal names for the Le58QL061 device change, but not their pin

assignment.

2.2 JUMPER BLOCKS JM1 – JM4

These jumpers are used to select different series capacitor values, or to select a direct DC

connection to the VOUT connector from the QLSLAC device’s analog output pins. Two capacitor

values (100 nF and 1.0 µF) are provided on the board. The table below shows the jumper

connection options.

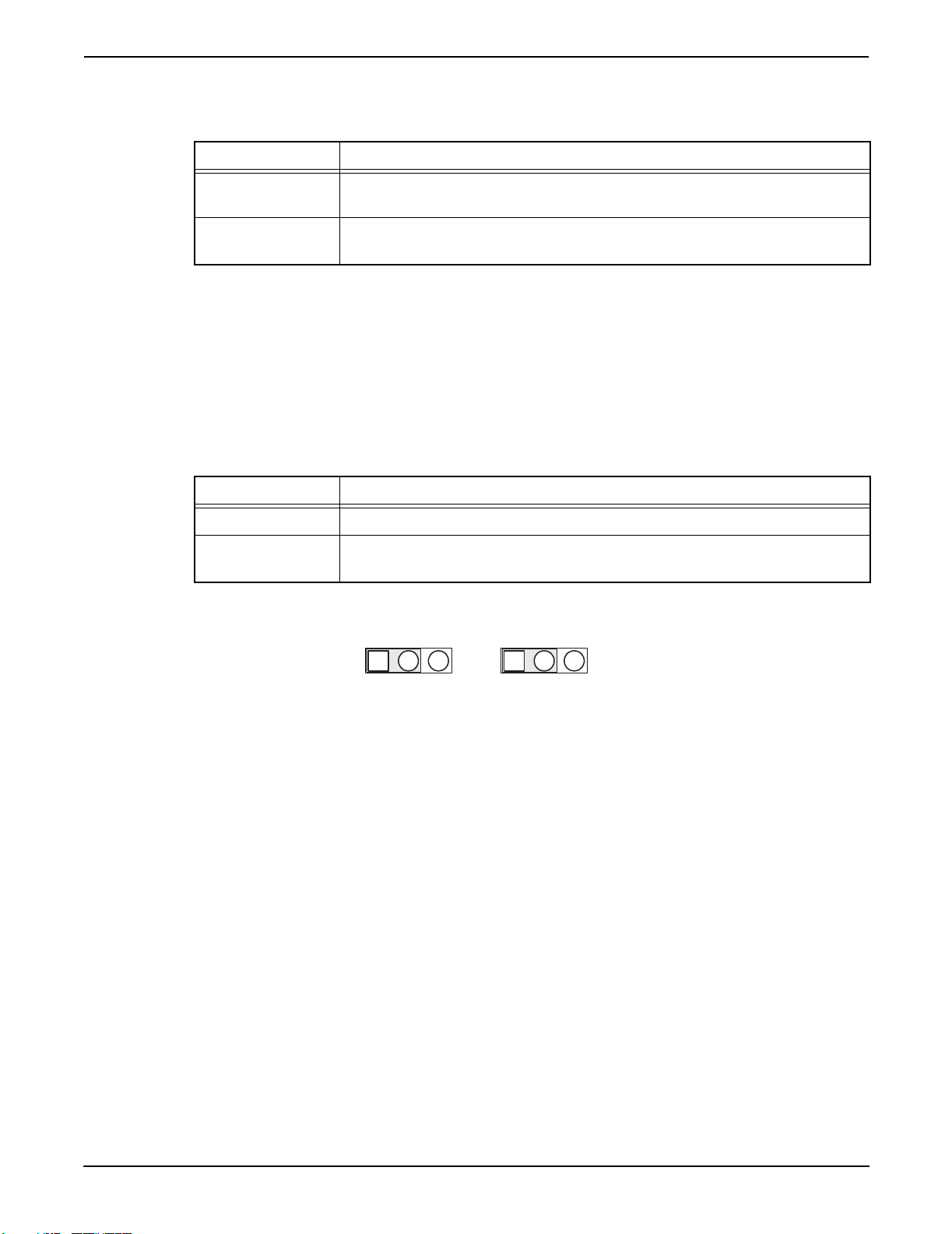

The default position of the shunt, when shipped from the factory, and the pin numbering of the

jumper is shown in Figure 2–1:

Figure 2–1 Jumper Blocks JM1 – JM4

2.3 JUMPER JM5

The QLSLAC device’s internal digital signal processor (DSP) operates from an internal master

clock. In the PCM/MPI mode, the master clock can be provided from the external MCLK input or the

device may internally derive the signal from the PCM (PCLK) clock input. In GCI mode the master

clock is derived from the DCL pin. If the internal clock is derived from PCLK, the MCLK/E1 pin can

be used as an E1 output to control Zarlnk SLIC devices having multiplexed switchhook and

ground-key detector outputs. Selection of the MCLK/E1 pin’s MCLK input or E1 output operation is

established by device programming. (Refer to Zarlink SLIC device data sheets and the QLSLAC

device data sheets for explanations and use of the E1 function.)

The JM5 jumper selects the board connection options to the QLSLAC device’s MCLK/E1 pin. When

this jumper is set for the E1 function, the MCLK/E1 pin of the QLSLAC device connects to the H1,

H2, H3, and H4 headers that supply the control input/output to an Zarlnk SLIC Device Evaluation

Board. When the jumper is set to the MCLK function, the MCLK/E1 pin connects to the MCLK signal

Table 2–1 JM1 – JM4 Jumper Connection Options

Output Pin Jumper Pin 1 to 6 Pin 2 to 5 Pin 3 to 4

VOUT1 JM1 DC 100 nF 1.0 µF

VOUT2 JM2 DC 100 nF 1.0 µF

VOUT3 JM3 DC 100 nF 1.0 µF

VOUT4 JM4 DC 100 nF 1.0 µF

1

2

34

5

6

Place shunt between pins 2 & 5 when

connecting to a Zarlink SLIC device.

Place shunt between pins 3 & 4 when

testing the board in a standalone mode.