Advanced Micro Computers Am96/4016 User manual

Advanced

Micro

Computers

Distributed by

Advanced Micro Devices

Am96/4016

AmZ8000 Evaluatiion Board

User's Manual

--

REVISION RECORD

--

REVISION DESCRIPTION

01

Preliminary

Issue

(7/27/79)

f--

A

Manual

Released

--

(11/8/79)

--

£

J.)

f'

/P

()

t-t/

U'

tA

tfflyr

DN

L

t9

J4P~/1V

(/-.

-i

21

-JMv'--&V)

/

-"

1--

--

--

--

--

I--

1--

--

--

I--

_.

1--

1--

~-

~-

1--

~-

Publication No.

00680131

Address comments concerning

.....

this manual to:

REVISION

LEITERS

I,

0,0

AND

)(

ARE NOT USED

Copyright ©1979

Advanced Micro Computers

Printed

in

U.S.A.

ii

ADVANCED MICRO COMPUTERS

Publications Department

3340 Scott Boulevard

Santa Clara, CA

95051

PREFACE

This

manual

is

written

for

people

who

are thoroughly versed in the use

of

microcomputers.

Many

sections will

contain

more

information than

you

need,

and

we

encourage

you

to

use

the

table

of

contents as a

gui

de

for

your read-

ing.

The

information in

this

manual

is

be-

l i

eved

to

be

accurate

and

compl

ete

at

the time

it

was

pri

nted..

However,

AMC

reserves

the

right

to

change

specifica-

tions

without

notice.

No

responsibility

is

assumed

for

errors

that

might appear

in

this

manual.

No

part

of

this

manual

may

be

copied

or

reproduced in

any

form

without

prior

written

permission

from

AMC.

Publications

related

to

this

manual

include:

AmZ8002

CPU

Data

Sheet

AmZ8000

Family

Interface

Manual

AmZ8000

Data

Book

AmZ8001/2

Processor

Instruction

Set

Am96/4016-ASM

Assembler

Manual

iii

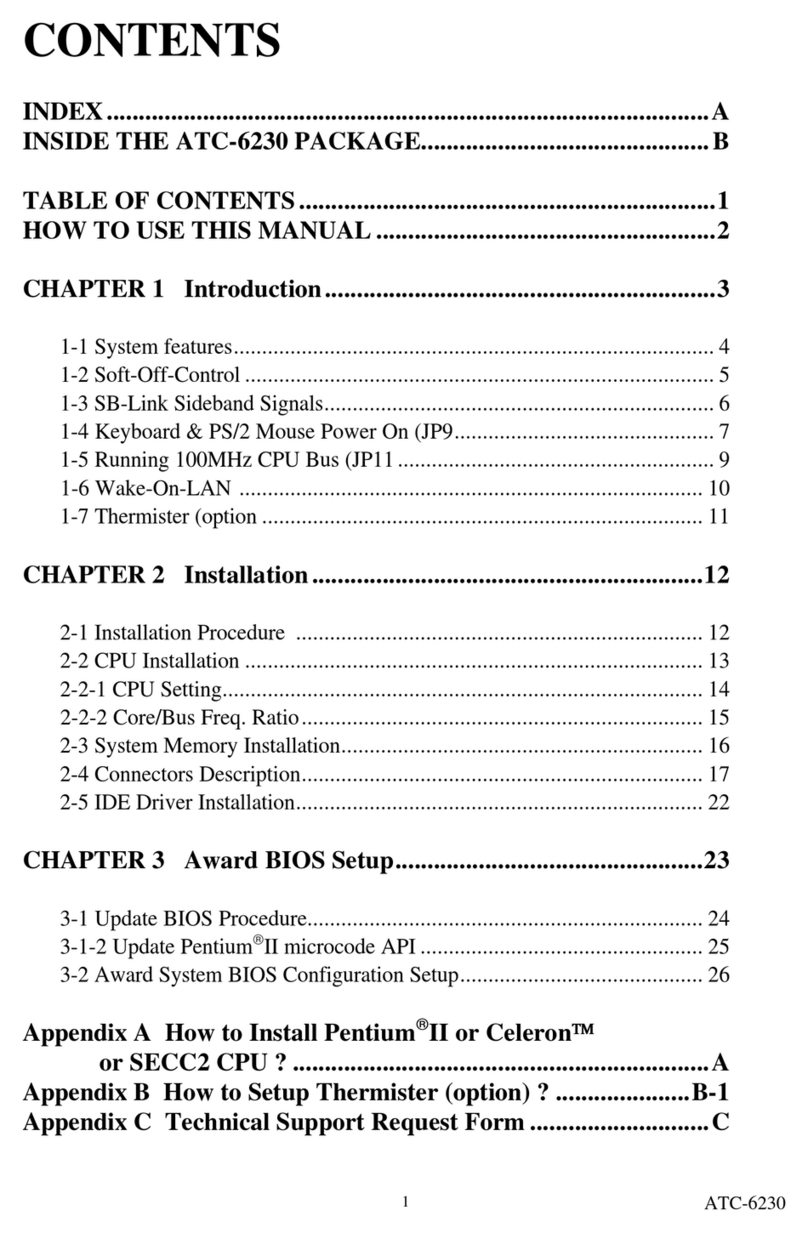

TABLE OF

CONTENTS

1.

INTRODUCTION

Description

••••••••••••••••

l-l

The

CPU

....•......••.....•.

1-3

Memory

•••••••••••••••••••••

1-7

Input/Output

•••••••••••••••

1-7

Software

•••••••••••••••••••

1-8

2.

HARDWARE

INSTALLATION

AND

INTERFACING

Unpacking

and

Inspection•••

2-1

Symbols

••••••••••••••••••••

2-1

Installation

Overview

••••••

2-1

Rom/E-Prom

Sockets

•••••••

2-1

Parallel

I/O

Driver/

Terminators

•••••••••••••

2-1

Edge

Connectors

••••••••••

2-4

Keyboard/Display

Installation

•••••••••••

2-14

Prototyping

and!

Memory-Expansion

Boards

•••••••••••••••••

2-14

AmSYS

8/8

Interconnection

••••••••

2-14

Jumper

Options

••••••••••

2-15

3.

OPERATION

WITH

THE

MONITOR

Overview

of

Operations

•••••

3-1

Monitor Functions

and

User

Controls

••

~

••••••••••

3-1

Mon

i

tor

Commands.,

••••••••••

3-3

(ASM)

Execute Assembler

••

3-3

(B

x,y,z)

Software

Breakpoint•••

~

••••••••••

3-5

(C

n)

Set Carry Flag

•••••

3-5

[(cr)

after

Bor

T]

Single-step

••

~

••••••••••

3-5

(D

n)

Set Decimal-Adjust

Flag

•••••••••

~

••••••••••

3-5

(D

x,y) Display

Mlemory

•••3-5

(E

x)

Hardware

Breakpoint

•.•

u

••••••••••

3-5

(F

x,y,z)

Fill

Memory

••••

3-5

(G

x)

Execute

Program

••••

3-6

(H

n)

Set Half-Carry

Flag

3-6

(LOAD

d:file,x)

Down

Load

••••••••••••••••••••

3-6

(M

x,y,z)

Move

Memory

••••

3-6

(NM)

Enter

Normal

Mode

•••3-6

(P

n)

Set

Parity

Flag

••••

3-6

(P

=

x)

Fill

Program

Counter

•••••••••••••••••

3-6

(RHn

=

x)

Fill

High-

Byte

Register

•••••••••••

3-6

(RLn

=

x)

Fill

Low-

Byte

Register

•••••••••••

3-6

(Rn

=

x)

Fill

Word

Register

••••••••••••••••

3-6

(SAVE

d:file,x,Y)

Up

Load

•••••••••••••••••

3-6

(SM)

Enter

System

Mode

•••3-7

(S

n)

Set Sign Flag

••••••

3-7

(S

x)

Display

and

Substitute

Memory

•••••••

3-7

(T

m,n)

Trace

••••••••••••

3-7

(V

n)

Set Overflow Flag•• 3-7

(

X)

Display

All

Registers

•••••••••••••••

3-7

(XF)

Display Flags

•••••••

3-7

(X

n)

Display

Word

Reg

i

ster

••••••••••••••••

3-8

(XP)

Display

Program

Counter

•••••••••••••••••

3-8

(Z

n)

Set

Zero

Flag

••••••

3-8

Monitor

I/O

Support

for

User

Programs

•••••••••••••

3-8

AmSYS

8/8

Up/Down

Loading

••••••••••••••••••

3-10

4.

PRINCIPLES

OF

OPERATION

Power-Up

Sequence

••••••••.•

4-1

CPU

Functions

••••••••••••••

4-1

Bus

Structure

••••••••••••••

4-2

Memory

•••••••••••••••••••••

4-4

Peripheral

Decoding

••••••••

4-4

5.

PERIPHERAL

PROGRAMMING

Parallel

1/0

•••••••••••••••

5-1

v

Serial

1/0

•••••••••••••••••

5-3

Counter/Timer

••••••••••••

~.5-7

Appendixes

A.

CPU

Bus

Buffering

Characteristics

at

P2

•••••

A-l

B.

ASCII

Character Set

••••••••

B-l

C.

Service Parts

and

Schematics

••••••••••••••••

C-l

Figures

1-1

Board

Layout

•••••••••••••

1-2

1-2 Block

Diagram

•••••••••••

~1-5

1-3 Standard

Configurations.~1-6

1-4 Memory-Addressing

Potential

••••••••••.••••

1-8

2-1

Edge

Connectors

and

Ie

Sockets

•••••••••••••••••

2-2

2-2 Connecting

to

the

AmSYS

8/8

•••••••••••••••

2-7

2-3 Connecting

to

Keyboard/

Display Console

•••••••••

2-8

2-4

Jumper

Option

••••••••••••

2-9

3-1

Memory

Address

••••.••••••

3-2

4-1

IOR*

and

lOW

Decoding

••••

4-3

4-2

Bus

Structure

••••••••••••

4-3

4-3 Customizing Off-Board

Memory

References

•••••.•

4-5

Tables

1-1

Specifications

••.••.••••.

1-4

2-1

Rom/E-Prom

Addresses

and

Sockets

•••••••••••••

2-3

2-2 Driver/Terminators

for

Parallel

Ports

••••••••••

2-3

2-3 Other Driver/Terminator

Circuits

for

P3

•••••••••

2-3

2-4

PI

Connector Pins

••••••••

2-5

2-5

P2

Connector Pins

••••••••

2-6

2-6

P3

Connector Pins

•••••••

2-11

2-7

P4

Connector Pins

•••.•••

2-12

2-8

P5

Connector Pins

•••••••

2-12

2-9

P6

Connector Pins

•••••••

2-13

3-1 Monitor

Command

Summary

••3-4

3-2 Monitor

I/O

Control

Block

••••••••••••••••••••

3-9

4-1 Peri pheral

Addresses

•••••••••••

4-6/4-7

5-1

Am8255A

Operation

Control

Word

Format

•••••

5-2

5-2

Am8255A

Bit Set/Reset

Control

Word

Format

•••••

5-2

5-3

Am8255A

Address

••••••••••

5-4

5-4

Am9551

Asynchronous

Mode

Control

Code

•••••••

5-4

5-5

Am9551

Control

Command

•••

5-5

5-6

Am9551

Synchronous

Mode

Control

Code

•••••••

5-5

5-7

Am9551

Addresses

•••••••••

5-6

5-8

Am9551

Status Register

•••

5-6

5-9

Am8253

Control

Byte

Format

••••••••••••••••••

5-9

5-10

Am8253

Control Byte

Definition

•••••••.••••••

5-9

5-11

Am8253

Control

Byte

to

Latch

Count

•••••••••

5-10

5-12

Am8253

Addresses

••.•.•••

5-10

vi

CHAPT'ER 1

INTRODUCTION

1-1.

DESCRIPTION

The

Am96/4016

Evaluation Board

is

a

com-

p1

ete

si

ngl

e-board

mi

crocomputer bui 1t

around

the

new

16-bit

AmZ8000

micropro-

cessor.

Used

with a

standard

CRT

or

the

low-cost

keyboard/display

console

available

as

an

option,

it

provides

an

excellent

means

,of

testing

the

advanced

capabil

ities

of

this

remar~kably

ver-

sat

i1e

CPU.

Used

wi

th

Advanced

Mi

cro

Computer's

new

AmSYS

8/8

Development

System,

the

entire

AmZ8000

instruction

set

can

be

macroassembled

to

create

very powerful programs for' executi

on on

the

Evaluation Board.

The

fully

assembl

ed

and

tested

board

h~s

the

following

features:

Standard Features

•

AmZ8002

CPU

(non-segmented)

• 8

kilobytes

of

dynamic

RAM,

expand-

able

off-board

•

Up

to

12

kilobytes

of

ROM

or

E-PROM,

expandable

off-board

•

4-kilobyte

ROM

Monitor, with

break-,

point,

single-step

and

up/down-load

commands

•Buffered

CPU

busava

i1

ab

1e

at

edge

of

board

•

Two

programmable

serial

I/O

ports

(RS232C

and

20mA)

• A programmable

counter/timer

channel

associated

with one

serial

port

•

24

programmable

paral'lel

I/O

lines

(three

8-bit

ports)

•

Fits

in Multibus·t

or

iSBCt

card

cage

tTrademarks

of

Intel

Corporation

Optional Features

•One-pass Assembler

in

ROM

•Keyboard/Display console

•

CRT

termi nal

•Universal

prototyping

board

•

CPU-bus

backplane

(2

or

3

slots)

•Six-board card cage

•

64-kilobyte

memory

expansion

•

Compl

ete

AmSYS

8/8

Development

Sys

...

tern, with di

skette

storage,

i

nter-

face

utilities

and

PASCAL~like

mac-

roassembler

for

the

ArnZ8000

series

Programs can

be

entered

and

executed in

either

the

stand-alone

or

Development

System confi

gurat

ion.

Speci

ali

zed ci

r-

cuits

or

external

expan~ion

boards can

a1so

be

attached

in

ei

ther

mode.

The

entire

CPU

bus

is

buffered

and

brought

to

the

edge

of

the

board

for

intercon-

'nection,

as

are

extra

I/O

ports

for

serial

and

parallel

transfers

on

the

data

bus.

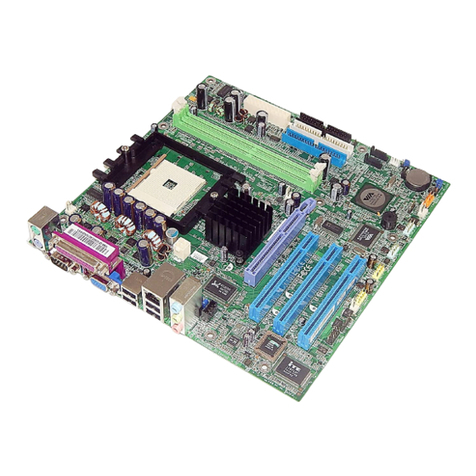

Fi

gure 1-1

ill

ustrates

the

board 1ay-

out.

The

lower

two

edge connectors

are

physically

compatible with

the

Multibus

standard,

although

the

PI

edge connec-

tor

uses only

power

and

ground in

the

standard

Multibus card cage.

All four top edge connectors

on

the

board

are

used

for

110.

The

P3

connec-

tor

has

24

programmable

lines

divided

into

three

8-bit

ports

for

data

and

hand

shaking.',

The

P4

connector

is

a1

so

parallel

but designed

specifically

for

the

optional

keyboard/display

console

that

can

be

attached

to

the

Evaluation

Board.

The

P5

and

P6

connectors both

carry

programmable

lines

for

asynchro-

nous

or

synchronous

seri

a1

data.

The

P5

connector al

so

carri

es

control

I/O

for

an

on-board programmabl e

counter/

timer

channel.

1-1

SERIAL

I/O

SERIAL

I/O

I I I I

PARALLEL

I/O

P3

KEYBOARD

DISPLAY

I I

P4 P5

P6

50-pin

IAm

8255A

rDriver/Terminator

. . Sockets

8Kilobytes

Am 9050C

RAM

~M

4716 EPROM

~itor

and Assembler

86-pin

P1

POWER

AND

GROUND

Break

Switch

N

8

00

N

E

<!

60-pin

P2

CPU

BUS

1-2

Figure

1-1.

Board

Layout

The

AmZ8002

CPU

is

in

the

center

of

the

board.

At

the upper

right

are

the

two

Am9551

USARTs

for

serial

I/O, surround-

ing the

Am8253

counter/timer

circuit

which

clocks them.

The

Am8255A

parallel

I/O

circuit

is

in the upper

left,

next

to

six

sockets

for

dri

VE~r

/terminators

on

the

parallel

port

lines.

Sixteen

Am9050C

dynamic

RAM

circuits

provide

the 8 ki1obytes of user

memory.

The

Monitor

and

optional Assembler programs

are contained in

six

Am4716

E-PROMs.

Figure 1-2

shows

ablock diagram of the

board.

The

system buses (address, data

and

control)

emerge

from

the

CPU

and

service

all

circuits,

terminating

at

the

P2.

The

address

and

data buses,

which

are multiplexed in

the

CPU,

are

separated

into

two

separate

16-bit

buses

on

the board.

The

diagram

shows

more

clearly

the

difference

between the

P5

and

P6

serial

I/O

ports;

one

has

a

counter/timer channel

available

and

the

other

can

be

changed

from

RS232C

to

20mA

current-loop

(TTY)

interfacing.

Memory-expansion boards

and

prototyping

boards carrying

any

AmZ8002-compatible

circuits

(such

as

DMAs

or

even

multiple

CPUs)

can

be

attached

at

P2.

Special-

i

zed

circuits

can

al

so

be

attached

at

P3,

P5

and

P6.

P5

is

particularly

use-

ful

for

event-counting process control

circuits

or foreign host computers.

Figure 1-3

illustrates

the range of

standard plug-in configurations sup-

ported

by

the boardls Monitor program.

If

attachments

to

the board are

limited

to

anyone

or

more

of these

three

choices,

application

programming

and

execution

can

begin immediately without

having

to

program

the

I/O

circuits.

When

the

AmSYS

8/8

is

attached

for

up/

down

loading of programs, the Develop-

ment

System

IS

console

can

commun

icate

with

the

Eval

uation

Board

to

control

all

functions.

The

Development

System

contains a

com-

prehensive

set

of hardware

and

software

resources

to

fully

utilize

AmZ8000

cap-

abi 1

it

i

es.

The

system incl udes

dua

1

diskette

drives,

64K

bytes

of

RAM,

se-

rial

and

parallel

ports,

and

amulti-

master bus. Existing

programming

sup-

port includes a

CPM-compatible

oper-

ating

system with linking

loader,

ed-

itor

and

debugger

and

a

PASCAL-like

AmZ8000

macroassemb

1

er

,

8080

macro-

assembler

and

AmZ8000

translator.

High-level languages, including

PASCAL,

are

available.

See

the

AmSYS

8/8 bro-

chure

for

more

details.

Table 1-1 gives a

summary

list

of spec-

ifications

for

the Evaluation

Board

1-2.

THE CPU

The

AmZ8002

microprocessor

is

a

regis-

ter-oriented

CPU

with exceedingly well

organized minicomputer-like

architec-

ture.

Si

xteen general-purpose regi

s-

ters,

each of

them

two-bytes (one 16-

bit

word)

wide, are

available

to

the

user.

Over

100

instructions,

and

400

combinations of

instructions,

can

be

used

to

manipulate data between the

CPU

registers,

memory

and

I/O.

The

CPU

can

operate in

two

modes--

system

and

normal--with separate

relo-

catable

stacks

for

each

mode.

This

al-

lows

a di

st

incti

on

between pri

vi

1

eged

and

protected

instructions,

as well as

great

flexibility

in

allocating

the

system1s use

of

memory.

In

either

mode,

ten

status

conditions are con-

tinuously reported:

1. Internal operation

2.

Instruction

fetch,

first

word

3.

Instruction

fetch,

subsequent

word

4.

Memory

request,

data

5.

Memory

request,

stack

6.

Memory

refresh

cycle

7.

I/O

cycle

8.

Interrupt

acknowledge, non-maskable

9.

Interrupt

acknowledge, non-vectored

10.

Interrupt

acknowledge, vectored

1-3

CPU

Time

Base

Serial

I/O

Parallel

I/O

RAM

Memory

ROM

Space

Counter/Timer

Power

Dimensions

TABLE 1-1. SPECIFICATIONS

AmZ8002

(non-segmented)

4MHz

crystal

oscillator

Two

RS232C

serial

ports with software-pro-

grammable

baud

rates.

One

port jumper-

selectable

for

20mA

current-loop

(TTY)

oper-

ation.

24

parallel

I/O

lines

(three

8-bit

ports).

Also

provides interconnection to

AmSYS

8/8

De-

velopment System.

8K

bytes of on-board

dynamic

memory;

CPU

re-

freshed

(transparent).

12K

bytes of

ROM/EPROM

space provided in

six

sockets;

ROM

monitor occupies

two

sockets.

Three

16-bit

programmable

interval

counter;

two

counters

used

for

serial

I/O

baud

rate

control;

third

counter

available

to user.

-12VDC

@.085A,

+12VDC

@.06A,

+5VDC

@

1.65A

(without optional keyboard/display console),

or

+5VDC

@

2.0A

(with optional

keyboard/display console).

12.0

11

(305

rrrn)

x6.75

11

(172

rnm);

MULTIBUS

form

factor

with six

edge

connectors

(PI

through P6).

Memory

Addressi

ng

ROM

space:

RAM

space:

0-2FFF(H)

4000-5FFF(H)

1-4

Environmental

Conditions

Edge-of-Card

Connectors

Monitor

o

to

55°C

ambient in

free-air

space with

relative

humidity

to

90%

without condensation.

PI: 86-Pin

for

power, ground,

and

initialize.

P2:

60-Pin

CPU

bus

P3:

50-Pin

parallel

I/O

for

up/down-load

from

AmSYS

8/8

Development

System.

P4:

26-Pin

interface

for

optional keyboard/

display

board.

P5:

26-Pin

RS232

and

counter/timer

interface.

P6:

26-Pin

RS232

or

20mA

current loop for

CRT

or

TTY

console.

4K

ROM

monitor included

at

addresses

O-OFFF(H)

Assembler Optional

ASCII,

one-pass,

line

assembler in

ROM

Up/Down-Load

Capability

Can

be

plugged into

AmSYS

8/8

Development

Sys-

tem

to

provide up-load

and

down-load

capabil-

ity.

Can

also

by

used

with

other

computer sys-

tems

to

execute

AmZ8000

code.

Optional

Keyboard/

Display

56-key keyboard with 20-character alphanumeric

LED

display.

Same

physical

form

as

Am96/4016

Evaluation

Board

with attaching

standoff

con-

nectors

and

interconnection ribbon

cable.

P6

P5

P4

r

,~

1rI I

,~

I

~.

,

~

/Keyboard RS232C RS232C

Interface Interface or

20mA

Interface

.-

•,,

,II

,.

,+,

-8253

9551

9551

ICounter Serial Serial

Timer

I/O I/O

-jjj

-

+2

..

,~

,,1

~

j

.1

4716 9050C

EPROM RAM

I

+12V

-'12V

HiV

L_~.!~J

P1

P3

Ie

[

Jrivers

Termi-

nators

~

4MHz

I---

Clock

K

8002

CPU

Figure

1-2.

Block Diagram

1-5

Use

one

or

more

of

these

options

CRT

I I

'11111111111111

Flat Cable

Keyboard/Display

P3

Am

SYS

8/8

Development

System

Flat cable

to

Development

System CPU board

for

~

control

and

up/down

loading

P1

P2

i

Power and

Ground

CPU-bus backplane board (2

or

3

slots)

for

interconnecting external

prototyping

or

memory-expansion

boards

Figure

1-3.

Standard Configurations

1-6

Only

three

of

these

status

outputs (2,

6

and

7)

are

needed

by

the Evaluation

Board's

internal

functions,

but

all

are

available

at

the

P2

edge

connector.

The

interrupt

and

trap

structure

is

part

icul arlypowerful,

wi

th

very

fast

response

to

externa1

dev

i

CE~S

and

i

1-

legal conditions.

Special

instructions

and

har'dware

fea-

tures

support multiprogramming

and

multiprocessing.

In

an

asynchronous

cha

in of

CPUs,

cri

t i

ca

1l"esources

can

be

shared without

sacrificing

through-

put.

1-3.

MEMORY

The

Eval

uati

on

Board's

dynami

cRAM

is

refreshed

by

the

CPU.

Additional

memory,

ei

ther

dynami

cor'

stat

i

c,

can

be

added

off-board through

the

P2

edge

connector.

AMC

will supply a

64-kilo-

byte

memory-expans

i

on

board

for

thi

s

purpose

which

has

self-contained

re-

freshing.

There

is

aprovision

for

substituting

off-board

memory

during

accesses

to

the

on-board

mE~mory'

sad-

dress space.

Depending

on

your use

of

CPU

functions,

avery 1arge

amount

of

memory

can

be

used.

The

CPU's

16

address

lines

can

directly

access

64

kilobytes.

However,

if

the various

distinctions

between

operating

mode

(system

and

normal)

and

memory-access

status

(instruction,

data

and

stack) are used

to

differentiate

memory

resources,

up

to

384

kilobytes

can

be

addressed as

illustrated

in

figure

1-4.

.

1-4.

INPUT/OUTPUT

Memory

space

and

I/O

space are

differ-

entiated

by

amemory-request 1i

ne

and

other

status

outputs

from

the

CPU.

The

CPU

can

use

16-bit

I/O

port addresses,

allowing

up

to

64K

ports,

although in

the Evaluation board implementation

the

upper four address

bits

are not decoded

and

often the lower

one

or

two

address

bits

are

used

for

sub-addressing within

peripheral

circuits.

The

Evaluation

Board

also implements

onl

y8-bit

I/O

transfers

on

the

four

top

edge

connectors

(P3

through P6).

These

are

the

lower 8

bits

on

the

data

bus.

The

24

parallel

I/O

lines

of

the

Am8255A

circuit

at

P3

can

be

configured

to

transfer

data in a

variety

of ways,

with or without handshaking.

In

the

standard

configuration,

this

edge

con-

nector

is

used

for

up/down

loading be-

tween the

AmSYS

8/8

Development

System

and

the Evaluation Board.

The

circuit

has

a

bi

t

set/reset

functi

on

that

i

n-

creases the

efficiency

of handshake

software.

The

sockets provided for

driver

or terminator

circuits

allow

further

characterization

of

these

ports

for

special

applications.

Ground

lines

are i

nterl

eaved

wi

th

signa1 1i

nes

for

better

noise

immunity

at

this

edge con-

nector.

The

two

Am9551

USART

(un

iversa1syn-

chronous/asynchronous

receiver/trans-

mitter)

circuits

attached

to

the

P5

and

P6

edge

connectors

can

be

programmed

for

abroad range of

full-duplex,

doubly-buffered communication proto-

cols,

with

many

automatic overhead fea-

tures.

The

baud

rate

is

contro

11

ed

by

two

of the

three

programmable channels

in

the

Am8253

counter/timer

circuit.

As

ment

i

oned

above,

no

programmi

ng

of

I/O

circuits

is

necessary

when

the

Evaluation

Board

is

used in

one

of

the

standard configurations

ill

ustrated

in

figure

1-3.

The

Monitor program will

initialize

these

circuits

for

you

•

1-7

1-5.

SOFTWARE

The

Evaluation Board's

ROM-based

Moni-

tor

program

provides

compl

ete

system-

initialization

functions

and

over

two

dozen user

commands

for

access

to

CPU

registers

and

memory.

It

features

breakpoint,

single-step

and

trace

func-

tions,

as well

as

up-load

and

down-load

functions

for

use

wi

th

the

AmSYS

8/8

Development

System.

Any

AmZ8000

i

n-

struction

whether privileged (system

mode)

or protected (normal

mode)

can

be

entered in

hex

format

us

i

ng

only

the

Monitor.

The

optional

ROM-based

mnemonic

Assem-

bler

simplifies

instruction

entry.

Most

of the

full

ArnZ8000

instruction

set

can

be

used

with

this

one-pass

line-by-line

Assemb

1

er,

wh

i

ch

a1

so

supports forward

symbolic

references.

It

is

an

excellent

tool

for

gai

ni

ng

afeel of

AmZ8000

i

n-

structions

without

the

need

for

a

com-

plete

macroassembler,

which

is

avail-

abol

e

on

the

AmSYS

8/8.

The

full

CPU

instruction

set

can

be

used

to

create

very powerful appl ica-

tion

programs.

The

110

basic

instruc-

tions

have

permutations around operand

addressing

modes,

plus autoincrement

and

autodecrement

facilities.

Code

written

for the

ArnZ8002

is

source-

compatible with the

AmZ8001

micro-

processor

Most

instruct

ions are between

one

and

three

16-bit

words

in length.

Instruc-

tions

and

hardware are

available

to

operate

on

bits,

4-bit

digits

(BCD),

8-bitbytes, 16-bit

words

,32-bitlong

words,

64-bit

quad

words, byte

strings

and

word

strings.

String

instructions

are auto-incremen-

ting

or auto-decrementing block

trans-

fers.

The

strings

can

be

up

to

64

kilo-

bytes in

length,

the

entire

directly-

addressabl e

memory,

and

the

transfers

are

interruptible.

It

is

this

facility

that

gi

ves

the

CPU

an

i

ntri

ns

ic

DMA

capability.

MODE:

STATUS:

SYSTEM

MODE

/1\

CODE

DATA

STACK

/\

NORMAL

MODE

/1\

CODE

DATA

STACK

/\

64

Kilobytes 64

64 64

Kilobytes Kilobytes Kilobytes 64

64

Kilobytes Kilobytes

Figure

1-4.

Memory-Addressing Potential

1-8

CHAPTER 2

HARDWARE~

INSTALLATION AND INTERFACING

2-1.

UNPACKING

AND

INSPECTION

Upon

receipt

of

this

equipment, inspect

both the equipment

and

the shipping

carton immediately for evidence of

dam-

age

during

transit.

If

the

shipping

carton

is

damaged

or

water-stained,

request the

carrier's

agent

to

be

pre-

sent

when

the carton

is

opened.

If

the

carrier's

agent

is

not present

when

the

carton

is

opened

and

the contents of

the carton are

damaged,

save the carton

and

packi

ng

materi

al

for

the

agent's

inspection.

Shipping

damages

should

be

reported immediately

to

the

carrier.

Do

not attempt

to

servi

CE~

the board

yourself

as

this

will

'Voi'd

the war-

ranty.

2-2.

SYMBOLS

Aspecial

symbolism

is

used in

this

and

subsequent

sect

ions

to

denote

act

ive-

low

signal

levels.

An

asterisk

(*)

fol-

lowing asignal

name,

rather

than abar

over the

name,

means

that

the signal

is

active-low

(negative-trUE~).

For

exam-

ple,

WAIT*

is

active

when

its

voltage

potenti

al

is

low.

2-3.

INSTALLATION

OVI::RVIEW

Figure 2-1

illustrates

the hardware

connectors

and

sockets

that

may

require

setup' before the

boa

rd

can

be

used.

These are the

six

edge connectors,

PI

through P6,

pl

us

sockets

for

ROM

or

E-PROM

and

the sockets

for

parallel-I/O

driver

or terminator

circuits.

Each

of

these

groups

is

discussed

individually

below.

NOTE

When

one

of the standard config-

urations

illustrated

in Figure

1-3 has

been

ordered

from

AMC,

only the following

installation

connections

need

be

considered:

Edge

External

Connection Connection

P3

AmSYS

8/8 Development Sys-.

tem

CPU

board (P3), as

il-

lustrated

in

figure

2-2.

P4

Keyboard/LED

Display

Board

(Am96/4016-KBD),

as

illus-

trated

in

figure

2-3.

P6

CRT

or

other

RS232C

term-

ina1•

2-4.

RaMIE-PROM

SOCKETS

The

board contains

six

sockets

for

fixed-address

ROM

or

E-PROM.

All

boards are shi

pped

wi

th

at

1

east

two

E-PROMs

installed,

which

contain the

4-kilobyte

Monitor program.

If

you

ordered the optional

line-by-line

8-

kilobyte Assembler, the remaining four

E-PROM

sockets will also

be

filled.

Table

2-1

is

therefore

only advisory

and

will not

require

installation

of

additional

ICs

unless

you

intend

to

alter

the use of

ROM

space or

install

the

Assembler

circuits

later.

2-5.

PARALLEL

1/0

DRIVER/TERMI

NATORS

When

the board

is

ordered,

the

driver

and

terminator

circuits

listed

in

table

2-2 are provided.

2-1

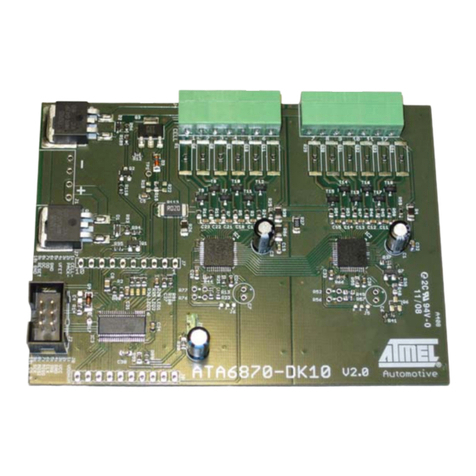

DRIVER/TERMINATOR

SOCKETS

FOR

Am

8255A

PARALLEL

I/O

(U2-U7)

Keyboard/

Parallel Display

Serial Serial

I/O

Console

I/O

I/O

P3 P4

P5 P6

50-pin

86-pin

P1

Power and Ground

'------

ROM/EPROM

(U57-U62)

60-pin

P2

CPU

Bus

2-2

Figure 2-1. Edge Connectors and

IC

Sockets

TABLE

2,-1.

ROM/EPROM ADDRESSES

AND

SOCKETS

Program

Monitor

Assembler

Addresses Socket #

o -

OFFF

(even)

U57

o -

OFFF

(odd)

U60

1000

-

IFFF

(even)

U58

1000

-

IFFF

(odd)

U61

2000

-

l~FFF

(even)

U59

2000

-

2FFF

(odd)

U62

-

TABLE 2-2" DRIVER/TERMINA.TORS FOR PARALLEL PORT

Device

74LS3j'

74LS37

74LS3j'

i

SBC902

iSBC902

i

SBC902

Function Socket #

-

Dr'j

ver

U2

Dr'j

ver

U3

Dr'j

ver

U4

Tenni

nator

U5

Tenni

nator

U6

Tenni

nator

U7

-

TABLE 2-3. OTHER DRIVER/TERMINATOR CIRCUITS FOR

P3

Drivers Terminators

7438,74LS38

7437

,

7~~LS37

7432, 7

i~LS32

7426,

7i~LS26

7409,

7i~LS09

7408,

7i~LS08

7403,

71~LS03

7400,

71~LSOO

Intel

Intel

Nat

ional

National

National

iSBC

901

iSBC

902

BLC

901

BLC

902

BLC

903

2-3

Non-standard uses

of

the

P3

edge con-

nector

may

requi

re

di

fferent

devices

for

these

sockets.

Some

of

the

pos-

sible

devices are

listed

in

table

2-3.

Alternatively,

the

sockets

can

be

jump-

ered

for

direct

connection

to

the

Am8255A

pins.

2-6. EDGE

CONNECTORS

A

minimum

of

two

edge

connectors

must

be

used

to

operate

the

board.

Power

(+

I2V,

-12V,

+5V)

and

ground

must

be

supp1

ied through

the

PI

connector. A

system console

must

also

be

connected

on

one

of

the

remaining connectors:

either

P4

for

the

AMC-supp1ied

key-

board/display console

or

P6

for

auser-

supplied tennina1.

Many

additions

to

these

required con-

nections are

possible,

as indicated in

the

list

of

edge-connector

characteris-

tics

and

applications

below. This

list

is

norma

11

ynot needed

if

you

are in-

stall

ing astandard configuration i1-

1ustrated

in

figure

1-3.

Note

that

connectors

PI

and

P2

have

their

odd-numbered

pins

on

the

com-

ponent

side

of

the

board, whereas

the

remaining connectors

have

them

on

the

solder

side.

The

abbreviation

N/C

in

the

pin-connection

lists

means

no

con-

nection.

PI

-

an

86-pin connector physically

(but not

electrically)

com-

patible

to

the

Multibus

and

i

5BC-80

formats.

It

is

used

only

for

power

and

ground, ex-

cept

that

pi

n

14

can

be

used

for

external

initializing

(re-

set)

when

jumpered

for

thi

s

function (see

figure

2-4).

The

pi

nconnections are

shown

in

table

2-4.

2-4

P2

- a 60-pin connector

physically

compatible with

the

Mu1tibus

and

i

5BC-80

formats.

It

car-

ries

buffered

signals

from

all

CPU

lines

except

+5V,

which

is

on

the

PI

connector,

and

DE-

COUPLE

wh

i

ch

is

not used

on

the

AmZ8002.

The

address/data

bus

from

the

CPU

is

demu1

t

i-

p1exed

into

separate

address

and

data buses.

The

CPU's

RE5ET*

line

is

connected

directly

to

the

RST*

1ine

on

P2, although

RST*

also

resets

the

Am9551

USARTs

and

the

Am8255A

PIO.

One

additional

line,

INH*

is

used

to

control

addressing

of

on/off-board

memory.

This connector

is

used

to

in-

terface

aprototyping board

and/or external

memory

boards.

An

optional backplane

is

available

for

this

purpose.

If

the

CPU

is

disabled via

the

BU5RQ*

input,

an

off-board de-

vice

can

take control over

most

of

the

signals

on

thi

s

connector

to

access

memory

and

peripherals

on

the

Evaluation

Board.

The

pin connections

are

shown

in

table

2-5.

P3

- a 50-pin connector

to

the

six

driver/terminator

sockets of

the

Am8255A

parallel

I/O

cir-

cuit.

The

24

active

lines

are

divided

into

three

8-bit

ports

(addresses

FFO,

FFI

and

FF2,

where

the

upper four address

bits

are not decoded).

Each

port

can

be

programmed

inde-

pendently

for

input

or

output

to

match

the

functions

of

the

driver

or

terminator

ICs

that

you

insert

in sockets

U2

through

U7.

This manual suits for next models

1

Table of contents