Allegro MicroSystems A8600 User manual

Description

Designed to provide the power supply requirements of next

generation car audio and infotainment systems, the A8600

provides all the control and protection circuitry to produce

four high current regulators, each with ±1.5% accuracy. The

A8600 includes control circuitry to implement three adjustable,

asynchronous buck regulators with integrated MOSFETs. Also,

the A8600 provides the control circuitry, gate drivers, and

current sensing to implement a synchronous buck controller

with external MOSFETs. In standby mode, the A8600 draws

less than 50 µA from VIN of 12 V while employing pulse

frequency modulation (PFM) to deliver 3.3 V/40 µA via the

always-on regulator, SW1. The always-on regulator operates

down to at least VIN of 3.6 V (VIN falling).

Features of the A8600 include: an EN/SYNC input to either

turn the A8600 on/off or increase/decrease the base pulse

width modulation (PWM) frequency, four adjustable soft-start

times, and four external compensation pins. Output voltage

monitoring of switchers SW2, SW3, and SW4 is provided

by a single, open-drain POK output. In addition, the A8600

provides two high voltage, high-side switches with foldback

overcurrent protection. These two high-side switches actively

block reverse current. The A8600 also provides direct battery

(BU) and switched (accessory) battery (ACC) detectors and

a mute pulse output with an adjustable delay.

A8600-DS, Rev. 4

Features and Benefits

• Four independent, high current switching regulators

• Adjustable 1.0 A/±1.5% always-on asynchronous buck

regulator with an integrated 150 mΩ MOSFET (SW1)

▫ Employs PFM to deliver 3.3 V/40 µA while drawing less

than 50 µA from VIN of 12 V

▫ Operates down to at least 3.6 VIN

• Adjustable 1.5 A/±1.5% asynchronous buck regulator with

an integrated 120 mΩ high-side MOSFET (SW2)

• Adjustable 2.0 A/±1.5% asynchronous buck regulator with

an integrated 110 mΩ MOSFET (SW3)

• Adjustable ±1.5% synchronous buck controller with

integrated gate drivers and current sensing (SW4)

• Fixed 425 kHz, interleaved PWM switching frequency

• EN/SYNC input for PWM frequency scaling

• Adjustable soft-start time for each switching regulator

• All switching regulators provide prebias startup with zero

reverse current

• All switching regulators have overvoltage protection

• External compensation for all switching regulators

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

Package: 48-pin LQFP (suffix JP)

Not to scale

A8600

1.0 A

AVG

/ 2.5 A

PEAK

1.5 A

AVG

/ 2.5 A

PEAK

2.0 A

AVG

/ 2.5 A

PEAK

Switcher 1

(SW1)

Always-On

Adjustable

Output Voltage

Adjustable

Output Voltage

Adjustable

Output Voltage

Adjustable

Output Voltage

Adjustable ILIM

PWM/ PFM

Asynchronous

Buck

Switcher 2

(SW2)

PWM

Switcher 3

(SW3)

PWM

Switcher 4

(SW4)

PWM

Regulator

Asynchronous

Buck

Regulator

Asynchronous

Buck

Regulator

Synchronous

Buck

Controller

BU and ACC

Detectors

Mute Pulse

with Delay

425 kHz

180° Shift

(EN/SYNC)

Charge

Enable and

Synchronization

Pump

High-Side Switch 2

(S2)

High-Side Switch 1

(S1)

1.0 Ω Total

with

Foldback Limiting

1.0 Ω Total

with

Foldback Limiting

Continued on the next page…

Continued on the next page…

Figure 1. A8600 major features

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

2

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

Protection features of the A8600 include pulse-by-pulse current

limit, hiccup mode short circuit protection, asynchronous diode

protection, BOOT voltage protection, undervoltage lockout, over-

voltage protection and thermal shutdown.

TheA8600 is supplied in a low profile 48-pin LQFP package (suffix

JP) with exposed power pad. It is lead (Pb) free, with 100% matte-

tin leadframe plating.

• Power OK (POK) open-drain output with de-glitch

• BU and ACC voltage detectors and comparators

• Mute control with programmable delay

• Two internal high-voltage, high-side NMOS switches

(S1 and S2) with foldback short circuit protection

• High-side switches simultaneously controlled on/off

• High-side switches block reverse current

• Internal charge pump for high-side switch biasing

• Withstands surge voltages up to 40 V

• −40°C to 85°C ambient operating temperature range

• 150°C maximum junction temperature

• Thermally enhanced, surface mount package

Features and Benefits (continued) Description (continued)

Selection Guide

Part Number

Operating Ambient

Temperature Range

TA, (°C)

Package Packing* Leadframe Plating

A8600EJPTR-T –40 to 85

48-pin LQFP with

exposed

thermal pad

1500 pieces per

13-in. reel 100% Matte-Tin

*Contact Allegro™for additional packing options.

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

3

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

Table of Contents

Specifications 4

Absolute Maximum Ratings 4

Thermal Characteristics 4

Pin-out Diagram and List 5

Top Level Block Diagram 6

Typical Application Circuit 6

SW1/2/3 Detailed Block Diagram 7

SW4 Detailed Block Diagram 8

Electrical Characteristics Table 9

General Specifications 9

SW1 Regulator 10

SW2 Regulator 12

SW3 Regulator 14

SW4 Controller 16

S1, S2 Switches 18

BU and ACC Comparators 18

CTMR and MUTE 19

Timing Diagrams 20

SW1 Normal PWM Operation 20

SW1 Low IQ and Low IP Operation 21

SW2/3/4 PWM Operation 22

S1/2 Operation 23

BU, ACC, and Mute Operation 24

Functional Description 25

Overview 25

Reference Voltage 25

PWM Switching Frequency 25

Enable/Synchronization Input (EN/SYNC) 25

BIAS Input Pin, Ratings, and Connections 26

Transconductance Error Amplifier 26

Slope Compensation 26

Current Sense Amplifiers 26

Power MOSFETs 26

BOOT Regulators 27

SW1/2/3/4 Pulse Width Modulation (PWM) Mode 27

SW1 Low IP PWM Mode 27

SW1 Pulse Frequency Modulation (PFM)

and Low IQ Mode 27

Soft Start (Startup) and Inrush Current Control 28

Prebiased Startup 29

High-Side Switches (S1 and S2) 29

BU and ACC Detectors and MUTE Output 31

Power OK (POK) Output 31

Protection Features 32

Undervoltage Lockout (UVLO) 32

Thermal Shutdown (TSDL and TSDH) 32

Pulse-by-Pulse Overcurrent Protection (OCP) 32

Output Short Circuit (Hiccup Mode) Protection 33

BOOT Capacitor Protection 33

Asynchronous Diode Protection 34

Overvoltage Protection (OVP) 34

Application Information 36

Design and Component Selection 36

Setting the Output Voltage (VSWx, RFBAx, RFBBx) 36

Output Inductor (LSWx) 37

Output Capacitors (CSWx) 37

SW1 Low IQ PFM Ripple Calculation 38

Input Capacitors (CINx) 38

Asynchronous Diode (DSWx) 39

Bootstrap Capacitor (CBOOTx) 40

Soft Start and Hiccup Mode Timing (CSSx) 40

SW4 External MOSFET Selections 41

SW4 Current Sense Resistor 41

Compensation Components (RZx, CZx, CPx) 41

A Generalized Tuning Procedure 43

Power Dissipation and Thermal Calculations 44

PCB Component Placement and Routing 45

Pin Descriptions Table 47

Pin ESD Structures 49

Package Outline Drawing 50

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

4

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

Absolute Maximum Ratings1

Characteristic Symbol Notes Rating Unit

OUTx Pins Continuous –0.3 to 40 V

BUI, VIN1/2/3, VINS, SSx, MUTE,

POK Pins –0.3 to 40 V

BIAS, CSP, CSN Pins –0.3 to 7 V

HG4 Pin –0.3 to VIN3 + 7 V

LG4 Pin –0.3 to 8.5 V

BOOTx Pins VINx = VIN1

, VIN2 , VIN3 –0.3 to VINx+7 V

LX1/2/3 Pin to GND VLX1 , VLX2

,

VLX3

Continuous, VINx = VIN1

, VIN2 , VIN3; minimum

voltage is a function of temperature –0.3 to VINx +1 V

t < 50 ns, VINx = VIN1

, VIN2 , VIN3 –1.0 to VINx +3 V

LX4 Pin to GND VLX4

Continuous, lower limit is a function of

temperature –1.0 to 37 V

t < 50 ns –1.5 to 40 V

VREG Pin to GND VVREG –0.3 to 5.5 V

ACCI Pin2IACCI

1 mA

t < 100 ms –50 mA

All Other Pins –0.3 to 5.5 V

Operating Ambient Temperature TAE temperature range –40 to 85 ºC

Maximum Junction Temperature TJ(max) 150 ºC

Storage Temperature Tstg –55 to 150 ºC

1Stresses beyond those listed in this table may cause permanent damage to the device. The Absolute Maximum ratings are

stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical

Characteristics table is not implied. Exposure to Absolute Maximum-rated conditions for extended periods may affect device reliability.

2Negative current is defined as coming out of the node or pin, positive current is defined as going into the node or pin.

Thermal Characteristics

Characteristic Symbol Test Conditions* Value Unit

Package Thermal Resistance,

Junction to Ambient RθJA

On 4-layer PCB based on JEDEC standard 23 ºC/W

On 2-layer PCB with 3 in.2of copper area on 2 sides 44 ºC/W

Package Thermal Resistance,

Junction to Pad RθJP 2 ºC/W

*Additional thermal information available on the Allegro website.

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

5

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

24

23

22

21

20

19

18

17

16

15

14

13

37

38

39

40

41

42

43

44

45

46

47

48

1

2

3

4

5

6

7

8

9

10

11

12

36

35

34

33

32

31

30

29

28

27

26

25

VIN2

VIN2

NC

PGND

LG4

BOOT4

LX4

HG4

SS4

CSP

CSN

FB4

VIN1

MUTE

GND

VREG

CTMR

EN/SYNC

ACCO

ACCI

BUO

BUI

VIN3

VIN3

COMP4

POK

OUT2

VINS

OUT1

ENS

COMP3

FB3

SS3

BOOT3

LX3

LX3

LX2

LX2

BOOT2

SS2

FB2

COMP2

COMP1

FB1

BIAS

SS1

BOOT1

LX1

PAD

Pin-Out Diagram

Name Number Function

ACCI 8 Input to the ACC comparator

ACCO 7 Output of the ACC comparator

BIAS 45 Bias input, supplies internal circuitry when VSW1

is high enough

BOOT1 47 Floating gate drive for buck regulator SW1

BOOT2 39 Floating gate drive for buck regulator SW2

BOOT3 15 Floating gate drive for buck regulator SW3

BOOT4 31 Floating gate drive for buck regulator SW4

BUI 10 Input to the BU comparator

BUO 9 Output of the BU comparator

COMP1 43 Error amplifier compensation network for

regulator SW1

COMP2 42 Error amplifier compensation network for

regulator SW2

COMP3 18 Error amplifier compensation network for

regulator SW3

COMP4 24 Error amplifier compensation network for

regulator SW4

CSN 26 Current sense pin for buck regulator SW4

CSP 27 Current sense pin for buck regulator SW4

CTMR 5 Delay programming for the Mute pulse circuit

EN/SYNC 6 SWx enable and PFM control, and PWM

synchronization

ENS 19 S1/S2 enable input

FB1 44 Feedback pin for buck regulator SW1

FB2 41 Feedback pin for buck regulator SW2

FB3 17 Feedback pin for buck regulator SW3

Name Number Function

FB4 25 Feedback pin for buck regulator SW4

GND 3 Ground

HG4 29 High side gate drive for buck regulator SW4

LG4 32 Low side gate drive for buck regulator SW4

LX1 48 Switching node for buck regulator SW1

LX2 37, 38 Switching node for buck regulator SW2

LX3 13, 14 Switching node for buck regulator SW3

LX4 30 Switching node for buck regulator SW4

MUTE 2 Open-drain, active low output of the Mute pulse

circuit

NC 34 Unused

OUT1 20 High-side switch S1 output

OUT2 22 High-side switch S2 output

PAD – Exposed pad for enhanced thermal dissipation

PGND 33 Power ground

POK 23 Power OK open drain output

SS1 46 Soft start programming for regulator SW1

SS2 40 Soft start programming for regulator SW2

SS3 16 Soft start programming for regulator SW3

SS4 28 Soft start programming for regulator SW4

VIN1 1 Input supply for buck regulator SW1

VIN2 35, 36 Input supply for buck regulator SW2

VIN3 11, 12 Input supply for buck regulator SW3 (and SW4)

VINS 21 S1/S2 high-side switch input

VREG 4 Internal voltage regulator bypass capacitor pin

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

6

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

FB2

LX2

LX2

VIN2

VIN2

BOOT2

10 Ω

COMP2

SS2

COMP2

Delay

SS2

CLK180

TSDH

Adj (8 V)

1.0 A

AVG

2.5 A

PEAK

FB3

LX3

LX3

BOOT 3

10 Ω

COMP3

SS3

COMP3

SS3

CLK0

TSDH

Adj (3.3 V)

3.3 V

2.0 A

AVG

2.5 A

PEAK

FB4

LG4

HG4

COMP4

SS4

COMP4

SS4

CLK180

TSDH

CSP

CSN

FB1

Switcher 1

(SW1)

Adjustable

Always-On

PWM/PFM

Asynchronous

Buck Regulator

Switcher 3

(SW3)

Adjustable

PWM

Asynchronous

Buck Regulator

Switcher 4

(SW4)

Adjustable

PWM

Synchronous

Buck Controller

High-Side Switch 1

(S1) with

Foldback Limiting

High-Side Switch 2

(S2) with

Foldback Limiting

Switcher 2

(SW2)

Adjustable

PWM

Asynchronous

Buck Regulator

LX1

LSW1

CSW1

CIN1

CBOOT1

CIN2

CSW2

CSW3

CSW4

LSW2

LSW3

VIN1

BOOT 1

10 Ω

COMP1 COMP1

SS1

CLK0

1.0 A

Adj

AVG

2.5 A

PEAK

15 m

RS

Ω

Shoot-

Through

Protec-

tion

10µH

10 µH

10

LSW4

µH

Adj (5.7 V)

2.5 A

AVG

4.0 A

PEAK

50µF

VIN3

VIN3

BIAS

SS1

CSS1

RZ1

CZ1

RZ2

CZ2

RZ4

CZ4

CP4

CP3

CP2

CP1

RZ3

CZ3

CSS2

CSS3

0.68 µF

22 nF

150 mΩ

120 mΩ

112 mΩ

15 µH

3

DSW1

A

40 V

LX4

BOOT 4

0.1 µF

V

SW1

3 A

40 V

3 A

40 V

VREG

1.0 µF

EN

ENS

VINS 1.0 ΩTotal

1.0 ΩTotal

OUT2 LOAD 2

1µF

50 V

LOAD 1

OUT1

825 kΩ

1%

1 MΩ

1%

Mute

Logic

CTMR

8 to 32 μs

De-glitch

ACCI

ACCO

VBAT

BUO

BUI

ACC

Switch

1%

22.1 kΩ

1%

78.7 kΩ

1%

475 kΩ

1%

≈

6.2 V

≈

6.2 V

BU 3.3V

TC7 S H14F

BU 3.3V

TC 7S H14F

≈

35 V

4.7 kΩ

9.1 kΩ

10 kΩ

15 kΩ

1 µF

1µF

2200

A8600

µF

PGND

200 kΩ

200 kΩ

POK3

Current will not flow from ACCI to BUI or any VINx pin

TSDL

0

CCTMR

.1 µF

TSDL

BUCLEAN

50 kΩDONE

CHARGE

SET

RST

2 µA 2µA

POK

POK2

POK3

POK4

200 kΩ

EN/PFM

EN

EN

2048↓

1.205 V

215 mV

3.3 to 5.5 V

18.7 kΩ

4.7 nF

27 pF

47

47 nF

47 nF

kΩR

FBA1

R

FBB1

147 kΩ

10pF

Audio

Amplifier

MUTE

BIAS

BIAS

60.4 kΩ

60.4 kΩ

1%

5.0V

EN/SYNC

200 kΩ

VREG

To

microcontroller

To

microcontroller

To

microcontroller

From

microcontroller

3 A

40 V

50 kΩ

50 kΩ

V

REG

BIAS

Bias

Switch

>3.2V and

Off

On

BIAS >LDO

OUT

LDO

VIN1

Oscillator

180° Shift

with

Synchronization

S Q

R

S Q

R

VIN

S

UVLO

POK2

POK4

TSD

EN

S

GND

VREG

POR

TSDL

TSDH

TSDL

5.0 V

Charge

Pump

50 µF

50µF

50 µF

39.2 kΩ

2.2 nF

27 pF

22 nF

CSS4

22 nF

18.7 kΩ

2.2 nF

27 pF

24.9 kΩ

2.2 nF

27 pF

VINS UVLO

+

–

3.70 V

S1A

1µF

50 V

S1A

1.8 kΩ

16.2 kΩ

4.7 kΩ

14.7 kΩ

1.8 kΩ

11 kΩ

VREG POR

1.205V

REF

Band

Gap V

REGPORH

V

REGPORL

VREG POR

VREG POR

VREG POR

VIN3

VBAT _FILT

VBAT _FILT

VBAT _FILT

VBAT _FILT

3A

40V

Block active in Low IQ mode

A

B

B

A

B

Current will not flow from ACCO, BUO, MUTE, BIAS, VREG, FB1, POK, or OUTx to any VINx pin

SW4 lower FET must not cause VSW4 to decay during prebias startup

C

Optional: POK

to OUT2 short

protection for

microcontroller

Optional: ENS

to OUT1 for short

protection for

microcontroller

Optional: To

protect VINS

for Field Decay test

PAD

C

C

D

C

C

C

A

C

C

C

C

D

Optional: MUTE

to VIN1 short

protection for

amplifier

Schottky for SW4

may be omitted for

very low current

system only

Optional: To

maintain V

BOOT1

during very

low V

BAT

V

SW2

V

SW3

V

SW4

Delay

15 ↓

R

FBA2

R

FBB2

R

FBA3

R

FBB3

R

FBA4

R

FBB4

47 nF

DSW2

CIN3

DSW3

DSW4

CBOOT2

CBOOT3

CBOOT4

Top Level Functional Block Diagram and Typical Application Circuit

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

7

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

U P P E R FE T ON:

Q = 1 & T

O F F,M I N

= 0

U P P E R FE T OFF:

FB x OV or

1x OCx = 1 or

1x B OOTx UV or

S S INITx =1 or

H IC CU P x = 1

LOWE R FE T O N :

B OOTx UV & T

O F F,M I N

= 1

LOWE R FE T O FF :

S S INITx = 1 o r

H IC CU P x = 1

S Q

R Q

LX1,2,3

VIN1/2/3

COMPx

FBx

SSx

HICCUPx

SSINITx

PWM

COMPARATOR

RESET

D OMINA N T

CLK 0° (SW1/3 )

CLK180° (SW2)

400mV

+

–

+

ERROR

A8600

AMP

LX2,3

VIN2/3

ISENSEx

800mVREF

SLOPE

COMP

400mV

PWMxRST

ON

ILIM

GCSA

5K1K

ISS

HICx

ISS

SUx

2.3V

0.3V

FBx > 0.3V

SSx > 2.3V

OCx

COMPARATOR

& COUNTER

0 = 30 c ounts

1 = 118 counts

E N A B LE

C OUN TE R

ISENSEx

COMPxM AX

BOOT

MONITOR &

COUNTERS

7x B OOTx OV or

30x B OOTx U V

SSx < 0.2V

0.2V

FBx OV

FBx UV

860mV

740mV

RESET

D OMINA N T

LX1

FA ULT

LX1

Q

B OOTx – LX x

BOOTx

+

–

LXx

OSCILLATOR

IF FB x <0 . 4V then F /2

IF H ICC UP x =1 then F /4

E LS E F T

O F F,M I N

I

FBx

S W2 & S W3 on ly

BOOTx

TGx

BGx

S W1 only

LOW IP PWM

(SW1 only)

UVLOON↑

UVLOOF F↓

Q

R Q

S

S Q

R Q

POKx

DE-

GLITCH

S W2 a nd S W3 o nly

SW1

FIXED

OFF-TIME

PFM

CONTROL

ISENSE1

FB1

UVLO1

E N A B LE

TG1

BOOT1 ON

I

PEAK

WA K E/ S LE E P

S W1 only

1x BOOT 1 FAULT

1x LX1 FAULT

LOW IP PWM:

All PWM functions

ON & 50% I

LIM

UVLOx

LX2, LX3

LX2, 3 or

LG2

FA ULTS

S W2 and S W 3 o nly

TSDH (S W2, SW3 only)

EN (SW2, SW3 only)

VREG POR

EN/PFM (SW 1 only)

S Q

R Q

CLAMP COMPxM AX

EN/PFM

Figure 2. Detailed functional block diagram for SW1, SW2, and SW3

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

8

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

S Q

R Q

LX4

COMP4

FB4

SS4

PWM

COMPARATOR

RESET

D OMINA N T

CLK180

400mV

+

–

+

ERROR

AMP

I

SENSE4

800mV

REF

SLOPE

COMP

400mV

PWM4

RST

ON

ILIM

G

CSA

Q

OSCILLATOR

IF FB 4<0.4V the n F / 2

IF H IC CU P 4= 1 the n F / 4

E LS E F T

O F F,M I N

I

FB4

BOOT 4

VIN3

CSP

CSN

HG4

LG4

PGND

VIN 3

Q

U P P E R FE T ON :

Q = 1 & T

O F F,M I N

= 0

U P P E R FE T OFF:

FB 4 OV or

1x OC4 = 1 or

1x B OOT4 U V o r

S S INIT4 =1 or

HICCUP4 = 1

LOWE R FE T ON:

Q = 1 & T

O F F,M IN

= 1 or

B OOT4 U V & T

O F F,M IN

= 1

LOWE R FE T OFF :

S S INIT4 = 1 or

HICCUP4 = 1

GA TE

D RIV E R

NON-

OV E R LA P

HICCUP4

SSINIT 4

5K1K

ISS

HIC4

ISS

SU4

2.3V

0.3V

FB4 > 0.3V

SS4 > 2.3V

OC4

COMPARATOR

& COUNTER

0 = 30 c ounts

1 = 118 counts

E N A B LE

C OUN TE R

I

SENSE4

COMP4

M AX

BOOT

MONITOR &

COUNTERS

7x B OOTx OV or

30x B OOTx U V

SS4 < 0.2V

0.2V

FB4 OV

FB4 UV

860mV

740mV

RESET

D OMINA N T

B OOT4 – L X 4

BOOT4

+

–

LX4

UVLO

ON

↑

UVLO

OF F

↓

Q

R Q

S

S Q

R Q

POK 4

DE-

GLITCH

UVLO4

LX4

LX4 or

LG2

FA ULTS

TSDH

EN

VREG POR

S Q

R Q

CLAMP COMP4

M AX

A8600

Figure 3. Detailed functional block diagram for SW4

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

9

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

ELECTRICAL CHARACTERISTICS Valid at 5.5 V ≤ VINx ≤ 26 V, –40°C ≤ TA ≤ 125ºC, –40°C ≤ TJ ≤ 125ºC;

unless otherwise specified

Characteristic Symbol Test Conditions Min. Typ. Max. Unit

GENERAL SPECIFICATIONS

Input Supply Current

Input Supply Current1IIN1 VBIAS > 3.2 V, ISW1 = 0 mA −7.5 10 mA

Input Supply Current, PFM1,3

(Using components shown in Typical

Application Circuit diagram and

table 3.)

ILO_IQ0

VIN1 = 12 V, VSW1 = 3.3 V, VEN/SYNC ≤ 0.4 V,

BUO and ACCO open, ISW1 = 40 µA, TA= 25ºC − − 50 µA

ILO_IQ1

VIN1 = 12 V, VSW1 = 5.0 V, VEN/SYNC ≤ 0.4 V,

BUO and ACCO open, ISW1 = 200 µA,TA

= 25ºC − − 250 µA

ILO_IQ2

VIN1 = 12 V, VSW1 = 6.5 V, VEN/SYNC ≤ 0.4 V,

BUO and ACCO open, ISW1 = 1 mA, TA = 25ºC − − 750 µA

Internal Oscillator Frequency

LX1/2/3/4 Switching Frequency fOSC 360 425 490 kHz

EN/SYNC Synchronization Timing

Synchronization Input Frequency fSYNC 325 −525 kHz

Synchronization Input Duty Cycle DSYNC 45 50 55 %

EN/SYNC Input

EN/SYNC Pin High Threshold VENIH

3.0 V < VBIAS < 3.6 V, VEN/SYNC rising − − 2.0 V

4.5 V < VBIAS < 5.5 V, VEN/SYNC rising − − 2.6 V

EN/SYNC Pin Low Threshold VENIL

3.0 V < VBIAS < 3.6 V, VEN/SYNC falling 0.8 − − V

4.5 V < VBIAS < 5.5 V, VEN/SYNC falling 1.2 − − V

EN/SYNC Hysteresis VENHYS

3.0 V < VBIAS < 3.6 V, VENIH – VENIL −200 −mV

4.5 V < VBIAS < 5.5 V, VENIH – VENIL −400 −mV

EN/SYNC Input Resistance RENIN 120 200 280 kΩ

EN/SYNC Turn-Off Delay

tdOFF

Measured from EN/SYNC pulled low to

SW2/3/4, S1/2, and TSD turned off −15 −PWM

cycles

tdLo_IQ

Measured from EN/SYNC pulled low or TSDH

going high to SW1 entering Low IQ mode −2048 −PWM

cycles

VREG Output and BIAS Input

VREG Output Voltage VVREG VBIAS = 0 V 2.95 3.05 3.175 V

VREG (REGOK rising) VREGPORHI VVREG rising 2.86 2.93 2.98 V

VREG (BIAS switch Off and POR) VREGPORLO VVREG falling 2.85 2.90 2.96 V

BIAS Switch Turn-On Threshold VBIAS(TH) VBIAS − VVREG −3 10 20 mV

Bias Switch Voltage Drop VBIASSW VBIAS − VVREG −45 70 mV

BIAS Input Voltage Range VBIAS 3.2 −5.5 V

Power OK (POK)

POK Low Condition Output Voltage VPOKO(L) IPOK = 3 mA − − 300 mV

POK Leakage1IPOK(LKG) VPOKO = 5.0 V −1 − 1 µA

Continued on the next page…

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

10

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

GENERAL SPECIFICATIONS (continued)

Thermal Protection

SW1/2/3/4 TSD Threshold3TTSDH

SW1 to Low IQ mode after 2048 cycles, reset by

cycling EN/SYNC, or by a VREG POR 150 165 180 ºC

S1/2 Latched TSD Threshold3TTSDL

Reset by cycling any of ENS, EN/SYNC, VINS,

or by a VREG POR 140 155 170 ºC

SW1 (ALWAYS-ON, LOW IQ, PWM/PFM REGULATOR)

Input Voltage

Input Voltage Range2VIN1 4.0 −35 V

UVLO Start VUVLOON1 VIN1 rising 3.6 3.8 4.0 V

UVLO Stop VUVLOOFF1 VIN1 falling 3.2 3.4 3.6 V

UVLO Hysteresis VUVLOHYS1 −400 −mV

Voltage Regulation

Feedback Voltage Accuracy VFB1 VIN1 ≥ 4.1 V, VFB1 = VCOMP1 788 800 812 mV

Output Voltage Setting Range VSW1

VSW1(min) value is design target, see footnote 2

for typ and max voltages 3.3 5.0 6.5 V

Output Dropout Voltage VSW(PWM)1

VIN1 = 3.7 V, ISW1 = 50 mA 3.3 − − V

VIN1 = 6.0 V, ISW1 = 1 A 5.0 − − V

Low IQ Peak Current Limit IPEAK(LO_IQ) 600 800 1000 mA

Low IQ DC Current Capability IDC(LO_IQ) 500 − − mADC

Low IQ Constant OFF Time tOFF(LO_IQ) 220 300 380 ns

Low IQ Maximum ON Time tON(LO_IQ) 3.3 4 4.9 µs

Low IQ Mode Voltage Ripple3VPP1(LO_IQ)

8 V < VIN1 < 12 V, configured as shown in the

Typical Application Circuit − − 50 mVPP

Internal MOSFET2

High-Side MOSFET On-Resistance RDS(on)HS1 TJ= 25ºC, IDS1 = 1.0 A −150 170 mΩ

High-Side MOSFET Leakage1IHS(LKG)1

TJ < 65°C,VEN/SYNC ≤ 0.8 V, VLX1 = 0 V,

VIN1 = 12 V −5 − 5μA

Low-Side MOSFET On-Resistance RDS(on)LS1 TJ= 25ºC − − 10 Ω

BOOT Regulator

BOOT Voltage Enable Threshold VBOOT(TH)1 VBOOT1 rising 1.85 2.10 2.30 V

BOOT Voltage Enable Hysteresis V

BOOT(HYS)1

−375 −mV

Error Amplifier

Feedback Input Bias Current1IFB1 –30 – –8 nA

Open Loop Voltage Gain AVOL1 VCOMP1 = 1.2 V 52 58 65 dB

Transconductance gm1

400 mV < VFB1 550 750 950 μA/V

0 V < VFB1 < 400 mV 275 375 475 μA/V

ELECTRICAL CHARACTERISTICS (continued) Valid at 5.5 V ≤ VINx ≤ 26 V, –40°C ≤ TA ≤ 125ºC, –40°C ≤ TJ ≤ 125ºC;

unless otherwise specified

Characteristic Symbol Test Conditions Min. Typ. Max. Unit

Continued on the next page…

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

11

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

SW1 (ALWAYS-ON, LOW IQ, PWM/PFM REGULATOR) (continued)

Error Amplifier (continued)

Output Current IEA1 VCOMP1 = 1.2 V −±75 − μA

Maximum Output Voltage VEAO(max)1 1.3 1.7 2.1 V

Minimum Output Voltage VEAO(min)1 − − 200 mV

COMP1 Pull Down Resistance RCOMP1 Fault condition −1− kΩ

Pulse Width Modulation (PWM)

PWM Ramp Offset V

PWMOFFSET1

VCOMP1 set for 0% duty cycle −400 −mV

Minimum Controllable On-Time tON(MIN)1 80 140 180 ns

Minimum Switch Off-Time tOFF(MIN)1 40 95 135 ns

COMP1 to SW1 Current Gain gmPOWER1 −3.6 −A/V

Slope Compensation SE1 300 450 600 mA/μs

Overcurrent Protection (OCP)

Pulse-by-Pulse Current Limit ILIM1

tON1 = tON(MIN)1

,fSW = fOSC 3.9 4.4 4.9 A

tON1 = (1 / fOSC) – tOFF(MIN)1 , fSW = fOSC 3.0 3.5 4.0 A

Overvoltage Protection (OVP)

Output Overvoltage Threshold (SW1

Disable) VOVO1 VFB1 rising, PWM mode 840 860 880 mV

Overvoltage Hysteresis VOVOHYS1 VFB1 falling, relative to VOVO1 − −10 − mV

Soft Start

SS1 Hiccup Reset Voltage VSSRST1 VSS1 falling due to RSSFLT1 140 200 275 mV

SS1 Switching Frequency fSS1

0 V < VFB1 < 300 mV, VCOMP1 at maximum −fSW1/4 −kHz

0 V < VFB1 < 300 mV −fSW1/2 −kHz

300 mV < VFB1 −fSW1 −kHz

SS1 Startup (Source) Current1ISSSU1 Hiccup mode disabled (no fault condition) −2.50 −2.00 −1.50 μA

SS1 Hiccup (Sink) Current1ISSHIC1 Hiccup mode enabled 0.75 1.00 1.25 μA

SS1 Delay Time tdSS1 CSS1 = 0.68 µF −136 −ms

SS1 Ramp Time tSSRAMP1 CSS1 = 0.68 µF −272 −ms

SS1 Pull Down Resistance RSSFLT1 Fault condition −5− kΩ

Hiccup Mode (PWM only, not in PFM)

Hiccup OCP Enable Threshold VHICEN1 VSS1 rising −2.3 −V

Hiccup Operation OCP Count tOCPLIM1

VSS1 > 2.3 V, VFB1 < 0.3 V −30 −PWM

cycles

VSS1 > 2.3 V, VFB1 > 0.3 V −118 −PWM

cycles

Hiccup Operation BOOT Shorted

Count tBOOTUV1 −30 −PWM

cycles

Hiccup Operation BOOT Open Count tBOOTOPEN1 −7−PWM

cycles

ELECTRICAL CHARACTERISTICS (continued) Valid at 5.5 V ≤ VINx ≤ 26 V, –40°C ≤ TA ≤ 125ºC, –40°C ≤ TJ ≤ 125ºC;

unless otherwise specified

Characteristic Symbol Test Conditions Min. Typ. Max. Unit

Continued on the next page…

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

12

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

SW2 (ASYNCHRONOUS BUCK REGULATOR)

Input Voltage

Input Voltage Range2VIN2 4.4 −35 V

UVLO Start VUVLOON2 VIN2 rising 4.1 4.25 4.4 V

UVLO Stop VUVLOOFF2 VIN2 falling 3.6 3.75 3.9 V

UVLO Hysteresis VUVLOHYS2 −500 −mV

Voltage Regulation

Feedback Voltage Accuracy VFB2 VIN2 ≥ 4.4 V, VFB2 = VCOMP2 788 800 812 mV

Output Voltage Setting Range VSW2

VSW2(typ) value is design target, see footnote 2

for min and max voltages 1.2 8.0 9.2 V

Output Dropout Voltage3VSW(PWM)2 VIN2 = 6.0 V, ISW2 = 1 A 5.0 − − V

Internal MOSFET2

High-Side MOSFET On-Resistance RDS(on)HS2 TJ= 25ºC, IDS2 = 1.5 A −120 140 mΩ

High-Side MOSFET Leakage1IHS(LKG)2

TJ < 65°C,VEN/SYNC ≤ 0.8 V, VLX2 = 0 V,

VIN2 = 12 V −5 − 5μA

Low-Side MOSFET On-Resistance RDS(on)LS2 TJ= 25ºC − − 10 Ω

BOOT Regulator

BOOT Voltage Enable Threshold VBOOT(TH)2 VBOOT2 rising 1.85 2.10 2.30 V

BOOT Voltage Enable Hysteresis V

BOOT(HYS)2

−375 −mV

Error Amplifier

Feedback Input Bias Current1IFB2 –100 – –8 nA

Open Loop Voltage Gain AVOL2 VCOMP2 = 1.2 V 52 60 65 dB

Transconductance gm2

400 mV < VFB2 550 750 950 μA/V

0 V < VFB2 < 400 mV 275 375 475 μA/V

Output Current IEA2 VCOMP2 = 1.2 V −±75 − μA

Maximum Output Voltage VEAO(max)2 1.3 1.7 2.1 V

Minimum Output Voltage VEAO(min)2 − − 200 mV

COMP2 Pull Down Resistance RCOMP2 Fault condition −1− kΩ

Pulse Width Modulation (PWM)

PWM Ramp Offset V

PWMOFFSET2

VCOMP2 set for 0% duty cycle −400 −mV

Minimum Controllable On-Time tON(MIN)2 80 140 180 ns

Minimum Switch Off-Time tOFF(MIN)2 40 95 135 ns

COMP2 to SW2 Current Gain gmPOWER2 −3.6 −A/V

Slope Compensation SE2 300 450 600 mA/μs

ELECTRICAL CHARACTERISTICS (continued) Valid at 5.5 V ≤ VINx ≤ 26 V, –40°C ≤ TA ≤ 125ºC, –40°C ≤ TJ ≤ 125ºC;

unless otherwise specified

Characteristic Symbol Test Conditions Min. Typ. Max. Unit

Continued on the next page…

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

13

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

SW2 (ASYNCHRONOUS BUCK REGULATOR) (continued)

Overcurrent Protection (OCP)

Pulse-by-Pulse Current Limit ILIM2

tON2 = tON(MIN)2

,fSW = fOSC 3.9 4.4 4.9 A

tON2 = (1 / fOSC) – tOFF(MIN)2 , fSW = fOSC 3.0 3.5 4.0 A

Power OK (POK) Thresholds for Overvoltage (OV) and Undervoltage (UV)

POK Threshold for Overvoltage VPOKOV2 VFB2 rising 840 860 880 mV

POK Hysteresis for Overvoltage V

POKOVHYS2

VFB2 falling, relative to VPOKOV2 − −10 − mV

POK Threshold for Undervoltage VPOKUV2 VFB2 falling 720 740 760 mV

POK Hysteresis for Undervoltage V

POKUVHYS2

VFB2 rising, relative to VPOKUV2 −10 −mV

Power OK (POK) Filtering

POK Delay Time V

POKDELAY2

Response to a step input −6−µs

Soft Start

SS2 Hiccup Reset Voltage VSSRST2 VSS2 falling due to RSSFLT2 140 200 275 mV

SS2 Switching Frequency fSS2

0 V < VFB2 < 300 mV, VCOMP2 at maximum −fSW2/4 −kHz

0 V < VFB2 < 300 mV −fSW2/2 −kHz

300 mV < VFB2 −fSW2 −kHz

SS2 Startup (Source) Current1ISSSU2 Hiccup mode disabled (no fault condition) −30 –20 −10 μA

SS2 Hiccup (Sink) Current1ISSHIC2 Hiccup mode enabled 5 10 20 μA

SS2 Delay Time tdSS2 CSS2 = 22 nF −440 − μs

SS2 Ramp Time tSSRAMP2 CSS2 = 22 nF −880 − μs

SS2 Pull Down Resistance RSSFLT2 Fault condition −5− kΩ

SS2 Startup Current Ratio ISSSUTRK2 Relative to ISSSU3 or ISSSU4 −15 − +15 %

Hiccup Mode

Hiccup OCP Enable Threshold VHICEN2 VSS2 rising −2.3 −V

Hiccup Operation OCP Count tOCPLIM2

VSS2 > 2.3 V, VFB2 < 0.3 V −30 −PWM

cycles

VSS2 > 2.3 V, VFB2 > 0.3 V −118 −PWM

cycles

Hiccup Operation BOOT Shorted

Count tBOOTUV2 −30 −PWM

cycles

Hiccup Operation BOOT Open Count tBOOTOPEN2 −7−PWM

cycles

ELECTRICAL CHARACTERISTICS (continued) Valid at 5.5 V ≤ VIN ≤ 26 V, –40°C ≤ TA ≤ 125ºC, –40°C ≤ TJ ≤ 125ºC;

unless otherwise specified

Characteristic Symbol Test Conditions Min. Typ. Max. Unit

Continued on the next page…

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

14

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

SW3 (ASYNCHRONOUS BUCK REGULATOR)

Input Voltage Specifications

Input Voltage Range2VIN3 4.4 −35 V

UVLO Start VUVLOON3 VIN3 rising 4.1 4.25 4.4 V

UVLO Stop VUVLOOFF3 VIN3 falling 3.6 3.75 3.9 V

UVLO Hysteresis VUVLOHYS3 −500 −mV

Voltage Regulation

Feedback Voltage Accuracy VFB3 VIN3 ≥ 4.4 V, VFB3 = VCOMP3 788 800 812 mV

Output Voltage Setting Range VSW3

VSW3(typ) value is design target, see footnote 2

for min and max voltages 1.2 3.3 9.2 V

Output Dropout Voltage3VSW(PWM)3 Configured as in Ty, VIN3 = 6.0 V, ISW3 = 1 A 5.0 − − V

Internal MOSFET Parameters2

High-Side MOSFET On-Resistance RDS(on)HS3 TJ= 25ºC, IDS3 = 2.0 A −112 130 mΩ

High-Side MOSFET Leakage1IHS(LKG)3

TJ < 65°C,VEN/SYNC ≤ 0.8 V, VLX3 = 0 V,

VIN3 = 12 V −5 − 5μA

Low-Side MOSFET On-Resistance RDS(on)LS3 TJ= 25ºC − − 10 Ω

BOOT Regulator

BOOT Voltage Enable Threshold VBOOT(TH)3 VBOOT3 rising 1.85 2.10 2.30 V

BOOT Voltage Enable Hysteresis V

BOOT(HYS)3

−375 −mV

Error Amplifier

Feedback Input Bias Current1IFB3 –100 – –8 nA

Open Loop Voltage Gain AVOL3 VCOMP3 = 1.2 V 52 60 65 dB

Transconductance gm3

400 mV < VFB3 550 750 950 μA/V

0 V < VFB3 < 400 mV 275 375 475 μA/V

Output Current IEA3 VCOMP3 = 1.2 V −±75 − μA

Maximum Output Voltage VEAO(max)3 1.3 1.7 2.1 V

Minimum Output Voltage VEAO(min)3 − − 200 mV

COMP3 Pull Down Resistance RCOMP3 Fault condition −1− kΩ

Pulse Width Modulation (PWM)

PWM Ramp Offset V

PWMOFFSET3

VCOMP3 set for 0% duty cycle −400 −mV

Minimum Controllable On-Time tON(MIN)3 80 140 180 ns

Minimum Switch Off-Time tOFF(MIN)3 40 95 135 ns

COMP3 to SW3 Current Gain gmPOWER3 −3.6 −A/V

Slope Compensation SE3 300 450 600 mA/μs

ELECTRICAL CHARACTERISTICS (continued) Valid at 5.5 V ≤ VINx ≤ 26 V, –40°C ≤ TA ≤ 125ºC, –40°C ≤ TJ ≤ 125ºC;

unless otherwise specified

Characteristic Symbol Test Conditions Min. Typ. Max. Unit

Continued on the next page…

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

15

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

SW3 (ASYNCHRONOUS BUCK REGULATOR) (continued)

Overcurrent Protection (OCP)

Pulse-by-Pulse Current Limit ILIM3

tON3 = tON(MIN)3

,fSW = fOSC 3.9 4.4 4.9 A

tON3 = (1 / fOSC) – tOFF(MIN)3 , fSW = fOSC 3.0 3.5 4.0 A

Power OK (POK) Thresholds for Overvoltage (OV) and Undervoltage (UV)

POK Threshold for Overvoltage VPOKOV3 VFB3 rising 840 860 880 mV

POK Hysteresis for Overvoltage V

POKOVHYS3

VFB3 falling, relative to VPOKOV3 − −10 − mV

POK Threshold for Undervoltage VPOKUV3 VFB3 falling 720 740 760 mV

POK Hysteresis for Undervoltage V

POKUVHYS3

VFB3 rising, relative to VPOKUV3 −10 −mV

Power OK (POK) Filtering

POK Delay Time V

POKDELAY3

Response to a step input −6−µs

Soft Start

SS3 Hiccup Reset Voltage VSSRST3 VSS3 falling due to RSSFLT3 140 200 275 mV

SS3 Switching Frequency fSS3

0 V < VFB3 < 300 mV, VCOMP3 at maximum −fSW3/4 −kHz

0 V < VFB3 < 300 mV −fSW3/2 −kHz

300 mV < VFB3 −fSW3 −kHz

SS3 Startup (Source) Current1ISSSU3 Hiccup mode disabled (no fault condition) −30 –20 −10 μA

SS3 Hiccup (Sink) Current1ISSHIC3 Hiccup mode enabled 5 10 20 μA

SS3 Delay Time tdSS3 CSS3 = 22 nF −440 − μs

SS3 Ramp Time tSSRAMP3 CSS3 = 22 nF −880 − μs

SS3 Pull Down Resistance RSSFLT3 Fault condition −5− kΩ

SS3 Startup Current Ratio ISSSUTRK3 Relative to ISSSU2 or ISSSU4 −15 − +15 %

Hiccup Mode

Hiccup OCP Enable Threshold VHICEN3 VSS3 rising −2.3 −V

Hiccup Operation OCP Count tOCPLIM3

VSS3 > 2.3 V, VFB3 < 0.3 V −30 −PWM

cycles

VSS3 > 2.3 V, VFB3 > 0.3 V −118 −PWM

cycles

Hiccup Operation BOOT Shorted

Count tBOOTUV3 −30 −PWM

cycles

Hiccup Operation BOOT Open Count tBOOTOPEN3 −7−PWM

cycles

ELECTRICAL CHARACTERISTICS (continued) Valid at 5.5 V ≤ VINx ≤ 26 V, –40°C ≤ TA ≤ 125ºC, –40°C ≤ TJ ≤ 125ºC;

unless otherwise specified

Characteristic Symbol Test Conditions Min. Typ. Max. Unit

Continued on the next page…

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

16

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

SW4 (SYNCHRONOUS BUCK CONTROLLER WITH GATE DRIVERS)

Input Voltage Specifications

Input Voltage Range2VIN3 4.4 −35 V

UVLO Start VUVLOON4 VIN3 rising 4.1 4.25 4.4 V

UVLO Stop VUVLOOFF4 VIN3 falling 3.6 3.75 3.9 V

UVLO Hysteresis VUVLOHYS4 −500 −mV

Voltage Regulation

Feedback Voltage Accuracy VFB4 VIN3 ≥ 4.4 V, VFB4 = VCOMP4 788 800 812 mV

Output Voltage Setting Range VSW4

VSW4(typ) value is design target, see footnote 2

for min and max voltages 1.2 5.7 6.5 V

Output Dropout Voltage3VSW(PWM)4

Configured as in Typical Application Circuit,

VIN4 = 6.0 V, ISW4 = 1 A 5.0 − − V

External MOSFET Gate Drivers

HG4 High Output Voltage VHG4ON Measured as VHG4 – VIN3 4.0 6.0 6.7 V

HG4 Low Output Voltage VHG4OFF Measured as VHG4 – VLX4

, IHG4 = 100 mA −0.20 0.40 V

HG4 Sink Current1IHG4ON VHG4 = VIN3 − 2 V − 1000 −mA

HG4 Source Current1IHG4OFF VHG4 = VIN3 − 2 V − −150 − mA

LG4 High Output Voltage VLG4ON VIN3 ≥ 5.5 V 4.0 6.0 7.2 V

LG4 Low Output Voltage VLG4OFF ILG4 = 100 mA −0.25 0.50 V

LG4 Source Current1ILG4ON − −500 − mA

LG4 Sink Current1ILG4OFF −600 −mA

BOOT Regulator

BOOT Voltage Enable Threshold VBOOT(TH)4 VBOOT4 rising 2.25 2.60 2.90 V

BOOT Voltage Enable Hysteresis V

BOOT(HYS)4

−375 −mV

Error Amplifier

Feedback Input Bias Current1IFB4 –100 – –8 nA

Open Loop Voltage Gain AVOL4 VCOMP4 = 1.2 V 52 60 65 dB

Transconductance gm4

400 mV < VFB4 550 750 950 μA/V

0 V < VFB4 < 400 mV 275 375 475 μA/V

Output Current IEA4 VCOMP4 = 1.2 V −±75 − μA

Maximum Output Voltage VEAO(max)4 1.3 1.7 2.1 V

Minimum Output Voltage VEAO(min)4 − − 200 mV

COMP4 Pull Down Resistance RCOMP4 Fault condition −1− KΩ

ELECTRICAL CHARACTERISTICS (continued) Valid at 5.5 V ≤ VINx ≤ 26 V, –40°C ≤ TA ≤ 125ºC, –40°C ≤ TJ ≤ 125ºC;

unless otherwise specified

Characteristic Symbol Test Conditions Min. Typ. Max. Unit

Continued on the next page…

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

17

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

SW4 (SYNCHRONOUS BUCK CONTROLLER WITH GATE DRIVERS) (continued)

Pulse Width Modulation (PWM)

PWM Ramp Offset V

PWMOFFSET4

VCOMP4 set for 0% duty cycle −400 −mV

COMP4 Cycle Skip Level VCOMPSKIP4 VSS4 < 2.3 V −200 −mV

Minimum Controllable On-Time tON(MIN)4 40 100 150 ns

Minimum Switch Off-Time tOFF(MIN)4 80 120 160 ns

COMP4 to SW4 Current Gain gmPOWER4 −63 − (A•mΩ)/V

Slope Compensation SE4 4.5 6.8 9.0 mV/μs

Overcurrent Protection (OCP)

Pulse-by-Pulse Current Limit ILIM4

tON4 = tON(MIN)4 62 75 88 mV

tON4 = (1 / fOSC

) – tOFF(MIN)4, fSW = fOSC 48 60 72 mV

Power OK (POK) Thresholds for Overvoltage (OV) and Undervoltage (UV)

POK Threshold for Overvoltage VPOKOV4 VFB4 rising 840 860 880 mV

POK Hysteresis for Overvoltage V

POKOVHYS4

VFB4 falling, relative to VPOKOV4 − −10 − mV

POK Threshold for Undervoltage VPOKUV4 VFB4 falling 720 740 760 mV

POK Hysteresis for Undervoltage V

POKUVHYS4

VFB4 rising, relative to VPOKUV4 −10 −mV

Power OK (POK) Filtering

POK Delay / De-glitch V

POKDELAY4

Response to a step input −6−µs

Soft Start

SS4 Hiccup Reset Voltage VSSRST4 VSS4 falling due to RSSFLT4 140 200 275 mV

SS4 Switching Frequency fSS4

0 V < VFB4 < 300 mV, VCOMP4 at maximum −fSW4/4 −kHz

0 V < VFB4 < 300 mV −fSW4/2 −kHz

300 mV < VFB4 −fSW4 −kHz

SS4 Startup (Source) Current1ISSSU4 Hiccup mode disabled (no fault condition) −30 –20 −10 μA

SS4 Hiccup (Sink) Current1ISSHIC4 Hiccup mode enabled 5 10 20 μA

SS4 Delay Time tdSS4 CSS4 = 22 nF −440 − μs

SS4 Ramp Time tSSRAMP4 CSS4 = 22 nF −880 − μs

SS4 Pull Down Resistance RSSFLT4 Fault condition −5− KΩ

SS4 Startup Current Ratio ISSSUTRK4 Relative to ISSSU2 or ISSSU3 −15 − +15 %

ELECTRICAL CHARACTERISTICS (continued) Valid at 5.5 V ≤ VINx ≤ 26 V, –40°C ≤ TA ≤ 125ºC, –40°C ≤ TJ ≤ 125ºC;

unless otherwise specified

Characteristic Symbol Test Conditions Min. Typ. Max. Unit

Continued on the next page…

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

18

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

ELECTRICAL CHARACTERISTICS (continued) Valid at 5.5 V ≤ VINx ≤ 26 V, –40°C ≤ TA ≤ 125ºC, –40°C ≤ TJ ≤ 125ºC;

unless otherwise specified

Characteristic Symbol Test Conditions Min. Typ. Max. Unit

Continued on the next page…

Hiccup Mode

Hiccup OCP Enable Threshold VHICEN4 VSS4 rising −2.3 −V

Hiccup Operation OCP Count tOCPLIM4

VSS4 > 2.3 V, VFB4 < 0.3 V −30 −PWM

cycles

VSS4 > 2.3 V, VFB4 > 0.3 V −118 −PWM

cycles

Hiccup Operation BOOT Shorted

Count tBOOTUV4 −30 −PWM

cycles

Hiccup Operation BOOT Open Count tBOOTOPEN4 −7−PWM

cycles

HIGH-SIDE SWITCHES (S1, S2)

Input Voltage Range2VINS 4.5 −35 V

UVLO Start VUVLOONS VINS rising 4.0 4.2 4.4 V

UVLO Stop VUVLOOFFS VINS falling 3.5 3.7 3.9 V

UVLO Hysteresis VUVLOHYSS −500 −mV

Overvoltage Threshold (Rising) VOVRISES VINS rising 17.2 18.3 19.4 V

Overvoltage Threshold (Falling) VOVFALLS VINS falling 16.9 18.0 19.0 V

MOSFET On-Resistance RDS(on)S IS= 250 mA, TJ= 25ºC −1.00 1.15 Ω

Voltage Drop ΔVS

VINS ≥ 5.5 V, IS = −250 mA, TJ= 25ºC −250 290 mV

VINS ≥ 4.5 V, IS = −100 mA, TJ= 25ºC −100 115 mV

Current Limit1,2 IPEAKS Not continuous −570 −450 −270 mA

Foldback Current1IFLDBKS VOUTx = 0 V, VINS = 15 V −150 −100 −55 mA

Leakage Current1ILKGS −1 − 1 µA

Pull Down Resistance RFLTS −200 − kΩ

Turn-On Delay tdS VENS rise to 10% of ΔVOUTx 10 60 200 µs

Output Rise Time trS 237 Ω / 1 µF load, 10% to 90% of ΔVOUTx 10 60 200 µs

ENS High Threshold VENSH − − 2.0 V

ENS Low Threshold VENSL 0.8 − − V

ENS Hysteresis VENSHYS −100 −mV

ENS Input Resistance RINENS 120 200 280 kΩ

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

19

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

ELECTRICAL CHARACTERISTICS (continued) Valid at 5.5 V ≤ VINx ≤ 26 V, –40°C ≤ TA ≤ 125ºC, –40°C ≤ TJ ≤ 125ºC;

unless otherwise specified

Characteristic Symbol Test Conditions Min. Typ. Max. Unit

BU AND ACC COMPARATORS

BUI and ACCI Detect Threshold VDET 1.181 1.205 1.229 V

BUI and ACCI Input Bias1IBUI, IACCI VBUI or VACCI ≤ 5.0 V 30 65 100 nA

BUO Delay tdBUO 20 mV input overdrive −1.5 5 µs

ACCO Delay tdACCO 20 mV input overdrive −1.5 5 µs

BUO and ACCO Output Voltage

VBUOH,

VACCOH

IBUO = IACCO = −3 mA VBIAS –

300 mV −VBIAS V

VBUOL,

VACCOL

IBUO = IACCO = 3 mA − − 300 mV

BUO and ACCO Forced Low VBUOLF,

VACCOLF

IBUO = IACCO = 3 mA , 2 V < VBIAS < 3 V,

VIN1 < 5.5 V − − 300 mV

CTMR and MUTE

CTMR Charge Current1ICTMR(CHRG) MUTE = low, VCTMR rising −2.50 −2.00 −1.50 µA

CTMR Discharge Current1ICTMR(DIS) MUTE = low, VCTMR falling 1.50 2.00 2.50 µA

CTMR Upper Threshold VCTMRVH VCTMR rising 1.181 1.205 1.229 V

CTMR Lower Threshold VCTMRVL VCTMR falling 185 215 245 mV

CTMR Pull Down Resistance RCTMR MUTE = high −50 − kΩ

MUTE Low Output Voltage VMUTEOL IMUTE = 3 mA − − 300 mV

MUTE Leakage Current1IMUTELKG VMUTE = 5.0 V −1 − 1 µA

MUTE Rising Delay tdrMUTE CCTMR = 0.10 µF 725 1000 1275 ms

MUTE Falling Delay (De-glitch) tdfMUTE From BUO set low to MUTE low 8 16 32 µs

MUTE Self-Protect Shutoff VMUTE(OFF) −8.5 −V

1Negative current is defined as coming out of the node or pin, positive current is defined as going into the node or pin.

2Thermally limited depending on input voltage, duty cycle, regulator load currents, PCB layout, and airflow.

3Determined by design and characterization, not production tested.

Quadruple Output Regulator with Two High-Side Switches,

BU/ACC Voltage Detectors, and Mute Delay

A8600

20

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

Figure 4. SW1 PWM Timing Diagram with EN/SYNC pin high

15

Vout1 shorted to GND

BOOT

FAULTS

EN/SYNC↓for 15 cycles or VREG

POR clears the TSDH latch

20482048

DIODE

FAULT

BOOT

FAULTS

MODE

ACCo

EN/SYNC

TSDH

OC

HIC_EN

HICCUP

OC

FAULT

BOOT

FAULT

VIN1

VOUT1

SS1

COMP1

DIODE

FAULT

LX1

TSDL

F

F

/

4

F

/

2

F

/

2

F

/

2

F

/

2

SS PWM OC HICCUP HICCUPOC SS PWM HICCUP PWM HICCUP PWM TSDL /

TSDH

LOW IQ due to TSDH

(internal OSC is operational) PWM

FFFFF/4

S

SSS

F

/

2

SS LOW IQ

VFB<0 .3V: x 30

VFB> 0.3V: x 120

S

S

HICC

UP

F

/

2

SS HI

C

DIODE

FAULT

x1 x1

x7 OPEN

x30 UV

x7 OPEN

x30 UV

TO

2.3V

FROM

2.3V TO

2.3V

FROM

2.3V

OFF

VFB< 0.3V: x 30

VFB>0.3V : x120

This manual suits for next models

5

Table of contents

Popular Controllers manuals by other brands

Bosch

Bosch 2600 Series instruction manual

Linak

Linak TECHLINE LA25 Connection diagram

Bosch

Bosch FW 200 Installation and operating instructions

iZone

iZone 225 Installation, Configuration & User Manual

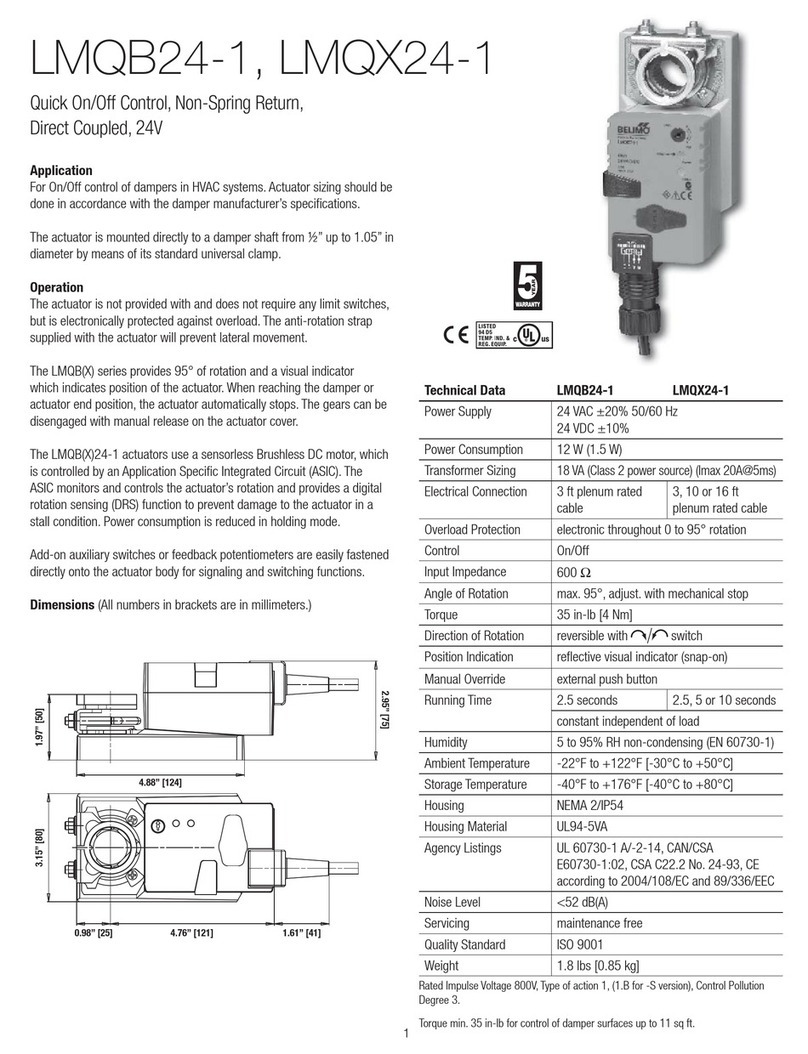

Belimo

Belimo LF-2 Series Product information

Comunello

Comunello RAMPART 1000 Installation and user manual

HighPoint

HighPoint RR640L installation guide

YASKAWA

YASKAWA E-7-Series SGD7S product manual

AMS

AMS XL200 Series Installation guide & technical reference

Honeywell

Honeywell UDC100 PID OPTION MANUAL

Dings

Dings DS-OLS8-FRS4 Technical manual

Circor

Circor RTK REact 30E Series Installation and operating instructions