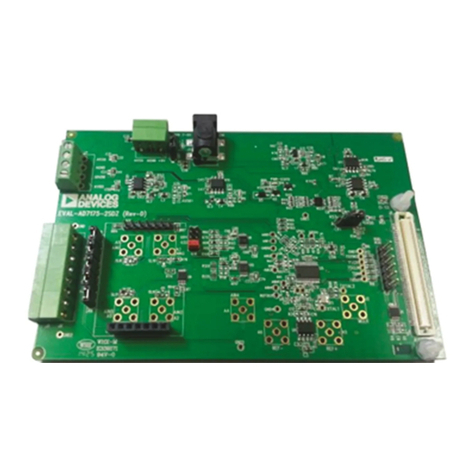

User Guide EVAL-ADAU1861

USING THE EVALUATION BOARD

analog.com Rev. 0 | 10 of 24

CODEC SYSTEM

Clock Option

The EVAL-ADAU1861EBZ has three options for providing a main

clock to the ADAU1861. The default option is to use the on-board

24.576 MHz oscillator. The second option is to provide an external

MCLK signal directly to the XTALI pin of the codec from JP9 and

JP11. The third option is to use the on-board crystal 24.576 MHz.

Refer to Table 4 to check the MCLK settings.

Table 4. MCLK Jumper Settings

Clock Source Jumper Settings External Port

Oscillator Pin 1 to Pin 2 of JP9, Pin 1 to Pin 2 of JP11,

jump JP9 to the left (OSC), and jump JP11 to

the left (MCLK)

Not applicable

Crystal Float JP9 and Pin 2 to Pin 3 of JP11, and jump

JP11 to the right (XTALI_MCLKIN)

Not applicable

External MCLK Pin 2 to Pin 3 of JP9, Pin 1 to Pin 2 of JP11,

jump JP9 to the right (EXT_MCLK), and jump

JP11 to the left (MCLK)

JP9,

EXT_MCLK

pin

Boot-Up Options

Two boot-up options are available for the EVAL-ADAU1861EBZ.

Use JP24 to select the boot-up options, which are self boot enabled

or disabled. When self boot is enabled, the Tensilica HiFi 3z

DSP core of the ADAU1861 loads the program from flash through

QSPI™ with two ROM boot modes that can be selected by JP25.

Power-Down

The EVAL-ADAU1861EBZ can power down all of the analog and

digital circuits of the codec by pressing the S2 button.

AUDIO INPUTS AND OUTPUTS

The EVAL-ADAU1861EBZ has multiple audio input and output

options, including digital and analog, including three analog inputs,

one analog output, eight digital microphone channels, a 2-channel

pulse-density modulation (PDM) output, and two serial audio inter-

face ports.

In addition, for audio tuning, the ADAU1966A also supports a

16-channel digital-to-analog converter. With its default settings, the

ADAU1966A works in standalone mode after power on with a

12.288 MHz oscillator clock input. To save power consumption,

the ADAU1966A works in subordinate mode, 256 × the sampling

frequency (fS), and a TDM 16 with digital audio input from the

ADAU1861 serial audio port, I2S0. To improve performance of the

ADAU1966A output, main mode of the ADAU1966A is suggested

when audio tuning (see Table 5 for additional information).

Table 5. ADAU1966A Configurations

Mode Resistor Installed Resistor Uninstalled

Program R30 R39

Table 5. ADAU1966A Configurations (Continued)

Mode Resistor Installed Resistor Uninstalled

Standalone R39 R30

Main R34 R43

Subordinate R43 R34

To program the ADAU1966A, P14 can be used as the control port

with I2C or SPI.

Analog Inputs

The three analog inputs (P2, P3, and P4) can be configured as

microphone or line inputs. All three inputs are set to differential or

single-ended through JP8, JP9, and JP10. Each analog input can

work with an optional programmable-gain amplifier (PGA). JP5 can

be used to choose mono (only ADC0) or stereo input mode (ADC0

and ADC1).

Refer to Table 6 for the hardware configuration of the analog input

signals. Note that the control register must be changed simultane-

ously.

Table 6. ADC Mode Jumper Settings

ADC No. Mode Jumper Settings

ADC0 Differential Jump JP8 to DIFF

Single-ended Jump JP8 to SINGLE

ADC1 Differential ends Jump JP7 to DIFF

Single-ended Jump JP7 to SINGLE

ADC2 Differential ends Jump JP6to DIFF

Single-ended Jump JP6 to SINGLE

Analog Output

The analog output (P13) can be set as a line output driver or as a

headphone driver. In line output mode, the typical load is 10 kΩ. In

headphone output mode, the typical loads are 16 Ω to 32 Ω. In ad-

dition, the ADAU1966A chip also supports 16 DAC single-channel

analog outputs. Refer to Table 7 for detailed information.

Table 7. DAC Output Interfaces and Signal

Chip Number Function Pin Number and Px Value

ADAU1966A (Single-Ended) DAC1P Pin 3 of P5

DAC2P Pin 2 of P5

DAC3P Pin 3 of P6

DAC4P Pin 2 of P6

DAC5P Pin 3 of P7

DAC6P Pin 2 of P7

DAC7P Pin 3 of P8

DAC8P Pin 2 of P8

DAC9P Pin 3 of P9

DAC10P Pin 2 of P9

DAC11P Pin 3 of P10

DAC12P Pin 2 of P10

DAC13P Pin 3 of P11