Analog Devices AD9161 User manual

Other Analog Devices Motherboard manuals

Analog Devices

Analog Devices ADP5302-EVALZ User manual

Analog Devices

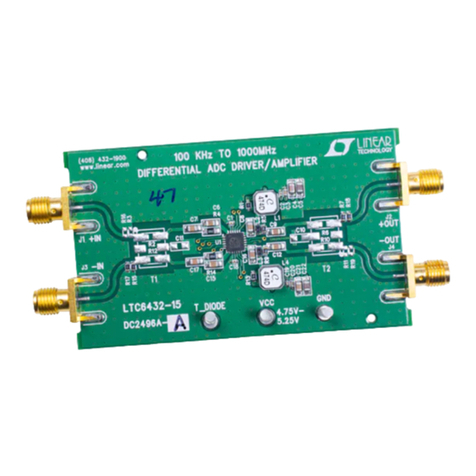

Analog Devices LINEAR DC2496A-A Quick setup guide

Analog Devices

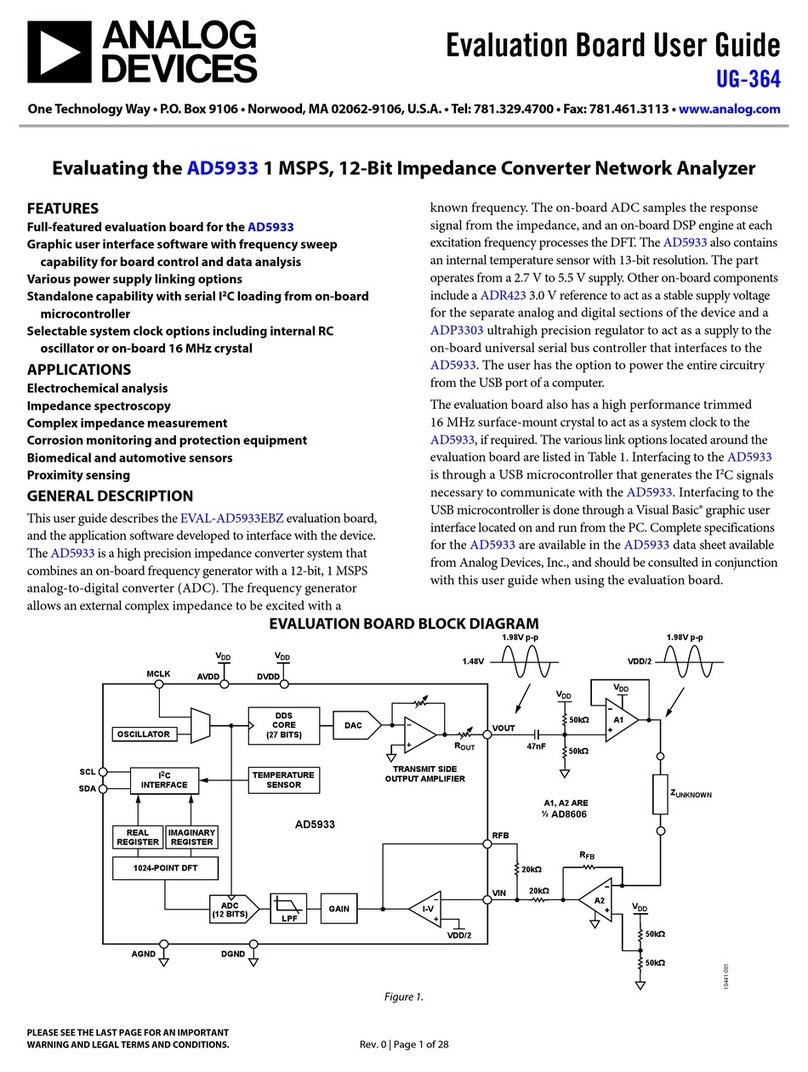

Analog Devices EVAL-AD5933EBZ User manual

Analog Devices

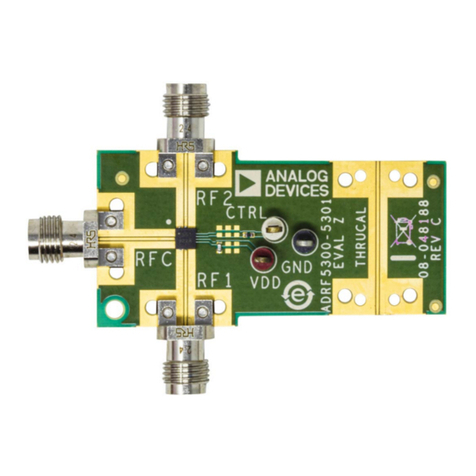

Analog Devices EVAL-ADRF5301 User manual

Analog Devices

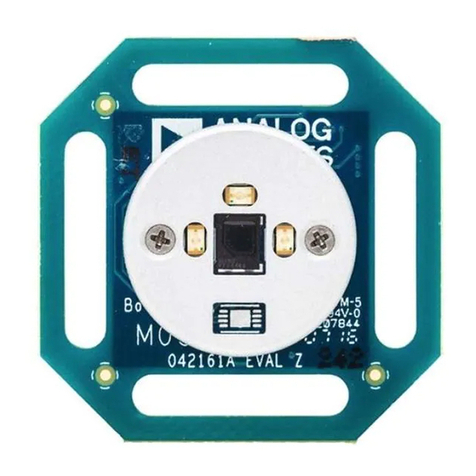

Analog Devices EVAL-ADPD1081Z-PPG User manual

Analog Devices

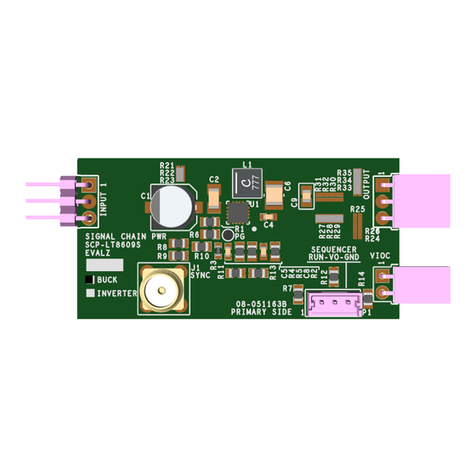

Analog Devices Linear ADI Power SCP-LT8609S-BEVALZ Quick setup guide

Analog Devices

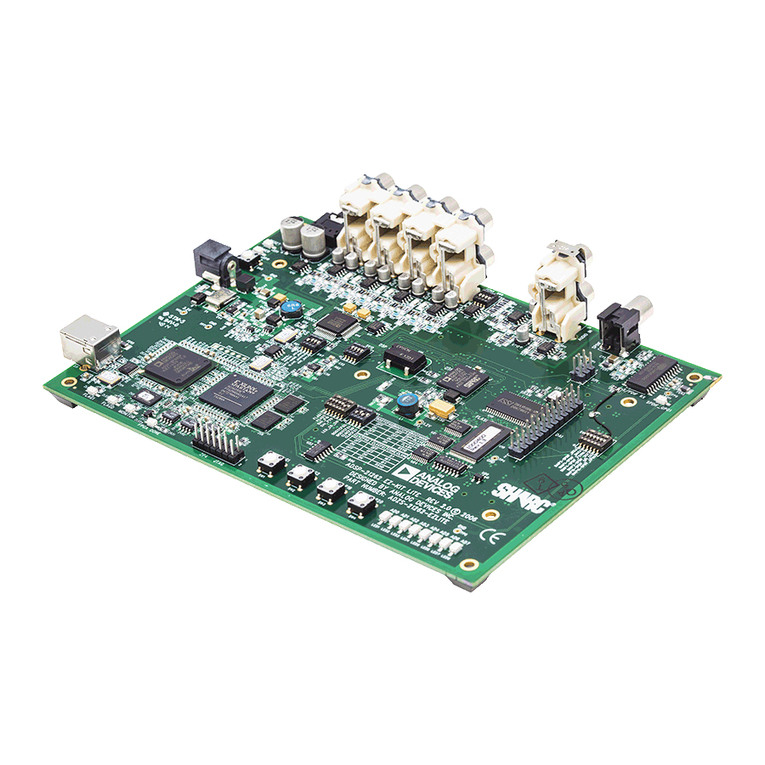

Analog Devices ADSP-21262 EZ-KIT Lite User manual

Analog Devices

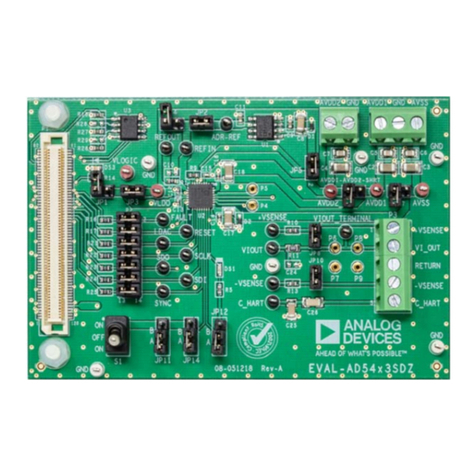

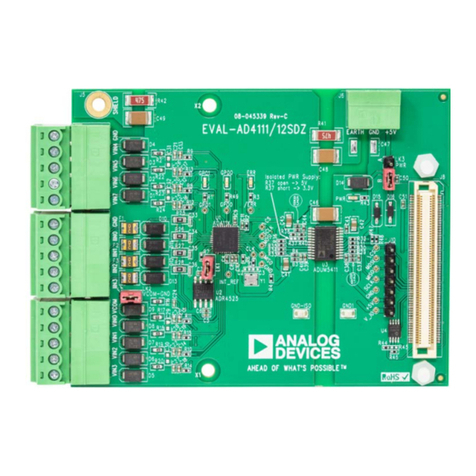

Analog Devices EVAL-AD4111SDZ User manual

Analog Devices

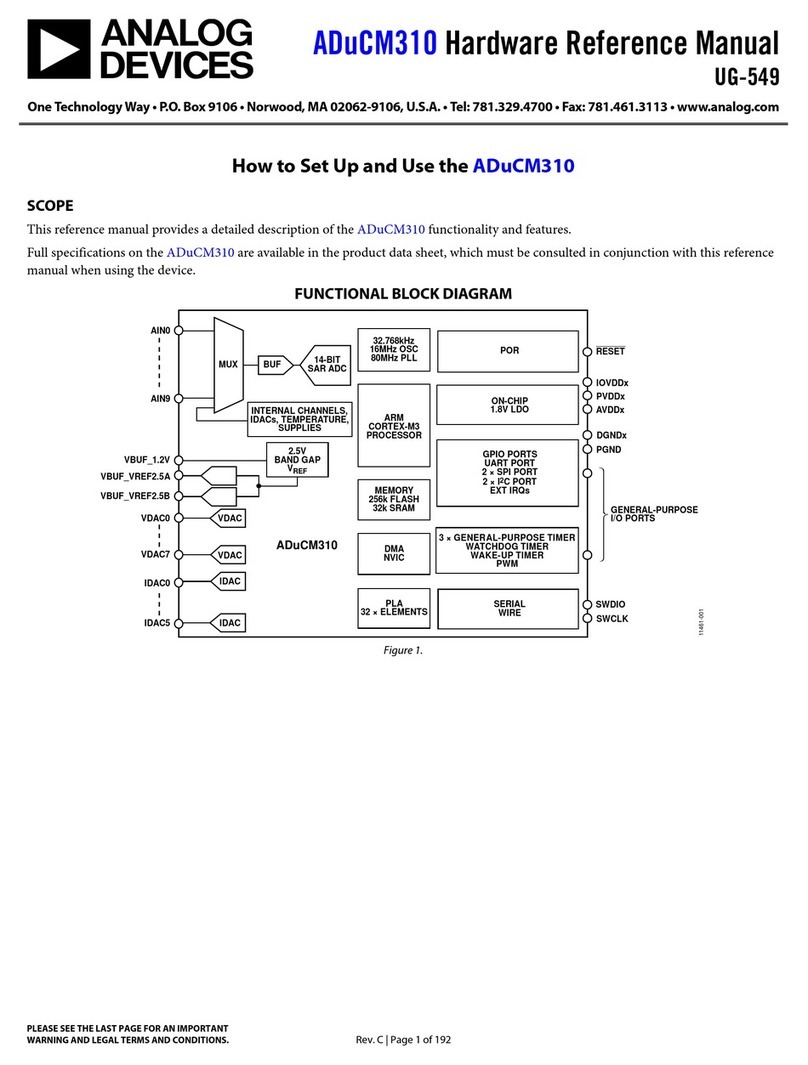

Analog Devices ADuCM310 Quick user guide

Analog Devices

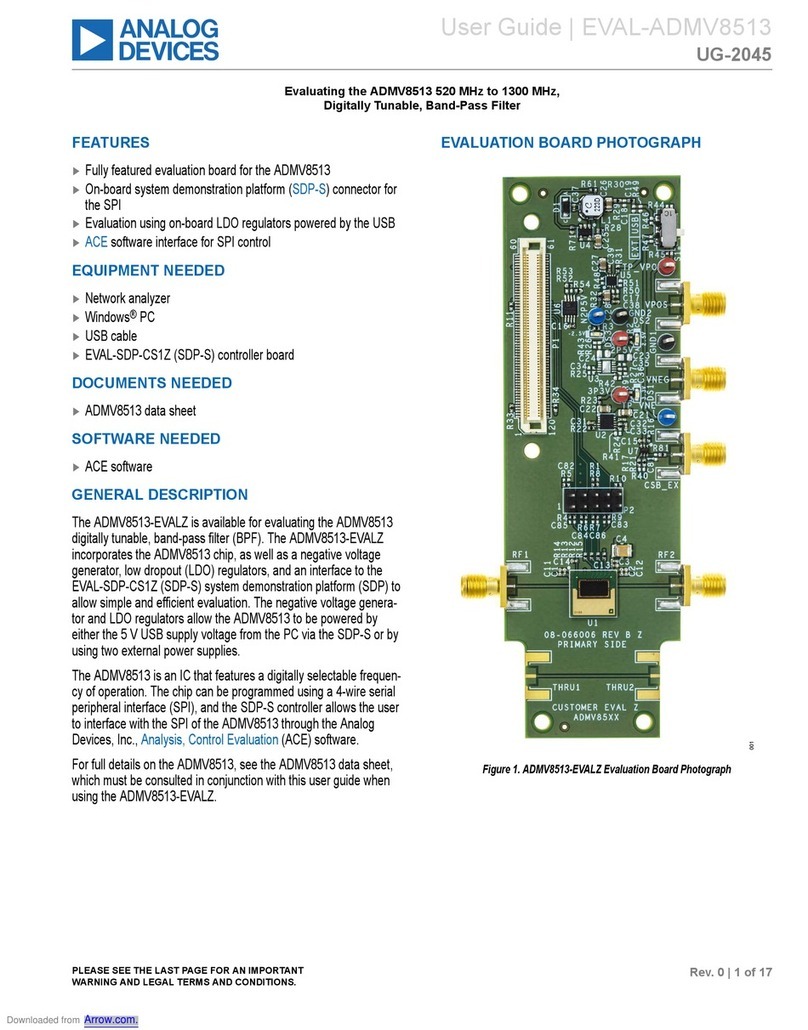

Analog Devices ADMV8513-EVALZ User manual

Analog Devices

Analog Devices DC3186A Quick setup guide

Analog Devices

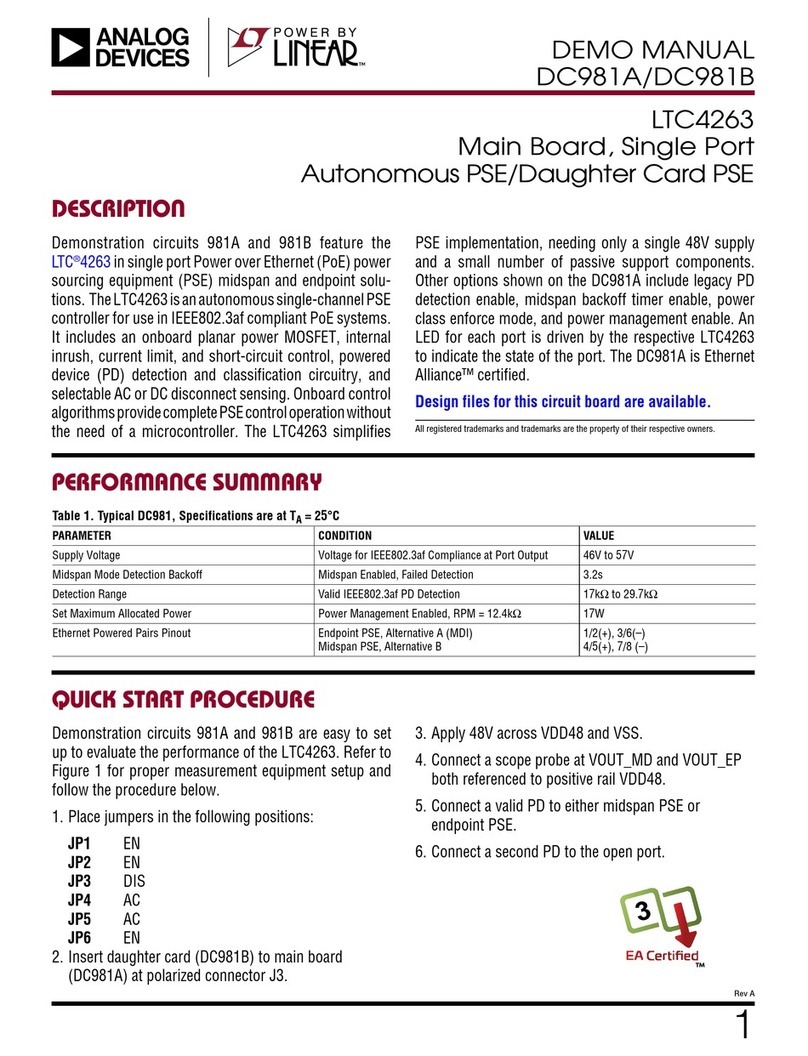

Analog Devices DC981A Quick setup guide

Analog Devices

Analog Devices ADIS16COM1/PCBZ User manual

Analog Devices

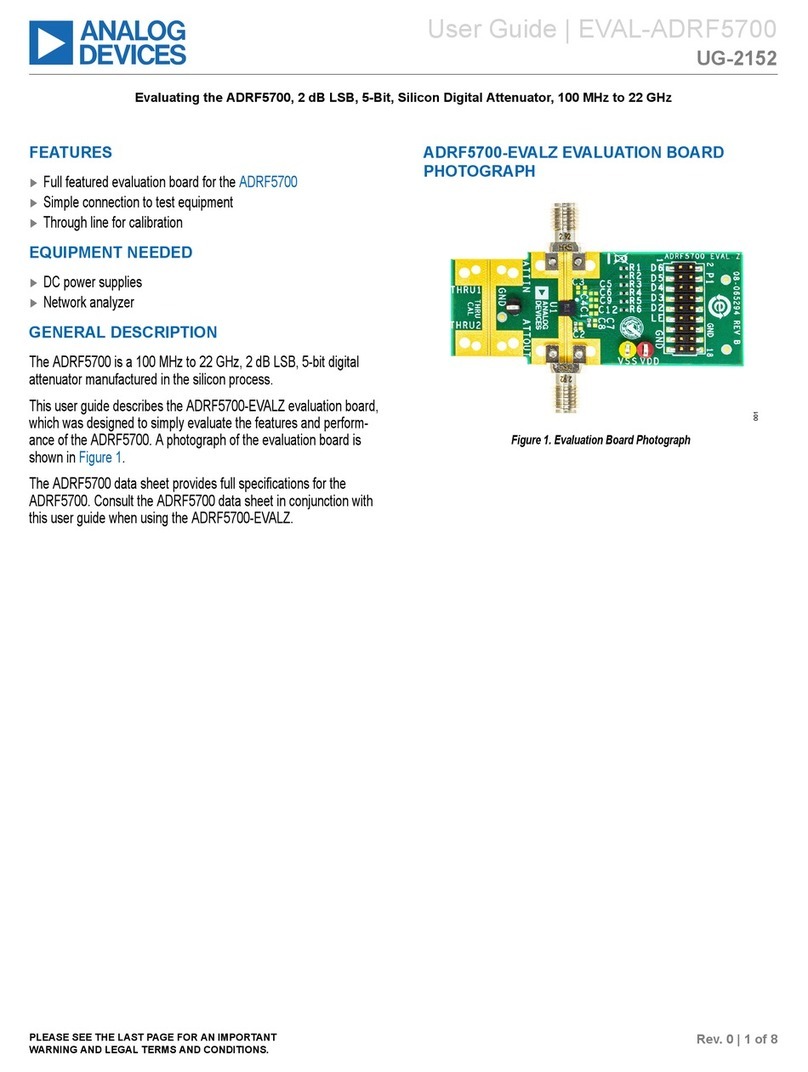

Analog Devices EVAL-ADRF5700 User manual

Analog Devices

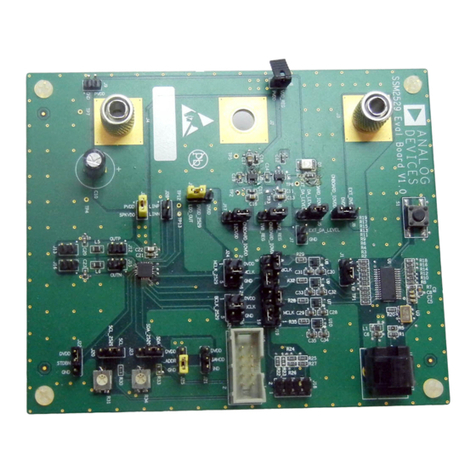

Analog Devices SSM2529 Instruction Manual

Analog Devices

Analog Devices AD9102 User manual

Analog Devices

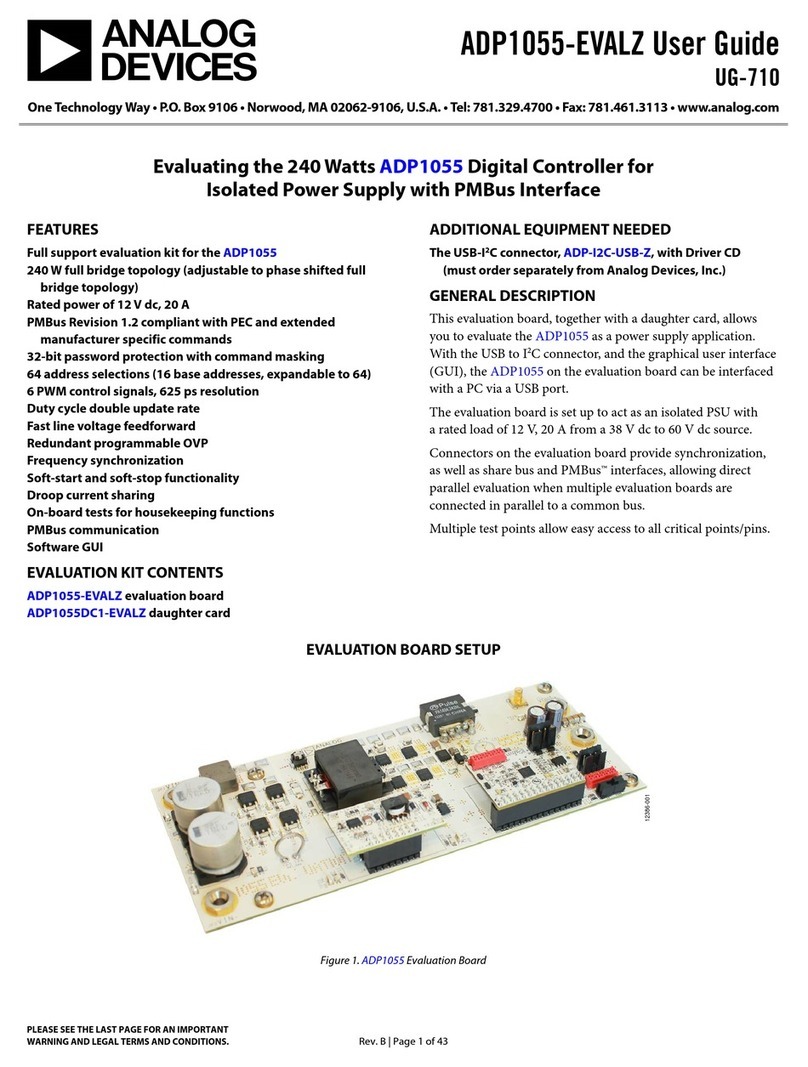

Analog Devices ADP1055-EVALZ User manual

Analog Devices

Analog Devices EVAL-AD7175-2SDZ User manual

Analog Devices

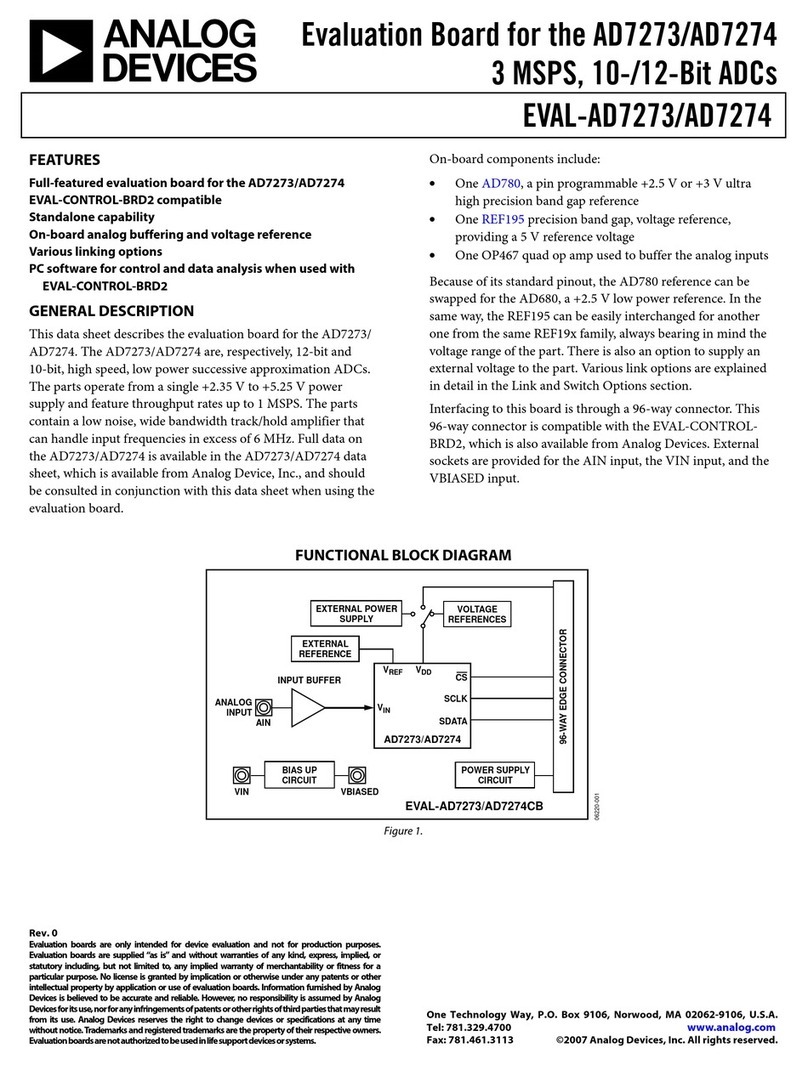

Analog Devices AD7273 User manual

Analog Devices

Analog Devices ADSP-BF535 EZ-KIT Lite User manual