I/O I/O K1 K/ ( 1 )

I/O K1 K2

c)

(Buzzer) 1 I/O FPGA 11 FPGA 1

Buzzer Buzzer 0 I/O Buzzer I/O 40 K3

I/O K3 Buzzer Jumper J3

11 Buzzer FPGA

4.2)

K1- K4 I/O 1 K1- K4

(Cross talk) (Flat

Cable)

I/O K1 K4

()

LED I/O 3 3V

40 1520 (

- CD )

I/O FPGA Slow Slew Rate

Transmission Line

effect PCB < (2/nS) x (Rise time)

O/P FPGA Fastslew rate < 1 nS Slow slew rate

< 3 nS (2/nS) x 3 nS = 6 = 15 ( 20 )

Terminate

Vcc 0 1 uF 10 nF

(Chip capacitor) Vcc (

) Vcc AC

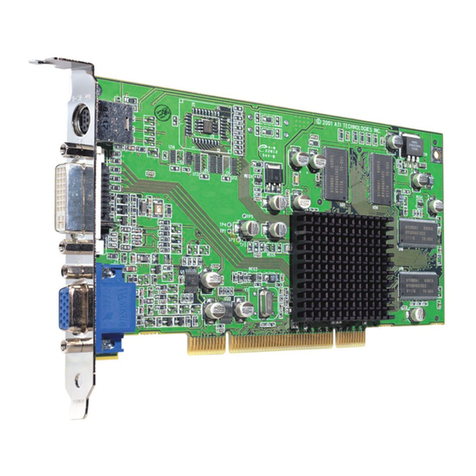

Vcco 3 3V I/O 3 3V I/O 2

LVCMOS33 LVTTL 2 FPGA LVTTL (IOSTANDARD = LVTTL)

Slow slew Rate (SLEW = SLOW) Edit Constraints(Text)12 PACE 13

FPGA 3 3V 5V ( 74LS00, 74HCT00) FPGA

3 3V FPGA 5 V 14(a)

CPLD XC9500XL 3 3V 5V 14(b) (Pulled up)

Jumper J2 J2