AS3990/AS3991

UHF RFID Single Chip Reader EPC Class1 Gen2 Compatible

www.austriamicrosystems.com/AS3990

www.austriamicrosystems.com/AS3991 Revision 3.9 1 - 51

Datasheet

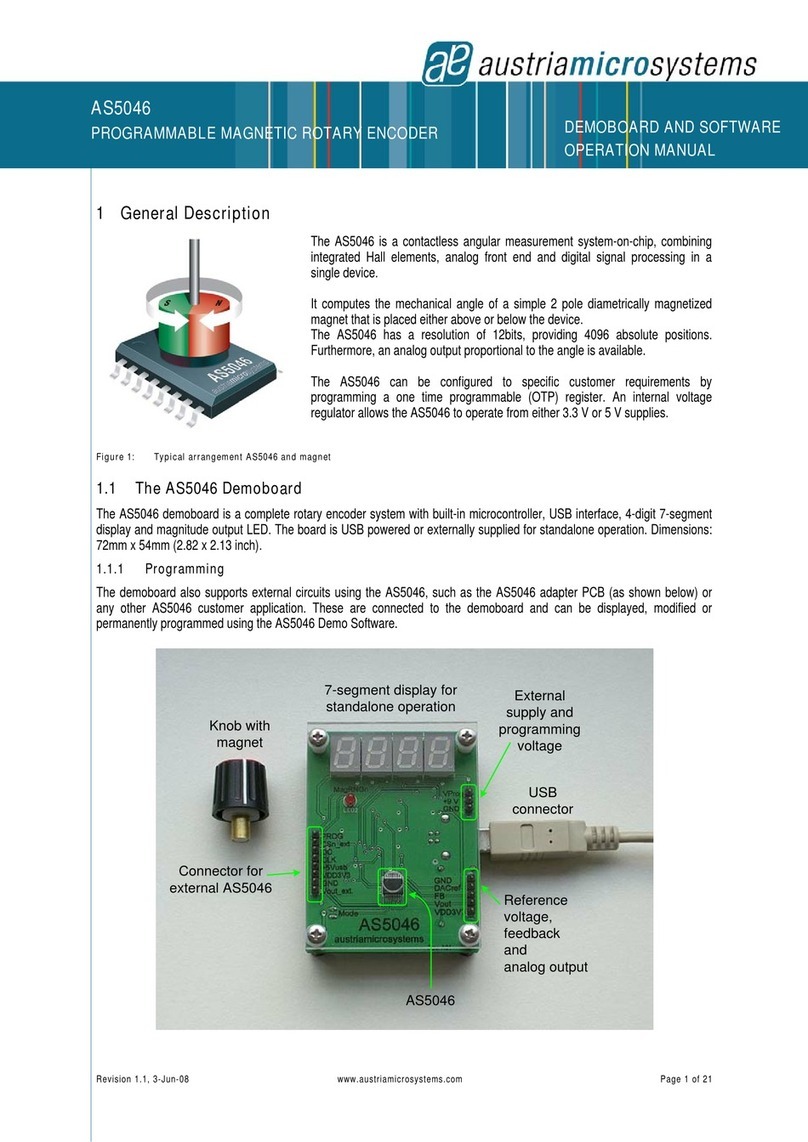

1 General Description

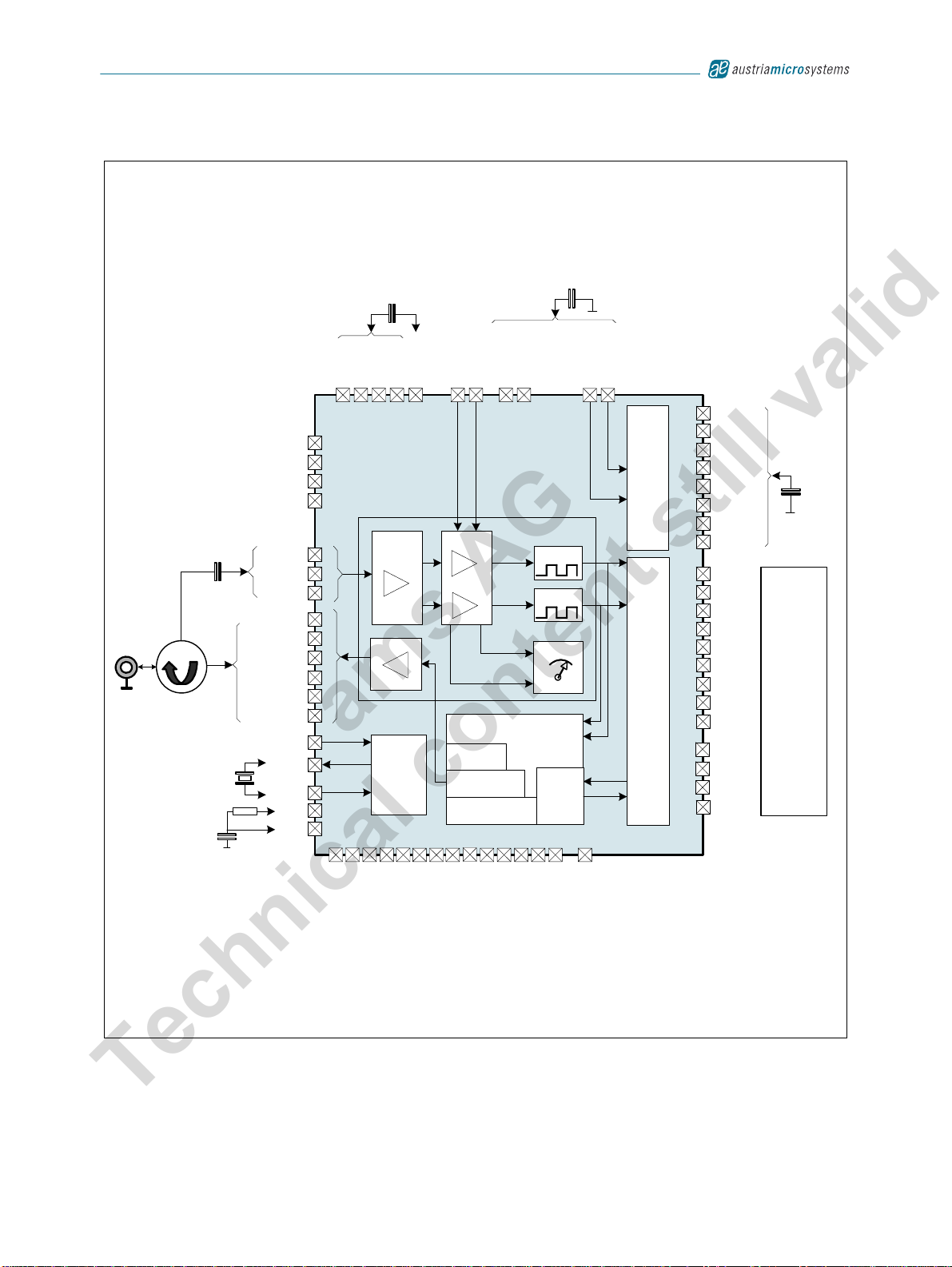

The AS3990/AS3991 UHF reader chip is an integrated analog front

end and protocol handling systems for a ISO18000-6C 900MHz

RFID reader system.

Equippedwithbuilt-inprogrammingoptions,thedeviceissuitablefor

a wide range of UHF RFID applications. The AS3990/AS3991

includes improved on-board VCO and internal PA.

The reader configuration is achieved by selecting the desired

protocol in control registers. Direct access to all control registers

allows fine tuning of different reader parameters.

Parallel or serial interface can be selected for communication

between the host system (MCU) and the reader IC. When hardware

coders and decoders are used for transmission and reception, data

is transferred via 24 bytes FIFO register.

In case of direct transmission or reception, coders and decoders are

bypassed and the host system can service the analog front end in

real time.

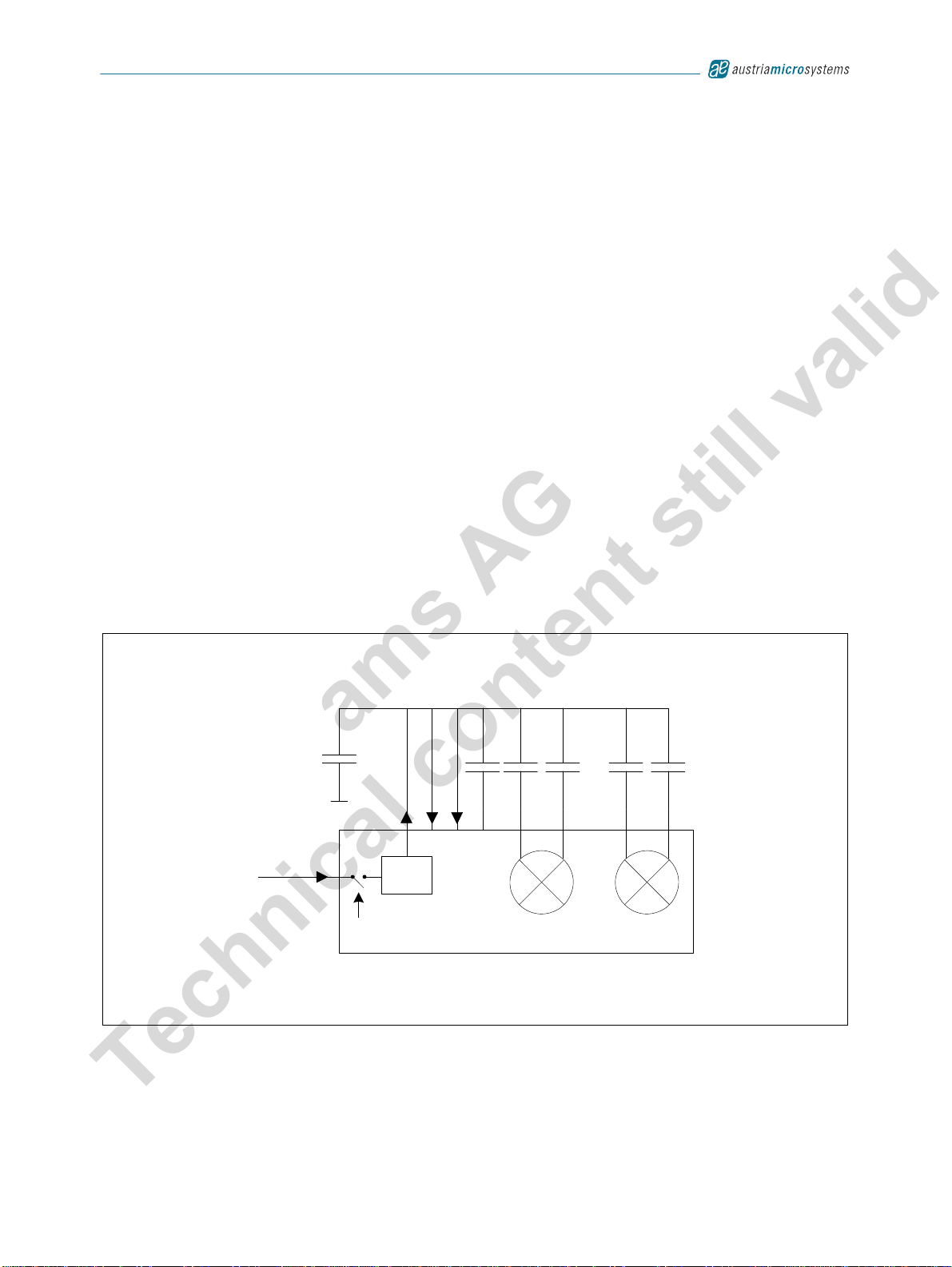

Thetransmitter generates20dBmoutput power into50Ωload and is

capable of ASK or PR-ASK modulation. The integrated supply

voltage regulators ensure supply rejection of the complete reader

system.

Thetransmissionsystemcompriseslowleveldatacoding.Automatic

generation of FrameSync, Preamble, and CRC is supported.

The receiver system allows AM and PM demodulation. The receiver

also comprises automatic gain control option (patent pending) and

selectable gain and signal bandwidth to cover a range of input link

frequency and bit rate options.

The signal strength of AM and PM modulation is measured and can

be accessed in RSSI register.

Thereceiveroutputis selectablebetweendigitized sub-carriersignal

and any of integrated sub-carrier decoders. Selected decoders

deliver bit stream and data clock as outputs.

The receiver system also comprises framing system. This system

performs the CRC check and organizes the data in bytes. Framed

data is accessible to the host system through a 24 byte FIFO

register.

To support external MCU and other circuitry a 3.3V regulated supply

and clock outputs are available. The regulated supply has 20mA

current capability.

The AS3990/AS3991 is available in a 64-pin QFN (9mm x 9mm),

ensuring the smallest possible footprint.

2 Key Features

Filters dedicated to 250kHz and 320kHz M4 and M8 DRM

operation. Available RX modes:

- LF40kHz, 160kHz: FM0, M2, M4, M8

- LF 250kHz, 320kHz, 640kHz: M4, M8

ISO18000-6C (EPC Gen2) full protocol support

ISO18000-6A,B compatibility in direct mode

Integrated low level transmission coding

Integrated low level decoders

Integrated data framing

Integrated CRC checking

Parallel 8-bit or serial4-pinSPIinterface to MCU using24bytes

FIFO

Voltage range for communication to MCU between 1.8V and

5.5V

Selectable clock output for MCU

Integrated supply voltage regulator (20mA), which can be used

to supply MCU and other external circuitry

Integrated supply voltage regulator for the RF output stage,

providing rejection to supply noise

Internal power amplifier (20dBm) for short range applications

Modulator using ASK or PR-ASK modulation

Adjustable ASK modulation index

AM & PM demodulation ensuring no“communication holes”

with automatic I/Q selection

Built-in reception low-pass and high-pass filters having select-

able corner frequencies

Selectable reception gain

Reception automatic gain control

AD converter for measuring TX power using external RF power

detector

DA converter for controlling external power amplifier

Frequency hopping support

On-board VCO and PLL covering complete RFID frequency

range 840MHz to 960MHz

Oscillator using 20MHz crystal

Power down, standby and active mode

Can be powered by USB with no need for step conversion

3 Applications

The device is an ideal solution for UHF RFID reader systems and

hand-held UHF RFID readers.

ams AG

Technical content still valid