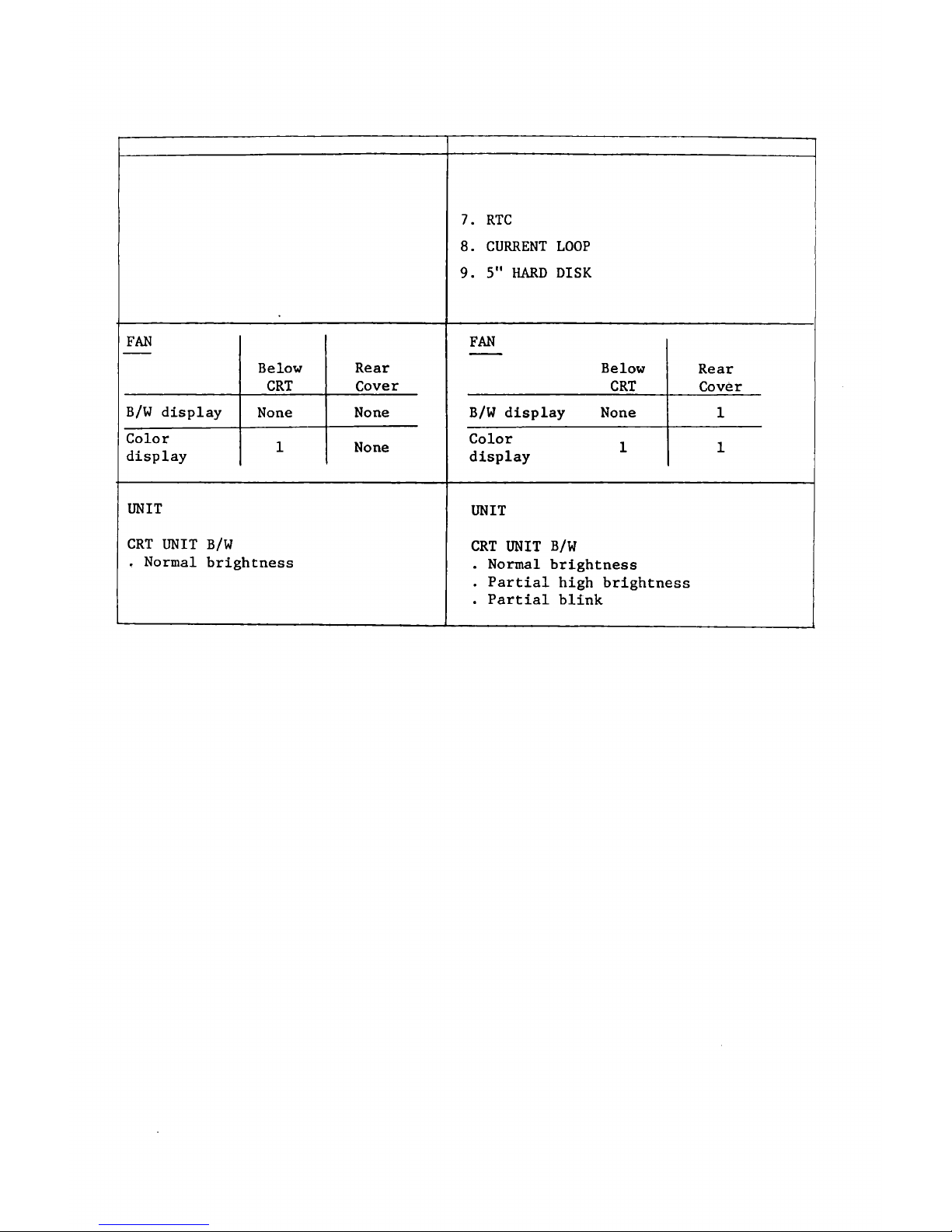

1.1.2 Models Table 1.1.1

Abbrevia

tion Model Symbol Configuration & outline Remarks

MAIN

UNIT

AS-100C E21-0021

. 12n color graphic display

. Standard 256KB main memory .

. The interfaces respectively for printer,

keyboard, and floppy disk are incorporated.

AS-100M E21-0011

. 12" B/W graphic display

. Standard 256KB main memory

. The interfaces respectively for the printer,

keyboard, and floppy disk are incorporated.

KEYBOARD AS KEYBOARD ASCII A-llll E21-0040 . ASCII Key + 10-key

5" FDD Minifloppy disk A-1300 E71-0050 . 2 sides, double density, double tracks,

mini drive x 2

. File capacity: 1.4MB (max)

8" FDD Floppy disk A-1330 E71-0061 • 2 sides, double desntiy, standard slim

drive x 2

. File capacity: 2.5MB (max)

PRINTER

Dot impact printer A-1200 E71-0081

. 9-pin wire dot, serial

.. 80 characters, 120CPS

. 480-dot image print

DP-7RG and

X-8220A are

applicable

Color printer A-1210 E63-0011

. 4-nozzle inkjet

. 80 characters, 40 CPS

. 560-dot image print

. 7-color print

Note: KSR for AP400/500 is applicable