Crystal CS4231A User manual

Features

•Windows Sound SystemTM

Compatible Codec

•ADPCM Compression/Decompression

•Extensive Software Support

•MPC Level 2 Compatible Mixer

•Dual DMA Registers support Full

Duplex Operation

•On-Chip FIFOs for higher performance

•Selectable Serial Audio Data Port

•Pin Compatible with CS4231/CS4248

General Description

The CS4231A includes stereo 16-bit audio converters

and complete on-chip filtering for record and playback

of 16-bit audio data. In addition, analog mixing and

programmable gain and attenuation are included to

provide a complete audio subsystem. A selectable se-

rial port can pass audio data to and from DSPs or

ASICs. Crystal-developed high-performance software

drivers for various operating systems are available that

support all the CS4231A features including full duplex

transfers. The CS4231A is a pin compatible upgrade to

the CS4231 and CS4248.

ORDERING INFORMATION:

CS4231A-KL 0 to 70°C 68-pin PLCC

CS4231A-KQ 0 to 70°C 100-pin TQFP

SEPT ’94

DS139PP2

1

Crystal Semiconductor Corporation

P.O. Box 17847, Austin, TX 78760

(512) 445-7222 Fax: (512) 445-7581

Parallel Interface, Multimedia Audio Codec

Semiconductor Corporation CS4231A

This document contains information for a new product. Crystal

Semiconductor reserves the right to modify this product withoutnotice.

Preliminary Product Information

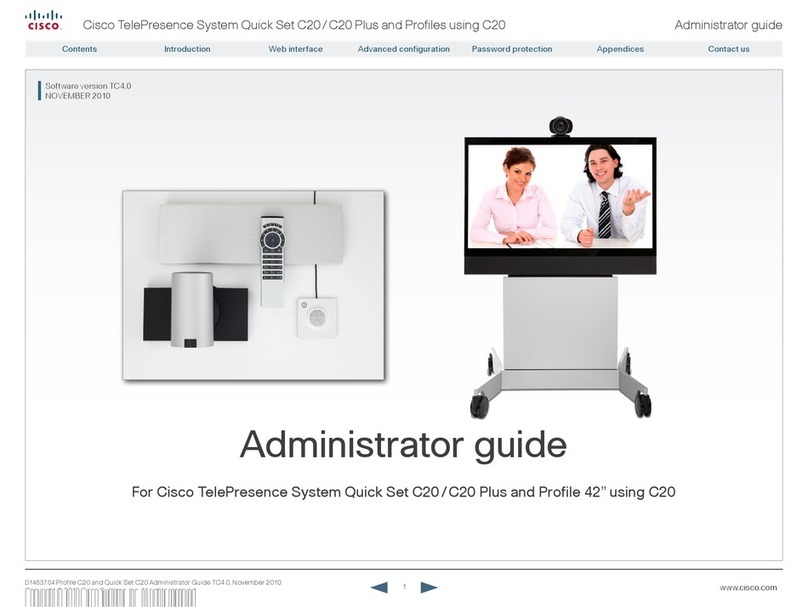

Mute

Gain

Gain

Mux

LMIC

RMIC

LLINE

RLINE

LAUX1

RAUX1

LOUT

ROUT

RAUX2

LAUX2

Mute

AGND1 AGND2

DAC

Attenuate

20dB Gain

VREF VREFI

VREF

XTAL2I XTAL2O

Oscillators

LFILT RFILT

D<7:0>

A<1:0>

CS

WR

PDRQ

CDRQ

PDAK

CDAK

8

2

IRQ

DBDIR

DBEN

XCTL1

XCTL0

Parallel

Bus

Interface

PDWN

Mute

MIN

MOUT

Linear

µ

-law

A-law

ADPCM

Linear

µ

-law

A-law

ADPCM

DGND3/4/7/8DGND1 DGND2 XTAL1I XTAL1O

VD1

VD2

FIFO

16

Samples

VD3 VD4

16 Bit Timer

VA1 VA2

16-bit

A/D

16-bit

A/D

Mix

Gain

Mix

Gain

Mix

Gain

Mix

Gain

16-bit

D/A

16-bit

D/A

Optional

Dither

Loopback

Digital

Attenuation

RD

FIFO

16

Samples

SDOUT

SDIN

SCLK FSYNC

I4

I5

I3

I2

I26

I8

I18

I19

I26

I1

I0

I0

I1

I0

I1

I13

I10

I8

I8 or I28

I20,I21

I 16

I6

I7

TEST

Audio Data Serial Port

I16

Copyright

Crystal Semiconductor Corporation 1994

(All Rights Reserved)

TABLE OF CONTENTS:

CS4231A TECHNICAL SPECIFICATIONS..............3

GENERAL DESCRIPTION .......................................11

Enhanced Functions (MODE 2)..............................12

Mixer Attenuation Control on Line Input ..............12

ANALOG HARDWARE DESCRIPTION...................12

Analog Inputs..........................................................12

Line-Level Inputs plus MPC Mixer .......................13

Microphone Level Inputs......................................13

Mono Input with Attenuation and Mute................13

Analog Outputs .......................................................13

Mono Output with Mute Control ...........................14

Miscellaneous Analog Signals................................14

DIGITAL HARDWARE DESCRIPTION....................14

Parallel Data Interface ............................................14

FIFOs ......................................................................14

High Current Data Bus Drivers...............................15

PIO Registers Interface...........................................15

DMA Interface.........................................................15

Dual DMA Channel Mode ....................................16

Single DMA Channel (SDC) Mode.......................16

Serial Audio Data Port............................................16

Miscellaneous Signals.............................................18

Crystals/Clocks.....................................................18

Power Down - PDWN ..........................................19

DBEN/DBDIR .......................................................19

SOFTWARE DESCRIPTION ....................................19

Power-Down and Initialization.................................19

Calibration Modes...................................................20

Changing Sampling Rate........................................21

Changing Audio Data Formats ...............................21

Audio Data Formats................................................21

16-bit Signed ........................................................22

8-bit Unsigned ......................................................22

8-bit Companded..................................................22

ADPCM Compression/Decompression ................25

DMA Registers........................................................25

Playback DMA Registers......................................26

Capture DMA Registers .......................................26

Digital Loopback......................................................26

Timer Registers.......................................................27

Interrupts.................................................................27

Error Conditions......................................................27

CS4231A REGISTER MAPPING .............................28

Physical Mapping....................................................28

Index Address Register................ (R0)................29

Index Data Register ..................... (R1)................29

Status Register............................. (R2, RO)........29

Capture I/O Data Register ........... (R3, RO)........30

Playback I/O Data Register ......... (R3, WO) .......31

Left ADC Input Control................. (I0) .................31

Right ADC Input Control .............. (I1) .................31

Left Auxiliary #1 Input Control...... (I2) .................31

Right Auxiliary #1 Input Control... (I3) .................32

Left Auxiliary #2 Input Control...... (I4) .................32

Right Auxiliary #2 Input Control... (I5) .................32

Left DAC Output Control.............. (I6) .................32

Right DAC Output Control ........... (I7).................32

Fs and Playback Data Format..... (I8) .................33

Interface Configuration................. (I9) .................34

Pin Control ................................... (I10) ...............35

Error Status and Initialization....... (I11, RO)........35

MODE and ID............................... (I12) ...............36

Loopback Control......................... (I13) ...............36

Playback Upper Base .................. (I14) ...............36

Playback Lower Base .................. (I15) ...............36

Alternate Feature Enable I........... (I16) ...............37

Alternate Feature Enable II.......... (I17) ...............37

Left Line Input Control.................. (I18) ...............37

Right Line Input Control............... (I19) ...............40

Timer Lower Base........................ (I20) ...............40

Timer Upper Base........................ (I21) ...............40

Alternate Feature Enable III......... (I23) ...............40

Alternate Feature Status.............. (I24) ...............41

Version/ Chip ID........................... (I25) ...............41

Mono Input & Output Control....... (I26) ...............41

Capture Data Format ................... (I28) ...............42

Capture Upper Base .................... (I30) ...............42

Capture Lower Base .................... (I31) ...............42

GROUNDING AND LAYOUT ...................................43

COMPATIBILITY WITH AD1848..............................43

ADC/DAC FILTER RESPONSE PLOTS..................45

PIN DESCRIPTIONS ................................................47

PARAMETER DEFINITIONS....................................54

APPENDIX A ............................................................55

PACKAGE DIMENSION...........................................56

CDB4231/4248 Data Sheet......................................57

CS4231A

2DS139PP2

ANALOG CHARACTERISTICS (TA= 25 °C; VA1, VA2, VD1-VD4 = +5V;

Input Levels: Logic 0 = 0V, Logic 1 = VD1-VD4; 1 kHz Input Sine wave; Conversion Rate = 48 kHz;

Measurement Bandwidth is 10 Hz to 20 kHz, 16-bit linear coding.)

Parameter* Symbol Min Typ Max Units

Analog Input Characteristics

- Minimum Gain Setting (0dB); unless otherwise specified.

ADC Resolution (Note 1) 16 Bits

ADC Differential Nonlinearity (Note 1) ±0.5 LSB

Instantaneous Dynamic Range Line Inputs

(Note 2) Mic Inputs IDR 80

72 85

77 dB

dB

Total Harmonic Distortion Line Inputs

Mic Inputs THD 0.006

0.01 0.02

0.025 %

%

Signal-to-Intermodulation Distortion 90 dB

Interchannel Isolation Line to Line Inputs

Line to Mic Inputs

Line-to-AUX1

Line-to-AUX2

80

80

90

90

dB

dB

dB

dB

Interchannel Gain Mismatch Line Inputs

Mic Inputs 0.5

0.5 dB

dB

Programmable Input Gain Span Line Inputs 21.5 22.5 dB

Gain Step Size 1.3 1.5 1.7 dB

ADC Offset Error 0 dB gain 10 100 LSB

Full Scale Input Voltage: (MGE=1) MIC Inputs

(MGE=0) MIC Inputs

LINE, AUX1, AUX2, MIN Inputs

0.266

2.66

2.66

0.29

2.9

2.9

0.31

3.1

3.1

Vpp

Vpp

Vpp

Gain Drift 100 ppm/°C

Input Resistance (Note 1) 20 kΩ

Input Capacitance (Note 1) 15 pF

Notes: 1. This specification is guaranteed by characterization, no production testing.

2. MGE = 1 and a 10 µF capacitor on the VREF pin.

*Parameter definitions are given at the end of this data sheet.

Windows and Windows Sound System are registered trademarks of Microsoft Corporation.

Specifications are subject to change without notice.

CS4231A

DS139PP2 3

ANALOG CHARACTERISTICS (Continued)

Parameter* Symbol Min Typ Max Units

Analog Output Characteristics

- Minimum Attenuation (0dB); unless otherwise specified.

DAC Resolution 16 Bits

DAC Differential Nonlinearity (Note 1) ±0.5 LSB

Dynamic Range -Total All Outputs

-Instantaneous TDR

IDR 80 95

85 dB

dB

Total Harmonic Distortion (Note 3) THD 0.01 0.02 %

Signal-to-Intermodulation Distortion 85 dB

Interchannel Isolation Line Out (Note 3) 95 dB

Interchannel Gain Mismatch Line Out 0.1 0.5 dB

Voltage Reference Output 2.0 2.2 2.35 V

Voltage Reference Output Current (Note 4) 100 µA

DAC Programmable Attenuation Span 93 94.5 dB

DAC Attenuation Step Size 0 dB to -81 dB

-82.5 dB to -94.5 dB 1.3

1.0 1.5

1.5 1.7

2dB

dB

DAC Offset Voltage 1 10 mV

Full Scale Output Voltage: OLB = 0 (Notes 3, 5)

OLB = 1 OUT, MOUT 1.8

2.6 2.0

2.8 2.25

3.2 Vpp

Vpp

Gain Drift 100 ppm/°C

Deviation from Linear Phase (Note 1) 1 Degree

External Load Impedance 10 kΩ

Mute Attenuation (0 dB) 80 dB

Total Out-of-Band Energy 0.6xFs to 100 kHz (Note 1) -45 dB

Audible Out-of-Band Energy 0.6xFs to 22 kHz (Fs=8kHz) -60 dB

Power Supply

Power Supply Current Digital, Operating

Analog, Operating

Total

Digital, Power Down

Analog, Power Down

55

43

98

0.1

0.8

65

60

120

1

1

mA

mA

mA

mA

mA

Power Supply Rejection 1 kHz (Note 1) 40 dB

Notes: 3. 10 kΩ, 100 pF load.

4. DC current only. If dynamic loading exists, then the voltage reference output must be buffered

or the performance of ADCs and DACs will be degraded.

5. All mixer and output gain tables assume the output level bit, OLB, in indirect register 16 (I16) is set,

wherein the input and output full scale values are equal. When OLB=0, the output value is 3 dB

below the input value, given no gain or attenuation.

CS4231A

4DS139PP2

ABSOLUTE MAXIMUM RATINGS (AGND, DGND = 0V, all voltages with respect to 0V.)

Parameter Symbol Min Max Units

Power Supplies: Digital

Analog VD1-VD4

VA1,VA2 -0.3

-0.3 6.0

6.0 V

V

Input Current per Pin (Except Supply Pins) -10.0 +10.0 mA

Output Current per Pin (Except Supply Pins) -50 +50 mA

Analog Input Voltage -0.3 VA+0.3 V

Digital Input voltage -0.3 VD+0.3 V

Ambient Temperature (Power Applied) -55 +125 °C

Storage Temperature -65 +150 °C

Warning: Operation beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

RECOMMENDED OPERATING CONDITIONS (AGND, DGND = 0V, all voltages with repect

to 0V.)

Parameter Symbol Min Typ Max Units

Power Supplies: Digital

Analog VD1-VD4

VA1,VA2 4.75

4.75 5.0

5.0 5.25

5.25 V

V

Operating Ambient Temperature TA02570°C

AUXILIARY INPUT MIXERS (TA = 25 °C; VA1, VA2, VD1-VD4 = +5V;

Input Levels: Logic 0 = 0V, Logic 1 = VD1-VD4; 1 kHz Input Sine wave)

Parameter Symbol Min Typ Max Units

Mixer Gain Range Span LINE, AUX1, AUX2 (Note 6)

MIN 45

42 46.5

45 dB

dB

Step Size LINE, AUX1, AUX2

MIN 1.3

2.3 1.5

3.0 1.7

3.4 dB

dB

Notes: 6. All mixer gain values assume OLB=1. If OLB=0, the analog output will be 3 dB below listed settings.

CS4231A

DS139PP2 5

DIGITAL CHARACTERISTICS (TA= 25°C; VA1, VA2, VD1-VD4 = 5V;

AGND1, AGND2, DGND1-DGND4, DGND7, DGND8 = 0V.)

Parameter Symbol Min Max Units

High-level Input Voltage Digital Inputs

XTAL1I, XTAL2I, PDWN VIH 2.0

VD-1.0 VD+0.3

VD+0.3 V

V

Low-level Input Voltage VIL -0.3 0.8 V

High-level Output Voltage: D<7:0> I0= -16.0 mA

All Others I0= -1.0 mA VOH 2.4

2.4 VD

VD V

V

Low-level Output Voltage: D<7:0> I0= 16.0 mA

All Others I0= 4.0 mA VOL 0.4

0.4 V

V

Input Leakage Current (Digital Inputs) -10 10 µA

Output Leakage Current (High-Z Digital Outputs) -10 10 µA

DIGITAL FILTER CHARACTERISTICS

Parameter Symbol Min Typ Max Units

Passband 0 0.40xFs Hz

Frequency Response -0.5 +0.2 dB

Passband Ripple (0-0.4xFs) ±0.1 dB

Transition Band 0.40xFs 0.60xFs Hz

Stop Band 0.60xFs Hz

Stop Band Rejection 74 dB

Group Delay 16- and 8-bit formats

ADPCM stereo format

ADPCM mono format

10/Fs

14/Fs

18/Fs

s

s

s

Group Delay Variation vs. Frequency ADCs

DACs 0.0

0.1/Fs µs

µs

CS4231A

6DS139PP2

TIMING PARAMETERS (TA= 25 °C; VA1, VA2, VD1-VD4 = +5V, outputs loaded with 30 pF;

Input Levels: Logic 0 = 0V, Logic 1 = VD1-VD4)

Parameter Symbol Min Max Units

WR or RD strobe width tSTW 90 ns

Data valid to WR rising edge (write cycle) tWDSU 22 ns

RD falling edge to data valid (read cycle) tRDDV 60 ns

CS setup to WR of RD falling edge tCSSU 10 ns

CS hold from WR or RD rising edge tCSHD 0ns

ADDR <> setup to RD or WR falling edge tADSU 22 ns

ADDR <> hold from WR or RD rising edge tADHD 10 ns

DAK inactive to WR or RD falling edge (DMA cycle

completion immediately followed by a non-DMA cycle) tSUDK1 60 ns

DAK active from WR or RD rising edge (non-DMA cycle

completion immediately followed by DMA cycle) tSUDK2 0ns

DAK setup to RD falling edge (DMA cycles)

DAK setup to WR falling edge tDKSUa

tDKSUb 25

25 ns

ns

Data hold from WR rising edge tDHD2 15 ns

DRQ hold from WR or RD falling edge

(assumes no more DMA cycles needed) tDRHD 025ns

Time between rising edge of WR or RD to next falling edge

of WR or RD tBWND 80 ns

Data hold from RD rising edge tDHD1 020ns

DAK hold from WR rising edge

DAK hold from RD rising edge tDKHDa

tDKHDb 25

25 ns

ns

DBEN or DBDIR active from WR or RD falling edge tDBDL 40 ns

PDWN pulse width low tPDWN 200 ns

Crystals, XTAL1I, XTAL2I frequency (Notes 1,7,8) 25.6 MHz

XTAL1I, XTAL2I high time (Notes 1,8) 18 ns

XTAL1I, XTAL2I low time (Notes 1,8) 18 ns

Sample frequency (Note 1) Fs 5.5 50 kHz

Serial Port Timing

SCLK frequency (Note 9) tSCLKW Fsx64 Hz

SCLK rising to SDOUT valid tPD1 30 ns

SCLK rising to FSYNC transition tPD2 -20 20 ns

SDIN valid to SCLK falling tS1 30 ns

SDIN hold after SCLK falling tH1 30 ns

Notes: 7. When only one crystal is used, it must be XTAL1. When using two crystals, the high frequency

crystal should be on XTAL1 which is designed for higher loop gains.

8. Sample frequency specifications must not be exceeded.

9. When SF1, 0 = 10, 32-bit mode, SCLK is active for the first 32 bit periods of the frame, and remains

low during the last 32 bit periods of the frame.

CS4231A

DS139PP2 7

tDRHD

tDBDL tDKHDb

tDHD1

tRDDV

tDKSUa

tSTW

CDRQ

CDAK

DBEN

D<7:0>

RD

DBDIR

tDBDL

8-Bit Mono DMA Read/Capture Cycle

SDIN

SDOUT

t

pd1

t

s1

t

h1

MSB, Left

SCLK

t

pd2

t

pd2

FSYNC

t

sckw

MSB, Left

t

pd2

FSYNC

SF1,0=01,10

SF1,0=00

Serial Port Timing

CS4231A

8DS139PP2

(high)

tDRHD

tDBDL

tDHD2

tWDSU

tDKSUb

tSTW

PDRQ

PDAK

D<7:0>

WR

DBDIR

tDKHDa

DBEN

8-Bit Mono DMA Write/Playback Cycle

RIGHT/HIGH

BYTE

LEFT/LOW

BYTE

tBWDN

D<7:0>

RD/ WR

CDRQ/PDRQ

CDAK/PDAK

8-Bit Stereo or 16-Bit Mono DMA Cycle

D<7:0>

LOW

BYTE

tBWDN

HIGH

BYTE

RD/

WR

CDRQ/

PDRQ

LEFT SAMPLE RIGHT SAMPLE

HIGH

BYTE

LOW

BYTE

CDAK/

PDAK

16-Bit Stereo or ADPCM DMA Cycle

CS4231A

DS139PP2 9

CDRQ/PDRQ

CDAK/PDAK

CS

DBEN

DBDIR

RD

D<7:0>

A<1:0>

tCSSU tCSHD

tDHD1

tRDDV

tADSU tADHD

tSUDK1 tSUDK2

tDBDL

tDBDL

I/O Read Cycle

CDRQ/PDRQ

CDAK/PDAK

CS

DBEN

DBDIR

WR

D<7:0>

A<1:0>

tCSSU tCSHD

tDHD2

tSUDK2

tADSU

tADHD

tWDSU

tSUDK1

tSTW

(high)

tDBDL

I/O Write Cycle

CS4231A

10 DS139PP2

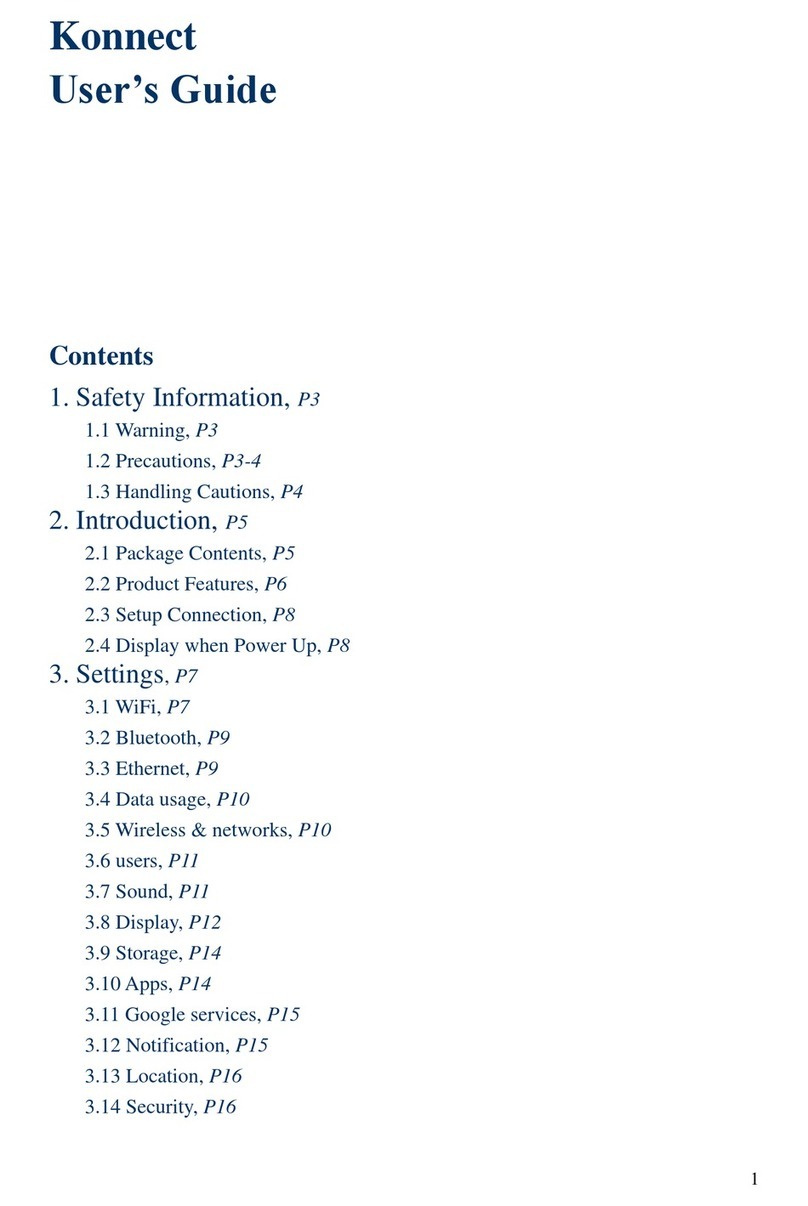

CS4231A

74F245

DIR

G

D

A

T

A

D

A

T

A

D7

D0

DBEN

DBDIR

PDRQ

CDRQ

IRQ

CDAK

PDAK

63

62

14

12

57

11

13

Board Digital

Ground

34 37

AGND1,2

ISA

BUS

D7

D0

DRQ<X>

DRQ<Y>

DAK<X>

IRQ<Z>

Auxilary

Inputs

39

0.33

µ

F

LAUX1

42

0.33

µ

F

RAUX1

38

0.33

µ

F

LAUX2

30

0.33

µ

F

Line

Inputs LLINE

27

0.33

µ

F

RLINE

21

XTAL2I

22

XTAL2O

17

XTAL1I

18

XTAL1O

24.576MHz

16.9344MHz

33 pF

33 pF

33 pF

33 pF

29

0.33

µ

F

Microphone

Inputs LMIC

28

0.33

µ

FRMIC

33

0.1

µ

F

10

µ

FVREFI

This trace

must be

very short

32

0.47

µ

F

VREF

43

0.33

µ

F

RAUX2

46

0.33

µ

F

MIN XCTL0

XCTL1

56

58

SAI

SAO

IOWC

IORC

A1

A0

WR

RD 60

61

9

10

CS 59

SA 19:2

AEN

Address

Decode

18

1

µ

F

LOUT

40

47k

Ω

1

µ

F

ROUT

41

47k

Ω

47

1

µ

FMOUT

Board Analog

Ground

26

31

RFILT

LFILT

1000 pF

NPO

1000 pF

NPO

+

VA1VA2

15 7

1

35

1

µ

F

+

+5V

Supply

Ferrite Bead

0.1

µ

F

0.1

µ

F

2.0

Ω

19

0.1

µ

F

36

0.1

µ

F

+5V Analog (preferred)

If a separate +5V analog

supply is available, attach here

and remove the 2.0

Ω

resistor

1

µ

F+

VD2

1

µ

F

+

0.1

µ

F

VD1VD3VD4

TEST

55

DGND1,2DGND3, 4, 7, 8

2816 20 53 64

PDWN 23

DAK<Y>

PLCC

Pinout

()

AB

88

SCLK

FSYNC

SDOUT

SDIN

51

50

52

49

DSP

or

ASIC

47k

Ω

VD3/4

(Optional)

Figure 1. Recommended Connection Diagram

(See Figures 16 & 17 for Layout Recommendations)

CS4231A

DS139PP2 11

GENERAL DESCRIPTION

The CS4231A is a monolithic integrated circuit

that provides audio in personal computers or

other parallel interface environments. The func-

tions include stereo Analog-to-Digital and

Digital-to-Analog converters (ADCs and DACs),

analog mixing, anti-aliasing and reconstruction

filters, line and microphone level inputs, optional

A-Law / µ-Law coding, simultaneous capture

and playback and a parallel bus interface. Five

analog inputs are provided and three can be mul-

tiplexed to the ADC. The line input, two

auxiliary inputs and a mono input can be mixed

with the output of the DAC with full volume

control. Several data modes are supported in-

cluding 8- and 16-bit linear as well as 8-bit

companded, 4-bit ADPCM compressed, and 16-

bit Big Endian. The CS4231A is packaged in a

68-pin PLCC or a 100-pin TQFP.

Enhanced Functions (MODE 2)

The CS4231A’s initial state is labeled MODE 1

and forces the CS4231A to appear as a CS4248.

Enhanced functionality is provided by a second

mode on the CS4231A. To switch from

MODE 1 to MODE 2, the MODE2 bit should be

set to one in the MODE and ID register (I12).

When MODE 2 is selected, the bit IA4 in the

Index Address register (R0) will be decoded as a

valid index pointer, providing 16 additional reg-

isters and increased functionality over the

CS4248.

To reverse the procedure, clear the MODE2 bit

and the CS4231A will resume operation in

MODE 1. Since previous code writes a zero to

bit IA4 of the Index Address register (R0), the

CS4231A is backwards compatible with the

CS4248 and the AD1848.

Mixer Attenuation Control on Line Input

The CS4231A adds mixer attenuation control for

the LINE inputs which are then summed into the

output mixer. This fourth input to the mixer

completes the recommended mixer configuration

for MPC Level-2 compliance. The LINE mix

register provides 32 volume adjustments in 1.5

dB steps. In addition, there is a one bit mute

control.

The additional MODE 2 functions are:

1. Full-Duplex DMA support

2. A programmable timer

3. Mono output with mute control

4. Mono input with mixer volume control

5. ADPCM and Big Endian audio data formats

6. Independent selection of capture and

playback audio data formats

7. Selectable serial audio data port.

ANALOG HARDWARE DESCRIPTION

The analog hardware consists of an MPC

Level 2-compatible mixer (four stereo mix

sources), three line-level stereo inputs, a stereo

microphone input, a mono input, a mono output,

and a stereo line output. This section describes

the analog hardware needed to interface with

these pins.

Analog Inputs

The analog inputs consist of four stereo analog

inputs, and one mono input. As shown on this

data sheet cover, the input to the ADCs comes

from a multiplexer that selects between two ana-

log line-level inputs (LINE, AUX1), a

microphone level input (MIC), and the output

from the MPC-compatible mixer. The LINE and

AUX1 lines also feed the MPC mixer and in-

clude individual volume controls. Unused analog

inputs should be connected together and then

connected through a capacitor to analog ground.

CS4231A

12 DS139PP2

Line-Level Inputs plus MPC Mixer

The analog input interface is designed to accom-

modate four stereo inputs and one mono input.

Three of these sources are multiplexed to the

ADC. These inputs are: a stereo line-level input

(LINE), a stereo microphone input (MIC), and a

stereo auxiliary line-level input (AUX1). The

LINE and AUX1 inputs have a separate path,

with volume control, to the output analog mixer

which has the additional inputs of a stereo

AUX2 channel, a mono input channel, and the

output of the DACs. All audio inputs should be

capacitively coupled to the CS4231A.

Since some analog inputs can be as large as

2 VRMS, the circuit shown in Figure 2 can be

used to attenuate the analog input to 1 VRMS

which is the maximum voltage allowed for the

line-level inputs on the CS4231A.

Microphone Level Inputs

The microphone level inputs, LMIC and RMIC,

include a selectable + 20dB gain stage for inter-

facing to an external microphone. The 20 dB

gain block can be turned off to provide another

stereo line-level input. Figure 3 illustrates a sin-

gle-ended microphone input buffer with +18 dB

of gain that will support lower gain mics, and

should be placed as close to the input jack as

possible to minimize noise coupling.

Mono Input with Attenuation and Mute

The mono input, MIN, is useful for mixing the

output of the "beeper" (timer chip), provided in

all PCs, with the rest of the audio signals. The

attenuation control allows 16 levels in -3dB

steps. In addition, a mute control is provided.

The attenuator is a single channel block with the

resulting signal sent to the output mixer where it

is mixed with the left and right outputs. Figure 4

illustrates a typical input circuit for the Mono In.

Although this input is described for a low-qual-

ity beeper, the input is of the same high-quality

as all other analog inputs and may be used for

other purposes. At power-up, the MIN line is un-

muted (as is the mono out line) allowing the

initial beeps heard, when the computer is initial-

izing, to pass through.

Analog Outputs

The analog output section of the CS4231A pro-

vides a stereo line-level output. The other output

types (headphone and speaker) can be imple-

mented with external circuitry. LOUT and

ROUT outputs should be capacitively coupled to

external circuitry.

5.6 k

Ω

5.6 k

Ω

0.33

µ

F

0.33

µ

FR

L

5.6 k

Ω

5.6 k

Ω

Figure 2. Line Inputs

1

µ

F

+

560 pF

NPO

10

µ

F+

1.5 k

Ω

11 k

Ω

47 k

Ω

MC33078 or

MC33178

0.33

µ

F

VREF

LMIC

10

µ

F

+32

29

Figure 3. Left or Mono Microphone Input

2.7 nF

47 k

Ω

4.7 k

Ω

0.1

µ

F46 MIN

1

+5VA

(Low Noise)

Figure 4. Mono Input

CS4231A

DS139PP2 13

Mono Output with Mute Control

The mono output, MOUT, is a sum of the left

and right output channels, attenuated by 6dB to

prevent clipping at full scale. The mono out

channel can be used to drive the PC-internal

mono speaker using an appropriate drive circuit.

This approach allows the traditional PC-sounds

to be integrated with the rest of the audio sys-

tem. Figure 5 illustrates a typical speaker driver

circuit. The mute control is independent of the

line outputs allowing the mono channel to mute

the speaker without muting the line outputs. The

power-up default has MIN and MOUT enabled

to provide a pass-through for the beeps heard at

power-up.

Miscellaneous Analog Signals

The LFILT and RFILT pins must have a 1000 pF

NPO capacitor to analog ground. These capaci-

tors, along with an internal resistor, provide a

single-pole low-pass filter used at the inputs to

the ADCs. By placing these filters at the ADC

inputs, low-pass filters at each analog input pin

are avoided.

The VREFI pin is used to lower the noise of the

internal voltage reference. A 10µF and 0.1µF ca-

pacitor to analog ground should be connected

with a short wide trace to this pin. No other con-

nection should be made, since noise coupling

onto this pin can degrade the analog perform-

ance of the codec. Likewise, digital signals

should be kept away from VREFI for similar

reasons.

The VREF pin is typically 2.1 V and provides a

common mode signal for single-supply external

circuits. VREF only supports DC loads and

should be buffered if AC loading is needed. For

typical use, a 0.47 µF capacitor should be con-

nected to VREF. The signal-to-noise ratio of the

microphone inputs can be improved by increas-

ing the capacitance on VREF to 10 µF.

DIGITAL HARDWARE DESCRIPTION

The digital hardware consist of the data bus, ad-

dress bus, and control signals needed for the

parallel bus, as well as an interrupt and DMA

signals.

Parallel Data Interface

The 8-bit parallel port of the CS4231A provides

an interface which is compatible with most com-

puter peripheral busses. This parallel interface is

designed to operate on the Industry Standard Ar-

chitecture (ISA) bus, but the CS4231A will

easily interface with other buses such as EISA

and Microchannel. Two types of accesses can

occur via the parallel interface: Programmed I/O

(PIO) access, and DMA access.

There is no provision for the CS4231A to "hold

off" or extend a cycle occurring on the parallel

interface. Therefore, the internal architecture of

the CS4231A accepts asynchronous parallel bus

cycles without interfering with the flow of data

to or from the ADC and DAC sections.

FIFOs

The CS4231A contains 16-sample FIFOs in both

the playback and capture paths. The FIFOs are

0.1

µ

F

1

µ

F+

47

Ω

0.1

µ

F

47

Ω

+

1

µ

F12 7

38

5

6

416 k

Ω

470 pF

0.1

µ

F

Ferrite Bead

10 k

Ω

0.22

µ

F

47

MOUT

+5V

RESDRV

MC34119

Figure 5. Mono Output

CS4231A

14 DS139PP2

transparent and have no programming associated

with them.

When playback is enabled, the playback FIFO

continually requests data until the FIFO is full,

and then makes requests as positions inside the

FIFO are emptied, thereby keeping the playback

FIFO as full as possible. Thus when the system

cannot respond within a sample period, the FIFO

is emptied, avoiding a momentary loss of audio

data. If the FIFO runs out of data, the last valid

sample can be continuously output to the DACs

(if DACZ in I16 is set) which will eliminate

pops from occurring.

When capture is enabled, the capture FIFO tries

to continually stay empty by making requests

every sample period. Thus when the system can-

not respond within a sample period, the capture

FIFO starts filling thereby avoiding a loss of

data in the audio data stream.

High Current Data Bus Drivers

The CS4231A provides 16 mA drivers eliminat-

ing the need for off chip drivers in many cases.

If a full 24 mA drive is required, the appropriate

direction and driver select lines are provided.

The current drivers are provided for the data bus,

DMA request line, and the interrupt request line.

PIO Registers Interface

The first type of parallel bus access is pro-

grammed I/O (PIO) to the four control registers.

The control registers allow access to status,

audio data, and all indirect registers via the in-

dex registers. The RD and WR signals are used

to define the read and write cycles respectively.

The PIO register cycle is defined by the asser-

tion of the CS4231A CS signal while the DMA

acknowledge signals, CDAK and PDAK, are in-

active. For read cycles, the CS4231A will drive

data on the DATA lines while the host asserts the

RD strobe. Write cycles require the host to assert

data on the DATA lines and strobe the WR sig-

nal. The CS4231A will latch data into the PIO

register on the rising edge of the WR strobe. The

CS4231A CS signal should remain active until

after completion of the read or write cycle. I/O

cycles are the only type of cycle which can ac-

cess the internal control and status registers.

When reading or writing audio data via PIO, the

Status register (R2) indicates which byte of the

audio sample is ready. The Status register does

not have to be read after every byte; however,

once all bytes of a sample are transferred, the

Status register must be read before the next sam-

ple can be transferred.

The audio data interface typically uses DMA re-

quest/grant pins to transfer the digital audio data

between the CS4231A and the bus. The

CS4231A is responsible for asserting a request

signal whenever the CS4231A’s internal buffers

need updating. The logic interfaced with the

CS4231A responds with an acknowledge signal

and strobes data to and from the CS4231A, 8

bits at a time. The CS4231A keeps the request

pin active until the appropriate number of 8-bit

cycles have occurred to transfer one audio sam-

ple. Notice that different audio data types will

require a different number of 8-bit transfers.

DMA Interface

The second type of parallel bus cycle on the

CS4231A is a DMA transfer. DMA cycles are

distinguished from PIO register cycles by the as-

sertion by the CS4231A of a CDRQ (or PDRQ)

followed by an acknowledgment by the host by

the assertion of CDAK (or PDAK). While the

acknowledgment is received from the host, the

CS4231A assumes that any cycles occurring are

DMA cycles and ignores the addresses on the

address lines and the CS line.

The CS4231A may assert the DMA request sig-

nal at any time. Once asserted, the DMA request

will remain asserted until a DMA cycle occurs to

the CS4231A. Once the falling edge of the final

CS4231A

DS139PP2 15

WR or RD strobe of a full sample of a DMA

cycle occurs, the DMA request signal is negated

immediately. DMA transfers may be terminated

by resetting the PEN and/or CEN bits in the In-

terface Configuration register (I9), depending on

the DMA that is in progress (playback, capture,

or both). Termination of DMA transfers may

only happen between sample transfers on the

bus. If PDRQ and/or CDRQ goes active while

resetting PEN and/or CEN, the request must be

acknowledged (PDAK and/or CDAK) and a fi-

nal sample transfer completed. The CS4231A

supports up to two DMA channels.

Dual DMA Channel Mode

In dual DMA channel mode, playback and cap-

ture DMA requests and acknowledges occur on

independent DMA channels. In this mode, cap-

ture and playback are enabled and set for DMA

transfers. In addition, the dual DMA mode must

be set (SDC = 0). The Playback- and Capture-

Enables (PEN, CEN, I9) can be changed without

a Mode Change Enable (MCE, R0). This allows

for proper full duplex control where applications

are independently using playback and capture.

Single DMA Channel (SDC) Mode

When two DMA channels are not available, the

SDC mode forces all DMA transfers (capture or

playback) to occur on a single DMA channel

(playback channel). The trade-off is that the

CS4231A will no longer be able to perform si-

multaneous DMA capture and playback.

To enable the SDC mode, set the SDC bit in the

Interface Configuration register (I9). With the

SDC bit asserted, the internal workings of the

CS4231A remain exactly the same as dual mode,

except for the manner in which DMA request

and acknowledges are handled.

The playback of audio data will occur on the

playback channel exactly as dual channel opera-

tion. However, the capture audio channel is now

diverted to the playback channel. This means

that the capture DMA request occurs on the

PDRQ pin and the PDAK pin is used to acknow-

ledge the capture request. (In MODE 2, the

capture data format is always set in register I28.)

Note, simultaneous capture and playback cannot

occur in SDC mode. If both playback and cap-

ture are enabled, the default will be playback.

In SDC mode, the CDRQ pin is logic low (inac-

tive). The CDAK pin is ignored by the

CS4231A. SDC does not have any affect when

using PIO accesses.

Serial Audio Data Port

The bits controlling the serial port can only be

changed when the Mode Change Enable bit,

MCE, in R0 is high. The audio serial port is

software selectable via the SPE bit in I16. Once

enabled, the data from the ADCs is sent to the

SDOUT pin and the audio data input on the

SDIN pin is routed to the DACs. The parallel

bus on the CS4231A is still used for control in-

formation such as volume and audio data

formats. While the serial port is enabled, audio

data can still be read from the codec ADCs (cap-

ture) on the parallel port, but the DACs

(playback) only accept data from the serial port

in pin. When the serial port is disabled

(SPE = 0); FSYNC, SCLK, and SDOUT are

held low.

FSYNC and SCLK are always output from the

CS4231A. The serial port can be configured in

one of three serial port formats, shown in Fig-

ures 6-8. SF1 and SF0 in I16 select the particular

format. Both left and right audio words are al-

ways 16 bits wide with the actual audio data left

justified in the word (i.e. ADPCM occupies the

first four bits). Unused bits are output as zeros

after the LSB. The justification is illustrated in

Figure 9. When the mono audio format is se-

lected, the right channel output is set to zero and

the left channel input is sent to both DAC chan-

nels. When changing sample frequencies the

CS4231A

16 DS139PP2

output clocks will stretch, but will not have any

glitches. This allows the serial port to operate

through a sample frequency change.

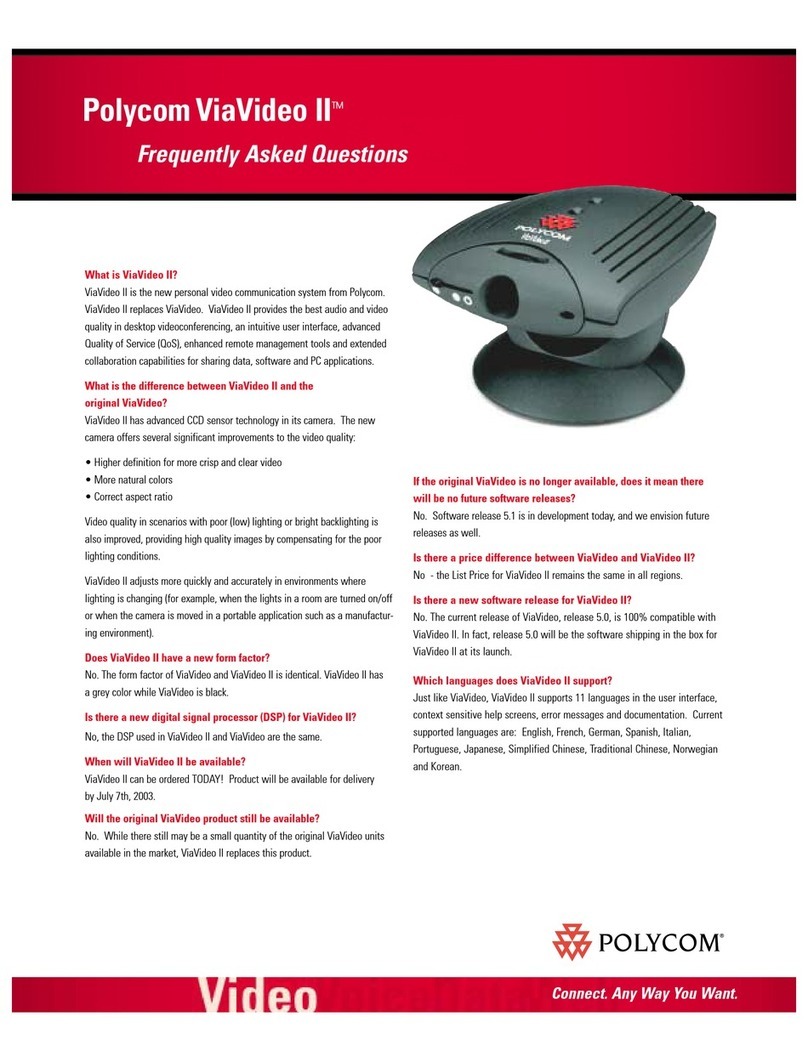

The first format - SPF0, shown in Figure 6, is

called 64-bit enhanced. This format has 64

SCLKs per frame with a one bit period wide

FSYNC that precedes the frame. The first 16 bits

FSYNC

SCLK

SDOUT

15 14 13 12

...

16 Bits

Left Data

015 14

...

0

16 Bits

Right Data

8 zeros

SDIN

15 14 13 12

...

16 Bits

Left Data

015 14

...

0

16 Bits

Right Data INT = Interrupt Bit

CEN = Capture Enable

PEN = Playback Enable

OVR = Left Overrange or

Right Overrange

INT

7 zeros

CEN PEN OVR

13 zeros

32 Bits

...

Figure 6. 64-bit enhanced mode (SF1,0 = 00)

FSYNC

Left Data

SCLK

SDOUT/

15 14 13 0

...

15 14 13 0

...

15

Right Data

16 Clocks 16 Clocks 16 Clocks 16 Clocks

SDIN

Figure 7. 64-bit mode (SF1,0 = 01)

SCLK

FSYNC

Left Data

SDOUT/

15 14 13 0

...

16 Clocks

15 14 13 0

...

16 Clocks

15

Right Data

32 No-Clock bit periods

...

Left Data

14

...

...

SDIN

Figure 8. 32-bit mode (SF1,0 = 10)

CS4231A

DS139PP2 17

is the left word and the second 16 bits is the

right word. The last 32 bits contains four status

bits and 28 zeros. This is the only mode that

contains status information.

The second serial format - SPF1, shown in Fig-

ure 7, is called 64-bit mode. This format also has

64 SCLKs per frame, but has FSYNC transition-

ing high at the start of the left data word and

transitioning low at the start of the right data

word. Both the left and the right data word are

followed by 16 zeros.

The third serial format - SPF2, shown in Fig-

ure 7, is called 32-bit mode. This format

contains 32 SCLKs per frame wherein FSYNC

is high for the left channel and low for the right

channel. The absolute time is similar to the other

two modes but SCLK is stopped after the right

channel is finished until the start of the next

frame (stopped for 32 bit period times). This

mode is useful for DSPs that do not want the

interrupt overhead of the 32 unused bit periods.

As an example, if a DSP serial word length is 16

bits, then four interrupts will occur in SPF0 and

SPF1; whereas in SPF2 the DSP will only get

two interrupts.

Miscellaneous Signals

The power supply providing analog power

should be as clean as possible to minimize noise

coupling into the analog section and degrading

analog performance. The VD1 and VD2 pins are

isolated from the rest of the digital power pins

and provide digital power for the asynchronous

parallel bus. These two pins can be connected

directly to the digital power supply. VD3 and

VD4 digital power supply pins provide power to

the internal digital section of the codec and

should be optimally quieter than VD1 and VD2.

This can be achieved by using a ferrite bead as

shown in the typical connection diagram in Fig-

ure 1. Grounding is covered in the Grounding

and Layout section.

An interrupt pin, IRQ, is provided to allow for

host notification by the CS4231A. Since the in-

terrupt is mainly a software function, it is

described in more detail under the software sec-

tion.

Crystals / Clocks

Four pins have been allocated to allow the inter-

facing of two crystal oscillators to the CS4231A:

XTAL1I, XTAL1O, XTAL2I, XTAL2O. The

crystals should be designed as fundamental

mode, parallel resonant, with a load capacitor of

between 10 and 20 pF. The capacitors shown in

Figure 1, connected to each of the crystal pins,

should be twice the load capacitance specified to

the crystal manufacturer. The XTAL1 oscillator

is designed with slightly more gain to handle

0

LSB

123456789

10

1112

13

1415

MSB

LSBMSB

LSBMSB

X: SDIN - Don’t care, SDOUT - 0

Audio Word

Bits

16

8

4

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

XXXXX

Figure 9. Serial Audio Data Justification

CS4231A

18 DS139PP2

higher frequencies, but any crystal with the

above specifications should suffice. The standard

crystals for audio are:

XTAL1: 24.576 MHz

Fundamental Mode

Parallel Resonant, CL= 20 pF

XTAL2: 16.9344 MHz

Fundamental Mode

Parallel Resonant, CL= 20 pF

These crystal frequencies support the standard

sample frequencies listed in Table 7.

External CMOS clocks may be connected the

crystal inputs (XTAL1I, XTAL2I) in lieu of the

crystals. When using external CMOS clocks, the

XTAL out pins should be left floating. Extreme

care should be used when laying out a board us-

ing external clocks since coupling between

clocks can degrade analog performance.

Power Down - PDWN

The PDWN signal places the CS4231A into

maximum power conservation mode. When

PDWN goes low, any reads of the codec’s paral-

lel interface return 80 hex, all analog outputs are

muted, and the voltage reference then slowly de-

cays to ground. When PDWN is brought high, a

full calibration cycle automatically occurs. While

the codec is initializing, any reads from the par-

allel interface will return 80 hex and writes will

be ignored. When initialization is completed, the

registers will contain their reset value as stated

in the register section of the data sheet. The

CS4231A contains an internal "Power On Reset"

signal that causes a proper initialization at power

up time. Therefore, if no power down mode is

needed, PDWN can be tied permanently to

VD3/4.

DBEN/DBDIR

If needed, the DBEN and DBDIR pins can con-

trol an external data buffer to the CS4231A. The

CS4231A contains 16 mA bus drivers so the ex-

ternal data buffer is only needed when driving a

full 24 mA bus. DBEN enables the external driv-

ers and DBDIR controls the direction of the data

flow. Both signals are normally high, where

DBDIR high points the transceiver towards the

codec and low points the transceiver towards the

data bus. See Figure 1 for a typical connection

diagram.

SOFTWARE DESCRIPTION

The CS4231A must be in Mode Change Enable

Mode (MCE=1) before any changes to the Inter-

face Configuration register (I9), the Sample

Frequency (lower four bits) in the Fs & Playback

Data Format register (I8), or the serial port bits

(SF1, SF0, SPE) in the Alternate Feature Enable

I register (I16) are allowed. The actual audio

data formats, which are the upper four bits of I8

for playback and I28 for capture, can be changed

by setting MCE (R0) or PMCE/CMCE (I16)

high. The exceptions are CEN and PEN which

can be changed "on-the-fly" via programmed I/O

writes to these bits. All outstanding DMA trans-

fers must be completed before new values of

CEN or PEN are recognized.

Power-Down and Initialization

To put the CS4231A into a power-down mode,

the PDWN pin is pulled low. In this state the

host interface reads 80h indicating that it is un-

able to respond and all analog circuits are turned

off.

To let the CS4231A go through its reset initiali-

zation the PDWN pin should be set high. This

CS4231A

DS139PP2 19

rising edge starts the initialization process in

which a full calibration occurs. While the

CS4231A is initializing, 80 hex is returned from

all reads by the host computer. All writes during

initialization of the CS4231A will be ignored.

At the end of the initialization, all registers are

set to known reset values as documented in the

register definition section.

Calibration Modes

The CS4231A has four different calibration

modes. The selected calibration occurs whenever

the Mode Change Enable (MCE, R0) bit goes

from 1 to 0.

The completion of calibration can be determined

by polling the Auto-Calibrate In-Progress bit in

the Error Status and Initialization register (ACI,

I11). This bit will be high while the calibration is

in progress and low once completed. The cali-

bration time varies with calibration mode.

The Calibration procedure is as follows:

1) Place the CS4231A in Mode Change En-

able using the MCE bit of the Index

Address register (R0).

2) Set the CAL1,0 bits in the Interface Con-

figuration register (I9).

3) Return from Mode Change Enable by reset-

ting the MCE bit of the Index Address

register (R0).

4) Wait until ACI (I11) cleared to proceed

No Calibration (CAL1,0 = 00)

This is the fastest mode since no calibration is

performed. This mode is useful for games which

need to change the sample frequency quickly.

This mode is also useful when the codec is oper-

ating in full-duplex and an ADC data format

change is desired. This is the only calibration

mode that does not affect the DACs (i.e. mute

the DACs at some point). Changing from any

other calibration mode to No Calibration mode

will take 40 sample periods to complete; how-

ever, subsequent MCE cycles will take 0 sample

periods.

Converter Calibration (CAL1,0 = 01)

This calibration mode calibrates the ADCs and

DACs but does not calibrate any of the analog

mixing channels. This is the second longest cali-

bration mode, taking 136 sample periods, and is

software and hardware similar to the CS4231 or

CS4248. Since the mixer is not calibrated, any

analog signals mixing into the output will be un-

affected. The calibration sequence done by the

CS4231A is as follows:

The DACs are muted

The ADCs are calibrated

The DACs are calibrated

The DACs are unmuted

DAC Calibration (CAL1,0 = 10)

This calibration mode only calibrates the DACs’

(playback) interpolation filters leaving the ADCs

unaffected. This is the second fastest calibration

mode (no cal. is the fastest) taking 40 sample pe-

riods to complete. The calibration sequence done

by the CS4231A is as follows:

The DACs are muted

The DAC filters are calibrated

The DACs are unmuted

Full Calibration (CAL1,0 = 11)

This calibration mode calibrates all offsets,

ADCs, DACs, and analog mixers. Full calibra-

tion is automatically initiated on power up or

anytime the CS4231A exits from a power down

state. This is the longest calibration mode and

takes 168 sample periods to complete. The cali-

bration sequence done by the CS4231A is as

follows:

CS4231A

20 DS139PP2

This manual suits for next models

2

Table of contents