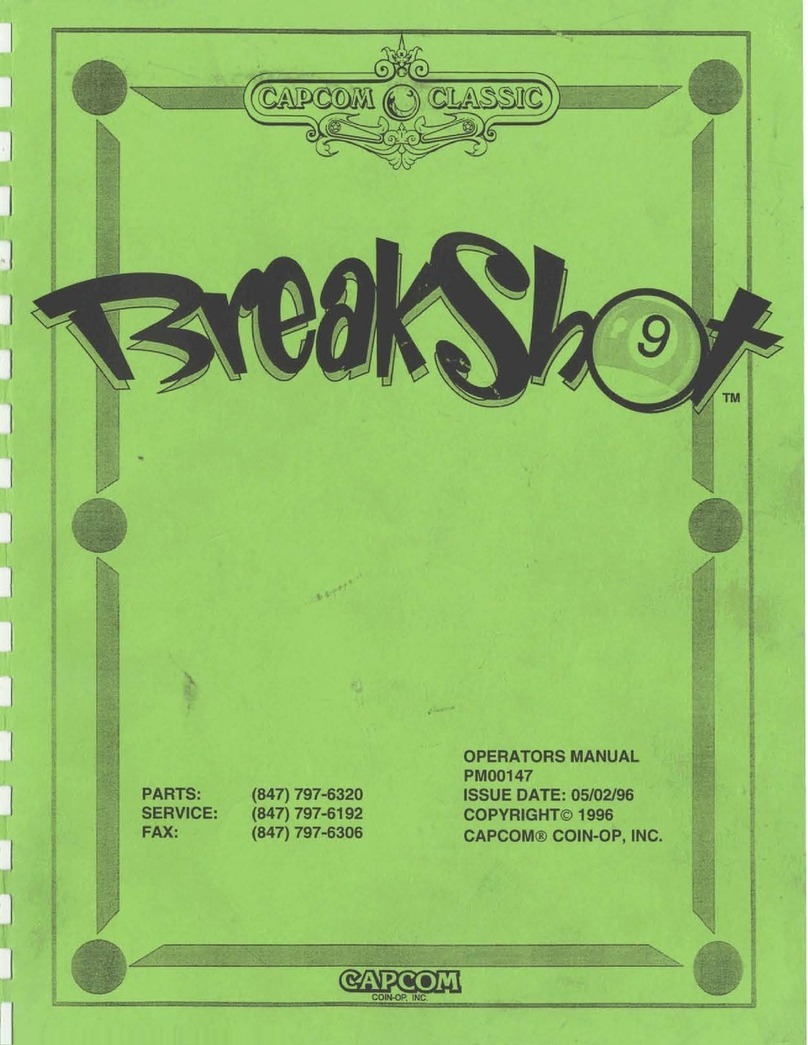

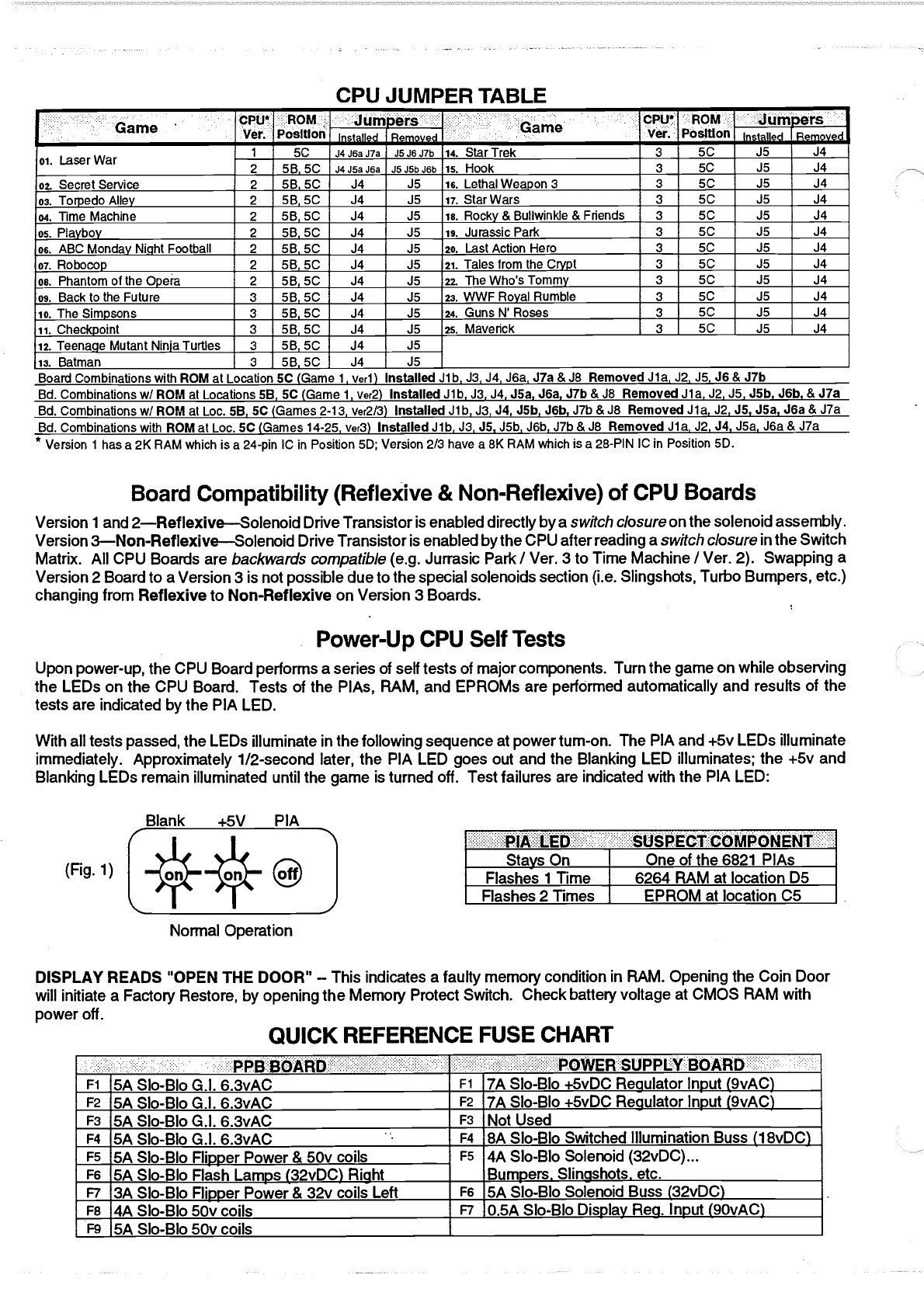

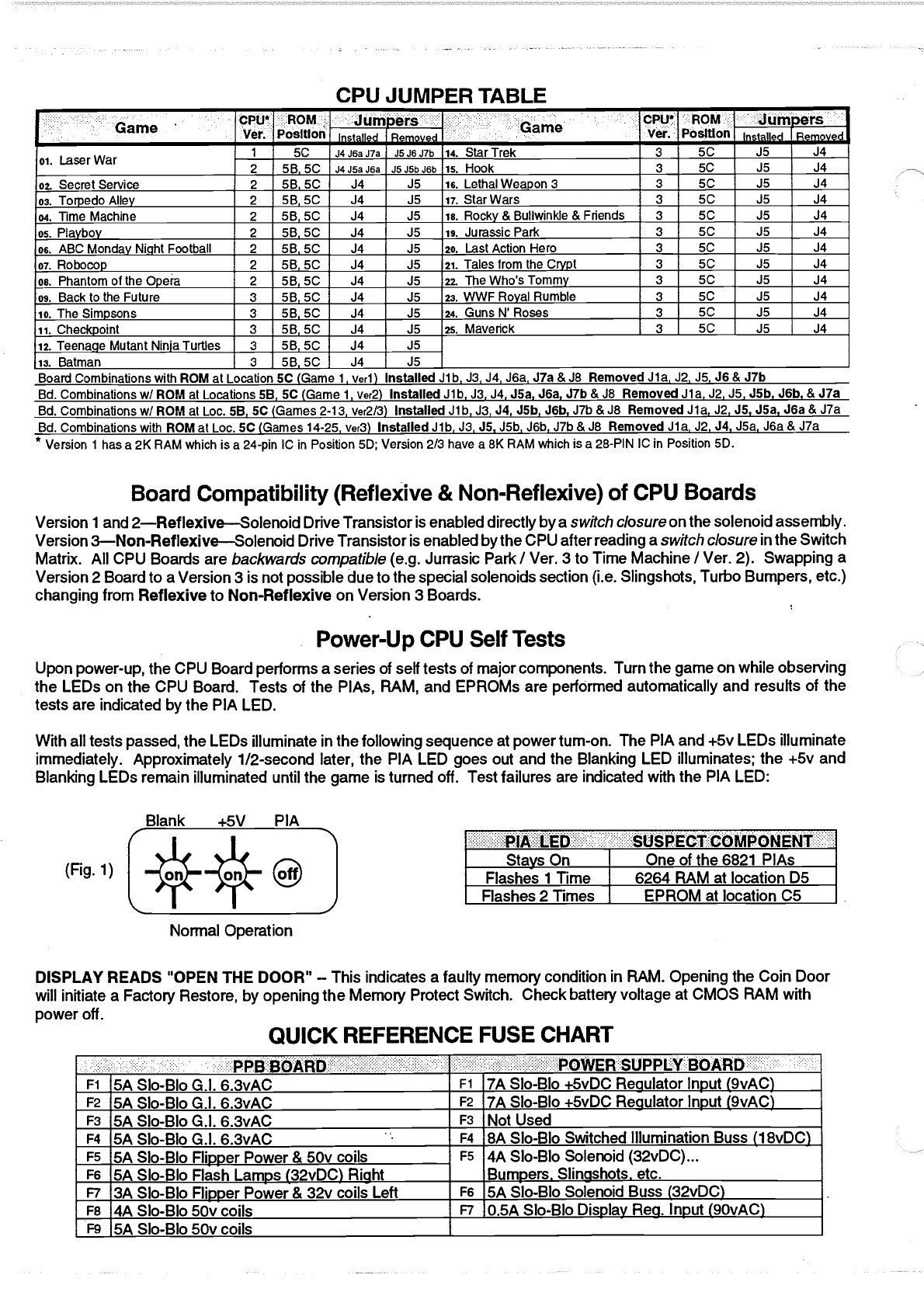

Cpu JUMPER TABLE

.: .:.:.:..:. G cpU:.'RoM: :jÜth,è s .

: :ROM _IJüers

. .. ame Position Instatled Removed _ :

Game . PoSlilon Installed Removed

01 LaserWar -i--- 5C J4J6aJ7a J5J6J7b 14. StrTrek 3 5C J5 J4

. _2__ 5B, 5C J4J5aJ6a J5J5bJ6b 15. Hook 3 5C J5 J4

fl2. Secret Service 2 5B, 5C J4 J5 16. Lethal Weapon 3 3 5C J5 J4

03. Torpedo Alley _î_ 5B, 5C J4 J5 17. StarWars 3 50 J5 J4

04. lime Machine 2 5B, 5C J4 J5 is. Rocky & Buliwinkle & Friends 3 5C J5 J4

05. Playboy _2__ 5B, 5C J4 J5 19. Jurassic Parl 3 5C J5 J4

06. ABC Monday Night Football 2 5B, 5C J4 J5 20. Lest Action Hero 3 5C J5 J4

07. Robocop _a_ 5B, 5C J4 J5 21. Tales from the Crypt 5C J5 J4

08. Phantom of the Opera 2 5B, 5C J4 J5 . The Whos Tommy 3 5C J5 J4

09. Back to the Future 3 5B, 5C J4 J5 23. WWF Royal Rumble 3 5C J5 J4

lo. The Simpsons 3 5B, 5C J4 J5 . Guns N' Roses 3 5C J5 J4

11. Checkpoint 3 5B, 5C J4 J5 s. Maverick 3 5C J5 J4

12. Teenape Mutant Ninja Turtles 3 5B, 5C J4 J5

13. Batman _a_ 5B, 5C J4 J5

Board Combinaons with ROM at Location 5C (Game i Verl) installed Jib, J3, J4, J6a, J7a & J8 Removed Jla, J2, J5, J6 & J7b

Bd. Combinations w/ ROM at Locations 5B, 5C (Game i , Ver2) installed Jib, J3, J4, J5a, J6a, J7b & J8 Removed Jia, J2, J5, J5b, J6b, & J7a

Bd. Combinations w/ ROM at Loc. 5B, 5C (Games 2-13, Ver2/3) Installed Jib, J3, J4, J5b, J6b, J7b & J8 Removed Jia, J2, J5, J5a, J6a & J7a

Bd. Combinations with ROM at Loc. 5C (Games 14-25, Ver3) Installed Jib, J3, J5, J5b, J6b, J7b & J8 Removed Jia, J2, J4, J5a, J6a & J7a

* Version i has a 2K RAM which is a 24-pin IC in Position 5D; Version 2/3 have a 8k RAM which is a 28-PIN IC in Position 5D.

Board Compatibility (Reflexive & Non-Reflexive) of CPU Boards

Version 1 and 2-Reflexive--Solenoid DriveTransistor is enabled directly bya switch closureon the solenoid assembly.

Version 3-Non-Reflexive-SolenoidDrive Transistoris enabled by the CPU after reading a switch closure in the Switch

Matrix. All CPU Boards are backwards compatible (e.g. Jurrasic Park I Vor. 3 to Time Machine I Ver. 2). Swapping a

Version 2 Board to a Version 3 is not possible dueto thespecial solenoids section (i.e. Slingshots, Turbo Bumpers, etc.)

changing from Reflexive to Non-Reflexive on Version 3 Boards.

Power-Up CPU Self Tests

Upon power-up, the CPU Board performs a series of selftests of major components. Turn the game on while observing

the LEDs on the CPU Board. Tests of the PIAs, RAM, and EPROMs are performed automatically and results of the

tests are indicated bythe PIA LED.

With all tests passed, the LEDs illuminate in the following sequence at powertum-on. The PIA and +5v LEDs illuminate

immediately. Approximately 1/2-second later, the PIA LED goes out and the Blanking LED illuminates; the +5v and

Blanking LEDs remain illuminated until the game is turned off. Test failures are indicated with the PIA LED:

Blank .4-5V PIA

(Fig.1) [:**@

Normal Operation

Stays On One of the6821 PIAs

Flashes i Time 6264 RAM at location D5

Flashes 2 Times EPROM at location C5

DISPLAY READS "OPEN THE DOOR" -This indicates a faulty memory condition in RAM. Opening the Coin Door

will initiate a Factory Restore, by opening the Memory Protect Switch. Check battery voltage at CMOS RAM with

power off. QUICK REFERENCE FUSE CHART

- PPB BOARD POWER SUPPLY BOARD

5A Slo-Blo G.I. 6.3vAC ..fl. 7A Slo-Blo +5vDC Regulator Input (9vAC)

!? 5A Slo-Blo G.l. 6.3vAC ..f& 7A Slo-Blo +5vDC Regulator Input (9vAC)

-- 5A Slo-Blo G.l. 6.3vAC í Not Used

_i 5A Slo-Blo G.l. 6.3vAC . . ii8A Slo-Blo Switched Illumination Buss (1 8vDC)

5A SIo-Blo Flipper Power & 50v coils F5 4A Slo-Blo Solenoid (32vDC)...

_E 5A Slo-Blo Flash Lamps (32vDC) Right Bumpers. Slingshots. etc.

..EZ 3A Slo-Blo Flipper Power & 32v coils Left 5A Slo-Blo Solenoid Buss (32vDC)

-. 4A Slo-Blo 50v coils O.5A Slo-Blo Display Reg. Input (9OvAC)

5A Slo-Blo 50v coils _________________________________________

PDF compression, OCR, web optimization using a watermarked evaluation copy of CVISION PDFCompressor