TABLE OF CONTENTS

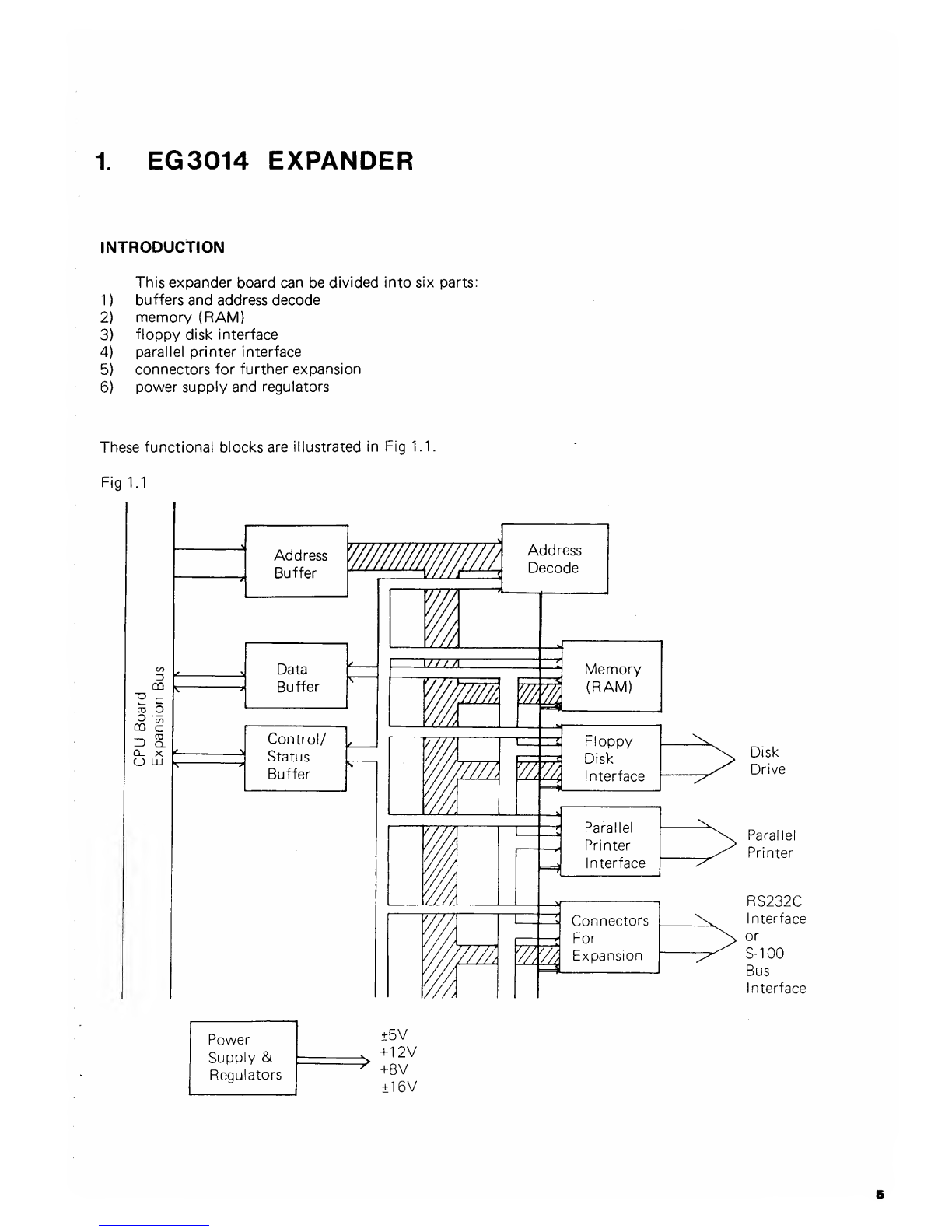

1. EG3014 EXPANDER PAGE

1.1 Buffers and Address Decode Logic __ _ ______.6

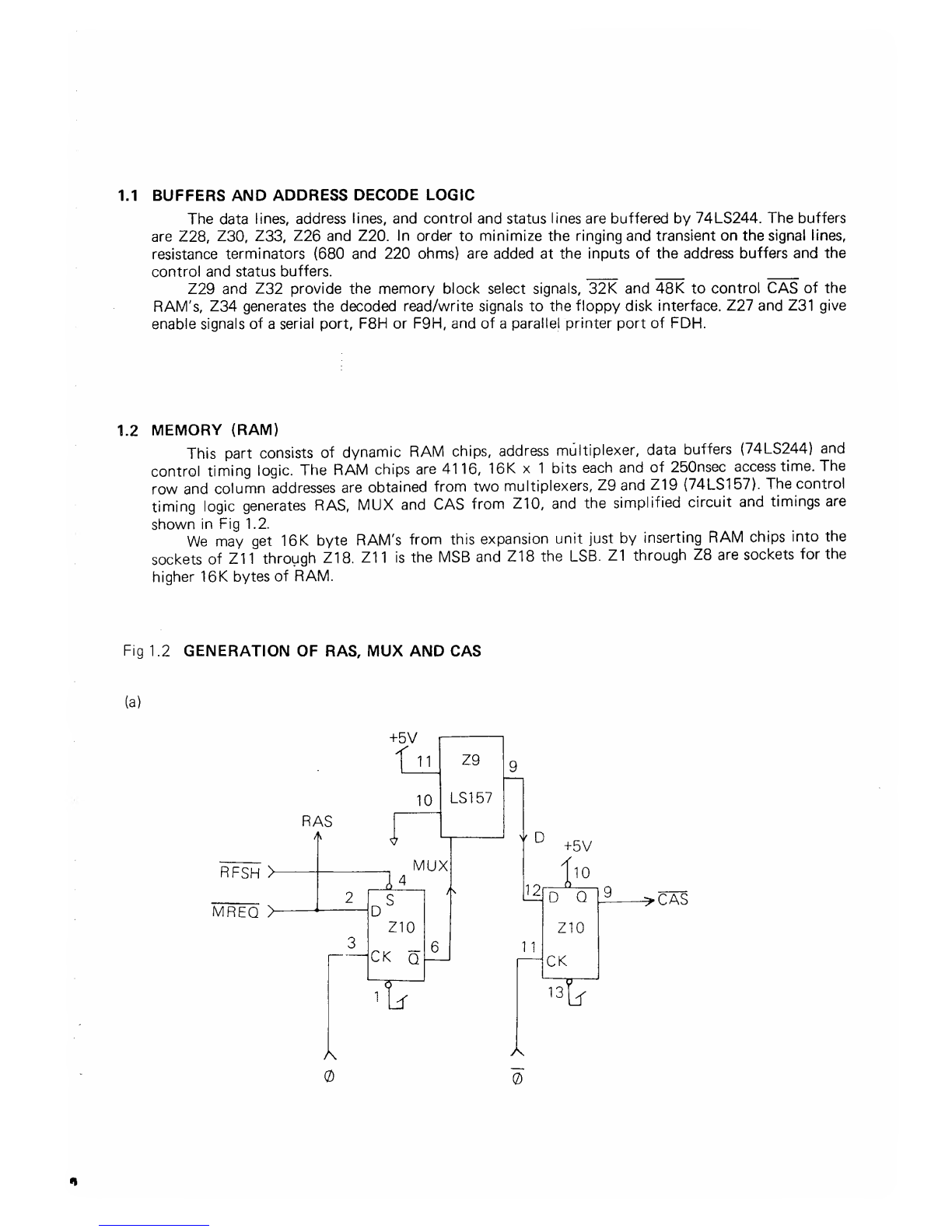

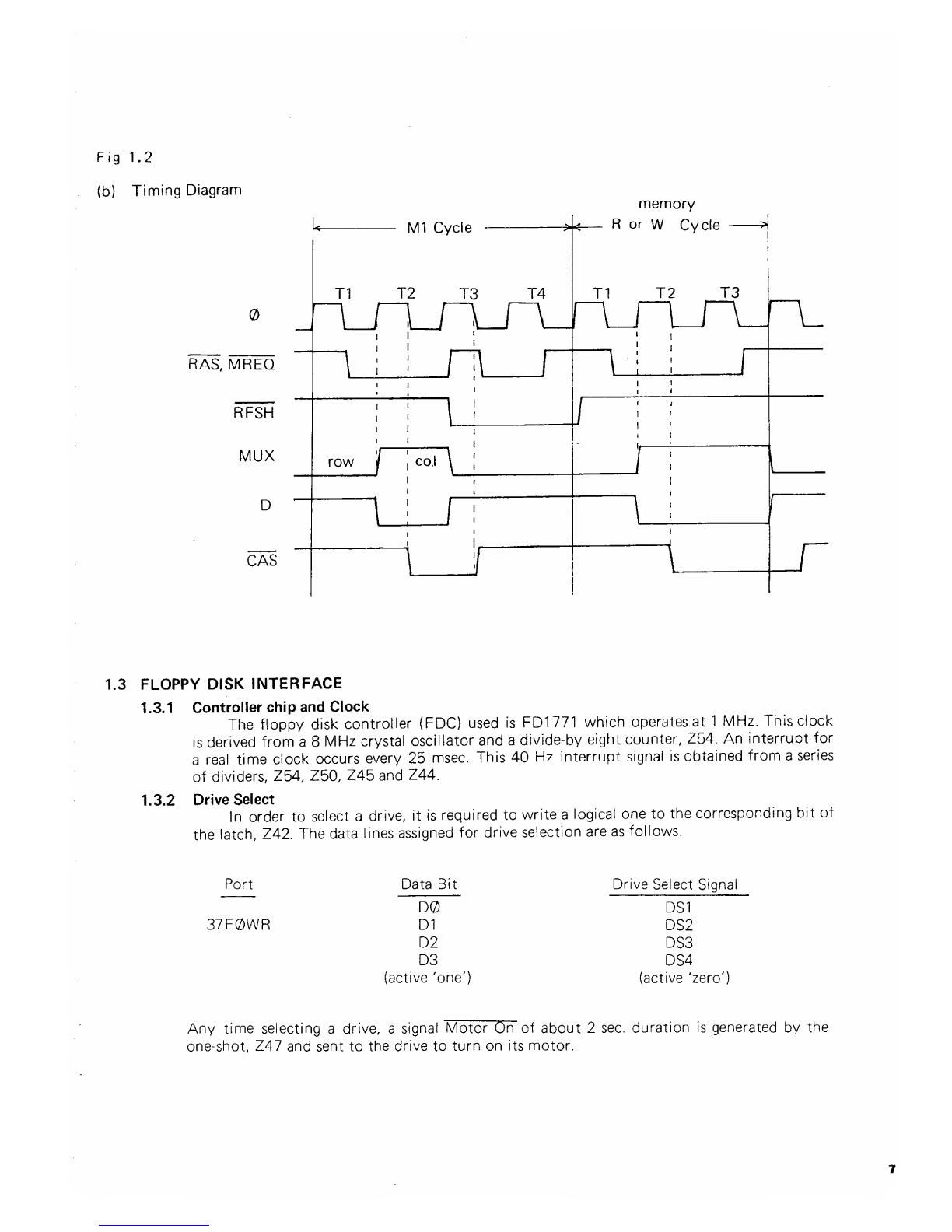

1.2 Memory (RAM) _____.____..____. 6

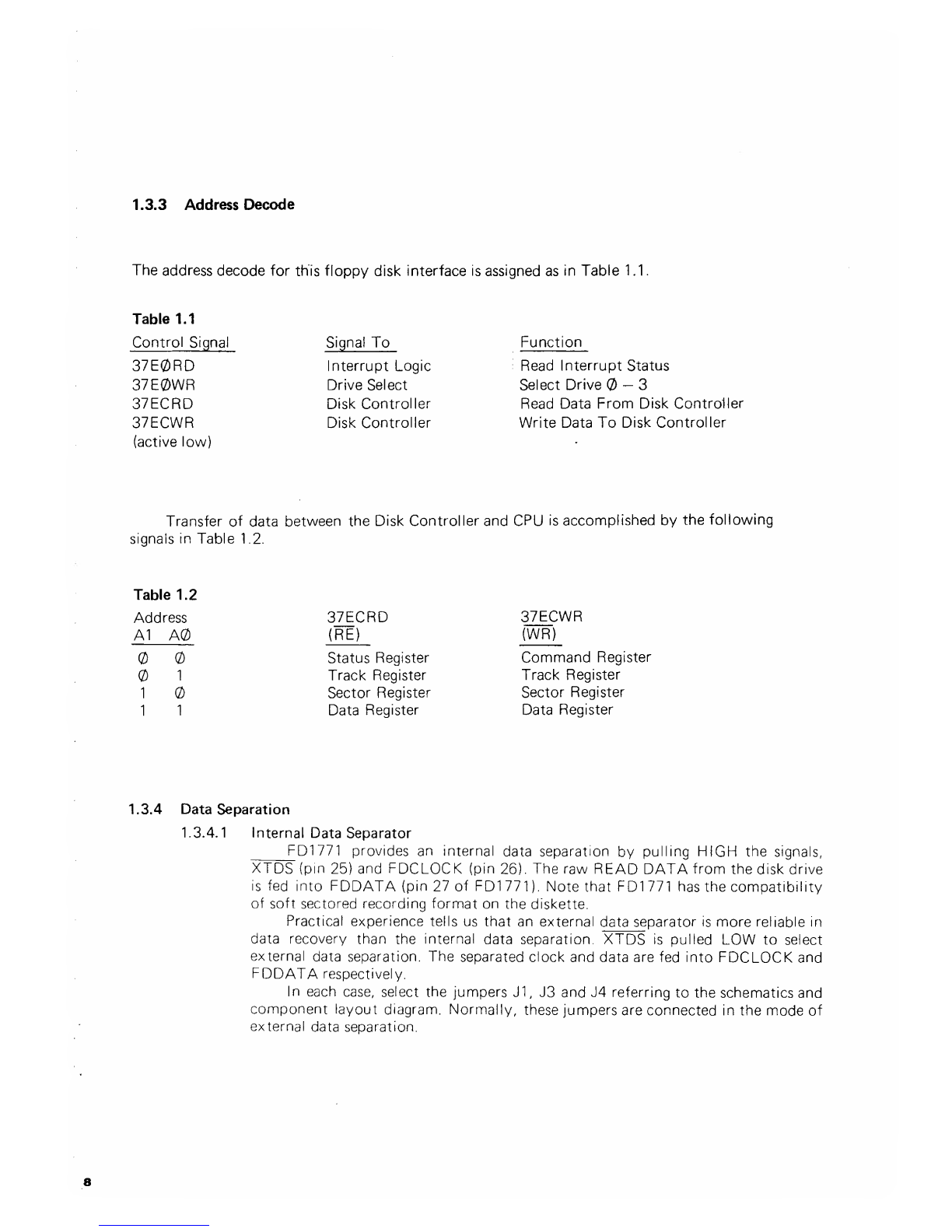

1.3 Floppy Disk Interface ________________ 7

1.3.1 Controller Chip and Clock __„__„___. 7

1.3.2 Drive Select __„„_„______. 7

1.3.3 Address Decode ____________ 8

1.3.4 Data Separation _____ ______. 8

1.3.4.1 Internal Data Separator __ _—__ _. __ _. 8

1.3.4.2 External Data Separator __„„____. 9

1.3.5 Side Select __. __ _ ______.11

1.3.6 Card-Edge Pin Assignemnt

for Floppy Disk Interface _—__„___ __ _.1

1

1.4 Parallel Printer Interface ____'„ ____ __.12

1.4.1 Printer Status _____„_____. 12

1.4.2 Card-Edge Pin Assignment

for Parallel Printer Interface —_______.12

1.5 Connectors for Further Expansion ________. .13

1.5.1 Pin Assignment for the 50-pin Connector ___. _„ „ .13

1.5.2 Pin Assignment for the 20-pin Connector —___—_.14

1.6 Power Supply and Regulators __ ____ ____ __.15

2. EG3020 RS-232-C INTERFACE ___ _ ___ ___.16

2.1 UART __„_____„____. 16

2.1.1 Control Bits ____-____ _ _.16

2.1.2 Clock __„________„. 16

2.2 Baud Rate Generator _____, -___ ___.17

2.3 Address Decode ____ ____ __.___. 17

2.4 TTL/E IALevel Shifters ___________ 18

2.5 Busses __-------_--_.18

2.5.1 Pin Assignment for the RS-232-C Bus _-_____.18

2.5.2 Pin Connections between the Expander and the RS-232-C Interface __ _.19

2.6 Voltage Regulator ___ ___ _ _ ____-.19

3. EG3021 DOUBLE DENSITY ADAPTER (FLOPPY DISK) _____.20

3.1 Introduction ______ _„____. 20

3.2 Floppy Disk Controllers ___________ 20

3.3 Chip Select Decode Logic and Multiplexer _____. __.20

3.4 16 MHz Clock Generator _„„_„„____. 21

3.5 Write Precompensation ___ _____ _ _ __ _.21

3.6 Data Separator ______ __ _ _ __.21

3.6.1 Single Density _. _____ ______ 21

3.6.2 Double Density __ _ _______ __.23

4. EG3022 S-100 BUS INTERFACE ____„___.24

4.1 introduction ___ _____ __ __ ___.24

4.2 Address Lines ____ —______ _ .24

4.3 Data Lines ____„_______ 24

4.4 Control/Status Lines _„_____ ____.24

4.5 Vectored Interrupt Lines __ „________.25

4.6 Power Lines _________ __ ____ .25