Introduction EP-6CXA2C

Page 1-4

System Overview

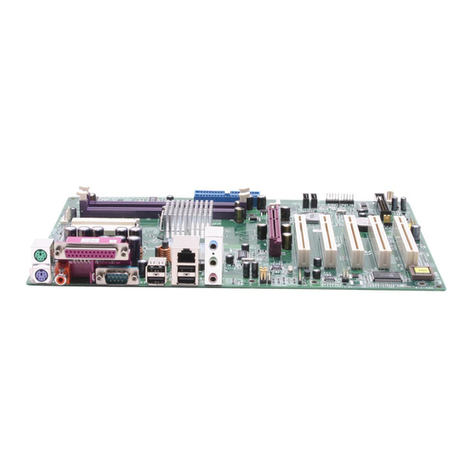

The EP-6CXA2C is designed with Intel®820 chipset. The Intel®820 chipset

includes MCH(FW82820), ICH(FW82801) and FWH (N82802AB) three chips.

The Intel®820 chipset is the third generation desktop chipset designed for Intel’s

SC242 architecture and the first chipset to support the 4X capability of the AGP

2.0 Interface Specification and 400MHz Direct RDRAM. The 400MHz, 16bit,

double clocked Direct RDRAM interface provides 1.6GB/s access to main

memory. A new chipset component interconnect, the hub interface, is designed

into the Intel®820 chipset to provide more efficient communication between

chipset components.

Support of AGP 4X, 400MHz Direct RDRAM and the hub interface provides a

balanced system architecture for the Pentium®III or later SC242 architecture

processor minimizing bottlenecks and increasing system performance. By

increasing memory bandwidth to 1.6GB/s through the use of AGP 4X, the Intel®

820 chipset will deliver the data throughput necessary to take advantage of the

high performance provided by the powerful Pentium®III or later SC242 architec-

ture processor.

The Intel®820 chipset architecture removes the requirement for the ISA expan-

sion bus that was traditionally integrated into the I/O subsystem of Intel chipsets.

This removes many of the conflicts experienced when installing hardware and

drivers into legacy ISA systems. The elimination of ISA will provide true plug-and

play for the Intel®820 platform.

Intel®820 chipset contains three core components: the Memory Controller Hub

(MCH), the I/O Controller Hub (ICH) and the Firmware Hub (FWH). The MCH

integrates the 133MHz, Pentium®II/III processor bus controller, AGP 2.0

controller, 400MHz direct RDRAM controller and a high-speed hub interface for

communication with the ICH. The ICH integrates an UltraATA/66 controller, USB

host controller, LPC interface controller, FWH interface controller, PCI inter-

face controller, and a hub interface for communication with the MCH. The Intel®

820 chipset will provide the data buffering and interface arbitration required to

ensure that system interfaces operate efficiently and provide the system bandwidth

necessary to obtain peak performance the Pentium®III or later SC242

architecture.