Fastrax IT321 Parts list manual

REV 1.2

TECHNICAL DESCRIPTION

Fastrax IT321 OEM GPS

Receiver

This document describes the electrical connectivity and

main functionality of the Fastrax IT321 OEM GPS

Receiver.

November 19, 2007

Fastrax Ltd.

2007-11-19

Page 2 of 35

IT321_Tech_doc_12

TRADEMARKS

Fastrax® is trademark of Fastrax Ltd.

SiRF®, SiRFStar TM, TricklePowerTM, Push-to-FixTM, SiRFDriveTM are registered

trademark and trademarks of SiRF Technology, Inc.

All other trademarks are trademarks or registered trademarks of their respective

holders.

2007-11-19

Page 3 of 35

IT321_Tech_doc_12

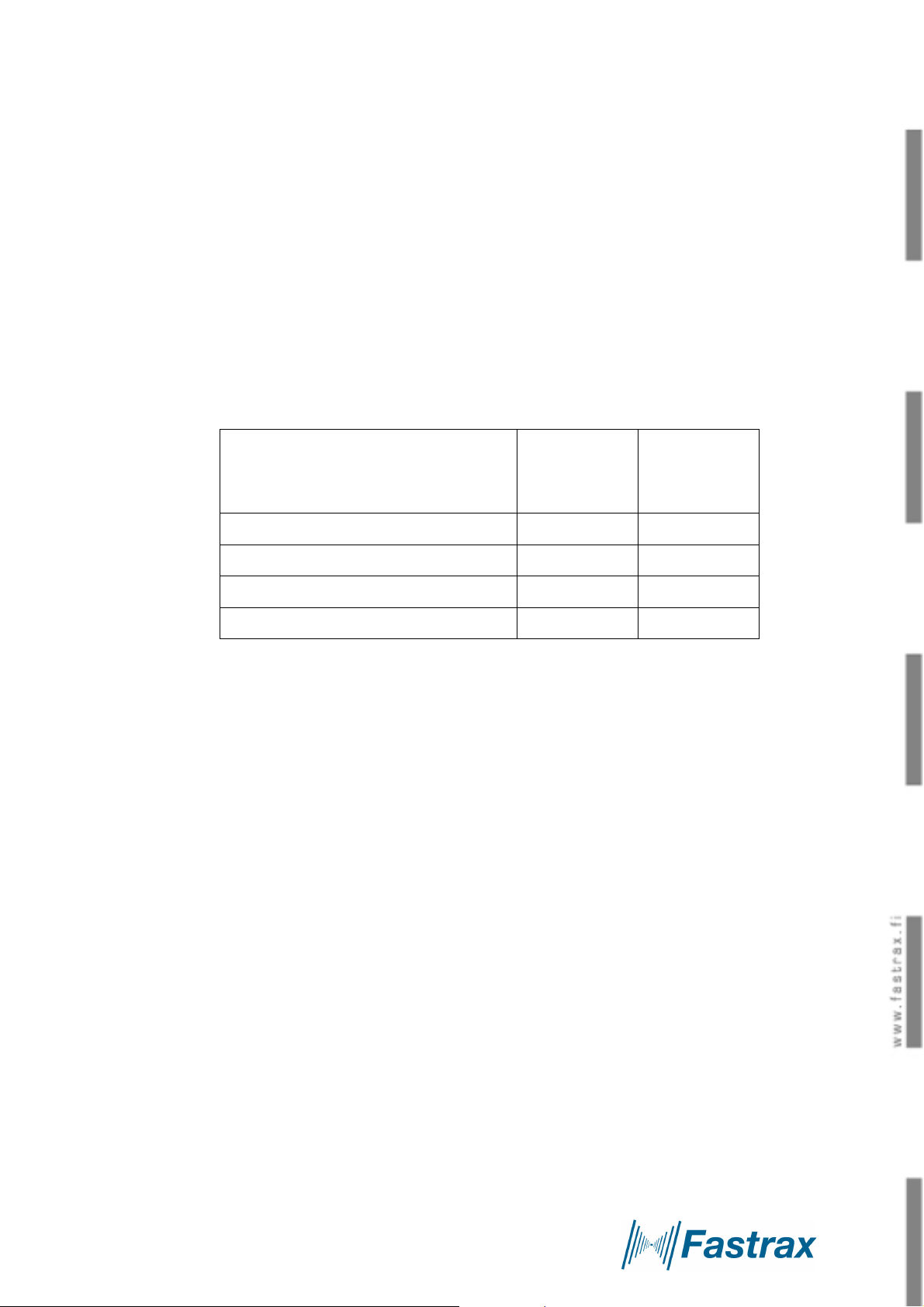

CHANGE LOG

Rev. Notes Date

1.0 Initial documentation 2007-08-24

1.1 Module name change to IT321, abs. max power

dissipation 300mW, oper. temp. range -30C…

+85C, GPIO6 & 13 added to HW rev. B, added

VDD ripple specification, added ON_OFF tim-

ing, removed solder profile picture, added tape

and reel spec, changed Application Board

documents to rev C.

2007-10-11

1.2 GPIO13 changed to GPIO2 (IT321 PCB rev. C).

Updated protocol configuration Table 3.

2007-11-19

2007-11-19

Page 4 of 35

IT321_Tech_doc_12

CONTENTS

1. GENERAL DESCRIPTION .............................................................................. 7

1.1 Block diagram ...................................................................................... 8

1.2 Frequency Plan .................................................................................... 8

2. SPECIFICATIONS........................................................................................... 9

2.1 General ................................................................................................. 9

2.2 Absolute maximum ratings................................................................ 10

3. OPERATION ................................................................................................. 11

3.1 Operating modes................................................................................ 11

3.2 Normal mode ...................................................................................... 11

3.2.1 Output configuration ................................................................ 11

3.2.2 Power management system modes ......................................... 12

3.3 Hibernate mode .................................................................................. 13

3.4 Programming mode............................................................................ 13

3.5 Procedure for re-programming the flash firmware .......................... 14

4. CONNECTIVITY ............................................................................................ 16

4.1 Connection assignments................................................................... 16

4.2 Power supply...................................................................................... 18

4.3 Configuration select: GPIO 6 & 2 ...................................................... 18

4.4 Boot Control inputs ........................................................................... 18

4.5 ON_OFF control input........................................................................ 19

4.6 Antenna input..................................................................................... 20

4.6.1 Active GPS antenna................................................................. 21

4.7 UART................................................................................................... 21

4.8 PPS ..................................................................................................... 21

4.9 ELCK ................................................................................................... 21

4.9.1 GPIO1 Valid fix indicator.......................................................... 22

4.9.2 TSYNC/GPIO8......................................................................... 22

4.10 Mechanical dimensions and contact numbering.............................. 22

4.11 Suggested pad layout and pin out .................................................... 23

5. MANUFACTURING ....................................................................................... 24

5.1 Assembly ............................................................................................ 24

5.2 Suggested Reflow soldering profile.................................................. 24

5.3 Moisture sensitivity............................................................................ 24

2007-11-19

Page 5 of 35

IT321_Tech_doc_12

5.4 Tape and reel...................................................................................... 24

6. REFERENCE DESIGN .................................................................................. 26

6.1 Reference circuit diagram ................................................................. 26

6.2 PCB layout issues.............................................................................. 27

7. IT321 APPLICATION BOARD....................................................................... 29

7.1 Card Terminal I/O-connector ............................................................. 29

7.2 Bill of materials, PCB rev C ............................................................... 31

7.3 Circuit drawing, rev C ........................................................................ 32

7.4 Assembly drawing, Top side, rev C .................................................. 33

7.5 Artwork, layer 1 (Top), rev C ............................................................. 33

7.6 Artwork, layer 2, rev C ....................................................................... 34

7.7 Artwork, layer 3, rev C ....................................................................... 34

7.8 Artwork, layer 4 (Bottom), rev C........................................................ 35

2007-11-19

Page 6 of 35

IT321_Tech_doc_12

COMPLEMENTARY READING

The following Fastrax reference documents are complementary

reading for this document. All operating and firmware related

documentation is also available at www.fastrax.fi

Ref. # File name Document name

The following SiRF reference documents are also complementary

reading for this document. All operating and firmware related

documentation is available from SiRF Technology, Inc.

Ref. # File name Document name

I GSC3LTProductInsert.pdf GSC3LT Brochure

II NMEA Reference Man-

ual.pdf

NMEA Reference Manual

III SiRF Binary Protocol Ref-

erence Manual.pdf

SiRF Binary Protocol Ref-

erence Manual

2007-11-19

Page 7 of 35

IT321_Tech_doc_12

1. GENERAL DESCRIPTION

The Fastrax IT321 is an OEM GPS receiver module, which provides

the SiRFstarIII receiver (ref I) functionality using the state of the art

SiRF GSC3LT chip. The module has tiny form factor 10.4x14.0mm,

height is 2.3mm nominal (2.6mm max). The Fastrax IT321 receiver

provides low power and very fast TTFF together with weak signal ac-

quisition and tracking capability to meet even the most stringent per-

formance expectations.

The module is available with two versions:

•SiRF ROM code version

•Early samples can be provided with embedded flash version

(4Mbit in GSC3LTf) for evaluation with GSWLT3 firmware.

The module provides complete signal processing from antenna input

to serial data output in either NMEA messages (ref II) or in SiRF bi-

nary protocol (ref III). The module requires a main power supply VDD,

which can be powered directly from a raw battery voltage. The Fas-

trax IT321 module interfaces to the customer’s application via one se-

rial port. Serial data and I/O signal levels are 1.8V or 1.2V CMOS

compatible.

The antenna input supports passive and active antennas and provides

also an internally generated antenna bias supply.

This document describes the electrical connectivity and main func-

tionality of the Fastrax IT321 OEM GPS Receiver module.

2007-11-19

Page 8 of 35

IT321_Tech_doc_12

1.1 Block diagram

RF BB

(flash)

SAW

LNA

GSC3LT

TCXO

RTC

+2.7V

CTRL_LNA

ANT

UART A

BOOT1&2

VDD

+2.7V

CTRL_TCXO

CTRL_TCXO

CTRL_LNA

ON_OFF

Figure 1 Block diagram

1.2 Frequency Plan

Clock frequencies generated internally at the Fastrax IT321 receiver:

•32768 Hz real time clock (RTC)

•16.369 MHz master clock (TCXO)

•1571.424 MHz local oscillator of the RF down-converter

2007-11-19

Page 9 of 35

IT321_Tech_doc_12

2. SPECIFICATIONS

2.1 General

Table 1 General Specifications

Receiver GPS L1 C/A-code, SPS

Chip set & Navigation sensitivity SiRF GSC3LT -159dBm

Channels 20 physical (12 in tracking, firmware limited)

Update rate 1 Hz default (fix rate configurable with SiRF

TricklePower)

Supply voltage, VDD +3.25V…+5.5 V (can be raw battery supply)

Supply voltage, VDD ripple max 300mVpp @ f<10kHz & 3mVpp @ f>100kHz

Power consumption, VDD 90 mW typical @ 3.3V (without Antenna bias)

Power consumption, VDD 65 uW typical @ 3.3V (during Hibernate state)

Antenna net gain range 0…+25dB (+10… +20dB suggested for optimum

performance)

Antenna bias voltage +2.7V (+0.3/-0.5V)

Antenna bias current 15 mA max

Storage temperature -40ºC…+85ºC

Operating temperature (note 1) -30ºC…+85ºC

Serial port configuration NMEA (configurable to SiRF binary)

Serial data format 8 bits, no parity, 1 stop bit

Serial data speed 4800 baud (configurable)

I/O signal levels, VCC = 1.8V or

1.2V

CMOS compatible: low state 0…0.25xVCC; high

state 0.75…1.0xVCC

I/O sink/source capability +/- 2 mA max.

PPS output +/-1us accuracy

2007-11-19

Page 10 of 35

IT321_Tech_doc_12

Note 1: Operation in the storage temperature range –40°C… +85°C is

allowed but Time-to-First-Fix and other GPS performance may be de-

graded.

2.2 Absolute maximum ratings

Table 2 Absolute maximum ratings

Item Min Max unit

Operating and storage temperature -40 +85 ºC

Power dissipation - 300 mW

Supply voltage, VDD -0.3 +5.5 V

Input voltage on any input connection,

VCC = 1.2V or 1.8V

-0.3 VCC+0.3V V

RF input level - +15 dBm

2007-11-19

Page 11 of 35

IT321_Tech_doc_12

3. OPERATION

3.1 Operating modes

After power up the IT321 module (with Flash version) boots from the

internal ROM or from flash memory depending on the BOOT1 and

BOOT2 control inputs (see Table 4).

With ROM code version the BOOT1 & 2 inputs can be left uncon-

nected but the inputs GPIO6 & 2 determine baud rate and protocol

selection (see Table 3). Modes of operation:

•Normal mode (Navigation)

oPower management system modes

•Hibernate mode

•Programming mode

3.2 Normal mode

The IT321 receiver will start navigation automatically after power up

using all (if any) aiding information on GPS time, satellite ephemeris

and Last Known Good (LKG) position information provided by the

non-volatile back up block (RTC & RAM). The power consumption will

vary depending on the amount of satellite acquisitions and number of

satellites in track. This mode is also referenced as Full Power or

Navigation state.

Navigation is available and any configuration settings are valid as

long as the VDD power supply is active. When the VDD is powered

off, settings are reset to factory configuration and receiver performs a

cold start on next power up.

3.2.1 Output configuration

With ROM code version user can select the data output configuration

by setting the GPIO 6 and 2, which are read at power up. Configura-

tion is selected by setting GPIO 6 and 13 to low or high state accord-

ing to the following table.

2007-11-19

Page 12 of 35

IT321_Tech_doc_12

Table 3 Output configurations

Configuration 1 2 3

GPIO6 input low high low

GPIO2 input low low high

Protocol NMEA 3.01 SiRF binary NMEA 3.01

Baud rate 4800,n,8,1 57600,n,8,1 57600,n,8,1

NMEA mes-

sages @1s

GGA, GSA,

GSV@5s, RMC, VTG

- GGA, GSA, GSV,

RMC, VTG, (EE)

Binary mes-

sages @1s

2, 4, 9, 13, 18, 41,

(EE)

GPIO1 output,

no navigation

high high high

GPIO1 output,

navigation

100ms high @ 1Hz 100ms high @

1Hz

100ms high @ 1Hz

DGPS/SBAS Disabled Enabled Enabled

Static naviga-

tion filter

Disabled Disabled Enabled

Track smooth-

ing filter

Enabled Enabled Enabled

Internal DR Disabled Disabled Enabled

Extended

Ephemeris

Disabled Enabled Enabled

3.2.2 Power management system modes

The IT321 module supports also SiRF operating modes for reduced

average power consumption (ref III) like Adaptive TricklePowerTM and

Push-to-FixTM modes:

1. Adaptive TricklePower: In this mode the receiver stays at Full

Power for 200… 900ms and provides a valid fix. Between fixes

with 1… 10 sec interval the receiver stays in a low power mode

to reduce power drain. TricklePower mode is configurable with

2007-11-19

Page 13 of 35

IT321_Tech_doc_12

SiRF binary protocol message ID151 (ref III). The receiver

stays once in while in Full Power automatically to collect new

ephemeris and almanac data from rising satellites.

2. Push-to-Fix: In this mode the receiver is configured to wake up

periodically, typically every 1800 sec, to collect new ephemeris

data from rising satellites. Rest of the time the receiver stays in

a low power mode. The host wakes up the receiver by ON_OFF

control input interrupt (pulse low-high-low >62us) after which

the receiver performs Hot start and a valid fix is available within

few seconds. This mode is configurable with SiRF binary proto-

col message ID151 (ref III).

Note that position accuracy is somewhat degraded in power man-

agement modes when compared to full power operation.

3.3 Hibernate mode

Hibernate mode means a low quiescent power state where only the

internal non-volatile RTC and RAM block is powered on. The main

supply input VDD is kept active all the time, even during Hibernate

mode. The Hibernate mode is entered by host interrupt at ON_OFF

control input (pulse low-high-low >62us).

Other internal blocks like digital baseband and I/O block are internally

powered off, thus output levels are at low state and any inputs, ex-

cluding ON_OFF input, like UART RXA should be disconnected or

forced to low state.

The receiver wakes up from Hibernate mode and returns to Normal

mode after next ON_OFF interrupt (pulse low-high-low >62us) allow-

ing fast TTFF with either Hot or Warm start.

3.4 Programming mode

Programming mode is only available with the flash version (GSC3LTf)

with the embedded 4Mbit flash memory. The ROM code version does

not support programming.

Programming via HW-booting mode is utilized by forcing the BOOT1

and BOOT2 control inputs for high state (Flash programming, follow-

ing table) during power up. Now the GPS module boots for the UART

and waits for the boot loader commands from the host (an application

running on the host, SiRFFlash). It is suggested that all applications

using embedded flash version should support the HW-booting by ac-

2007-11-19

Page 14 of 35

IT321_Tech_doc_12

cess to UART (TXA & RXA), BOOT1 and BOOT2 input signals and

VDD On/Off control.

Note that during the flash update process the serial data speed is

changed and thus the serial line connection should be a direct line to

the host without any transferring utilities that may cause failure during

speed change.

Table 4 BOOT modes

BOOT mode BOOT2

(internal

pull up)

BOOT1

(internal

pull down)

Flash (Normal mode) 0 0

Reserved 0 1

Flash programming UART A 1 1

ROM (Normal mode) (Default) 1 0

3.5 Procedure for re-programming the flash firmware

1. Connect UART (RXA and TXA signals) to PC via RS232 converter.

2. Set the module to UART boot mode: Power up the module to Flash

programming mode according to Table 4. when using Fastrax

Evaluation kit power up the kit and toggle Prog/Reset switch to

Prog position.

3. Start SiRFFlash application on PC.

4. Browse for the flash *.s file.

5. Check the Communication setting from the SiRFFlash to meet

your PC serial port.

6. Press Execute at SiRFFlash. Now the flashing starts.

7. After flashing has finished, recover normal operation by toggling

power VDD off-on and setting boot mode to Flash mode according

to Table 4.

2007-11-19

Page 15 of 35

IT321_Tech_doc_12

Figure 2 SiRFFlash utility settings

2007-11-19

Page 16 of 35

IT321_Tech_doc_12

4. CONNECTIVITY

4.1 Connection assignments

The I/O connections are available as soldering pads on the bottom

side of the module. These pads are also used to attach the module on

the motherboard in application. All unconnected I/O should be left

open (floating) unless instructed to use pull external up or pull down.

Table 5 Connections

Contact Signal name I/O Alternative

signal name

Signal description

1 ANT I/O - Antenna signal input 50 ohm, An-

tenna bias voltage +2.7V output

2 GND - - Ground

3 GND - - Ground

4 GND - - Ground

5 GND - - Ground

6 GPIO6 I - Control input for protocol configura-

tion. VCC=1.8V. For default pull

low.

7 ON_OFF I - Interrupt toggle (pulse low-high-low

100ms) for switching between Hi-

bernate/Normal mode. VCC=1.2V.

Pull to low state with e.g. 10kohm if

not used.

8 GND - - Ground

9 VDD - - Power supply, can be raw battery

voltage. Note ripple voltage spec.

10 BOOT1 I - BOOT select 1. Can be left uncon-

nected with ROM version.

With flash version connect to

BOOT2 signal and pull low with

R<5kohm. Has internal pull down

resistor 100kohm. VCC=1.8V.

2007-11-19

Page 17 of 35

IT321_Tech_doc_12

11 GND - - Ground

12 TSYNC I/O GPIO8 Option for Timing pulse input in A-

GPS version. Pull low when not

used with e.g. 10kohm. VCC=1.8V.

13 GPIO2 I - Control input for protocol configura-

tion. VCC=1.8V. For default pull

low.

14 GND - - Ground

15 GPIO1 O - Valid fix indicator output. Can be

left unconnected. VCC=1.8V

16 ECLK I - Option for external clock input in A-

GPS version. Pull low state with

e.g. 10kohm if not used.

VCC=1.8V.

17 GND - - Ground

18 RXA I - UART A async. Input. Has internal

pull up resistor 100kohm.

VCC=1.8V.

19 TXA O - UART A async. Output. VCC=1.8V.

20 PPS O - 1PPS signal output. VCC=1.8V.

21 GND - - Ground

22 BOOT2 I - BOOT select 2. Can be left uncon-

nected with ROM version.

With flash version connect to

BOOT1 signal and pull low with

R<5kohm. Has internal pull up re-

sistor 100kohm. VCC=1.8V.

23 GND - - Ground

24 GND - - Ground

Contact Signal name I/O Alternative

signal name

Signal description

2007-11-19

Page 18 of 35

IT321_Tech_doc_12

4.2 Power supply

The IT321 module requires only one power supply VDD, which can be

supplied directly from a battery since the module has internal regula-

tors. Keep the supply active all the time in order to keep the non-

volatile RTC & RAM active for fastest possible TTFF.

Main power supply VDD current varies according to the processor

load and satellite acquisition. Typical VDD peak current is 45mA dur-

ing acquisition. Typical VDD current in low power Hibernate mode is

20uA.

The IT321 allows about 300mVpp ripple voltage at the supply VDD

below 10kHz frequency. The ripple voltage should be reduced further

at VDD supply below 3mVpp at 100kHz frequency or higher. E.g. if

the battery that provides the supply for VDD is connected to a

switched mode regulator operating at 100kHz, the resulting voltage

ripple shall be reduced below 3mVpp by a suitable by-pass capacitor

or by external low pass filter prior VDD supply input.

4.3 Configuration select: GPIO 6 & 2

The data output protocol configuration is defined using the GPIO 6

and 13 control inputs. After power up the value is read and the con-

figuration is processed according the Table 3 (in previous chapter).

The GPIO 6&2 inputs should be kept valid after power up for at least

500 ms to allow the internal power-on-reset delay to settle. I/O levels

are CMOS 1.8V compatible.

4.4 Boot Control inputs

The boot source is defined in the internal boot ROM sector by using

the BOOT1 and BOOT2 control inputs. After power up the value is

read and the boot is processed according the Table 4 (in previous

chapter).

The BOOT inputs should be kept valid after power up for at least 500

ms to allow the internal power-on-reset delay to settle. I/O levels are

CMOS 1.8V compatible.

2007-11-19

Page 19 of 35

IT321_Tech_doc_12

NOTE

With ROM code version the BOOT inputs

can left unconnected (floating) since internal

pull ups are configured to ROM mode as de-

fault.

NOTE

With embedded flash version the BOOT1

and BOOT2 input can be connected to the

same boot control source from host. Normal

operation requires external pull-down resis-

tors connected to the common input, e.g. 0

ohm… 4.7kohm.

4.5 ON_OFF control input

The ON_OFF control input can be used to control the receiver be-

tween Normal or Hibernate modes and also to generate interrupt in

Push-to-Fix operation.

The ON_OFF interrupt is generated by a low-high-low toggle, which

should be longer than 62us and less than 1s (suggestion is abt.

100ms pulse length). Input level is CMOS 1.2V compatible. Do not

generate ON_OFF interrupts less than 1 sec intervals. Especially take

care that any multiple switch bounce pulses are filtered out.

After power up the first ON_OFF interrupt sets the module to Hiber-

nate mode. Next ON_OFF interrupt wakes up the module for Normal

(Navigation) operation. Consequent ON_OFF interrupts switch the

operation mode between Hibernate and Normal modes.

During Hibernate mode internal I/O supply is internally powered off,

thus output levels are at low state and any inputs, excluding ON_OFF

input, like UART RXA should be disconnected or forced to low state.

2007-11-19

Page 20 of 35

IT321_Tech_doc_12

Figure 3 Suggested ON_OFF Hibernate control timing diagram.

NOTE

If not used, pull ON_OFF signal to low state

with e.g. 10kohm pull down resistor.

If used, note that the input is CMOS 1.2V

compatible. Use e.g. a resistive divider to

reduce input voltage to 1.2V when using

1.8V or 3.3V host control source.

Do not generate multiple ON_OFF interrupts

less than 1 sec intervals. Especially filter out

multiple pulses generated by a mechanical

switch bounce.

4.6 Antenna input

The module supports passive and active antennas. The antenna input

impedance is 50 ohms. During Normal (navigating) operation, the in-

put provides also a bias supply (+2.7V typ.). When the navigation is

stopped, the antenna bias is switched off automatically.

NOTE

Passive antennas with a short-circuit to

GND should be DC blocked externally with a

18pF…1nF serial capacitor.

Table of contents

Other Fastrax GPS manuals