First International Computer VY050 User manual

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

First International Computer,Inc

Portable Computer Group HW Department

Board name : MotherBoard Schematic

Version : 0.3

Manager Sign by: AVERY

Total confirm by: AVERY

Drawing by : Spruce

VY050

Initial Date : Nov/ 18/ 2008

Confidential

Project :

Title

0.1

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN,ROC

(886-2)8751-8751

C

149Tuesday, November 18, 2008

Penryn+Candiga GM/PM45+ICH9M(VY050)

Title

Size Document Number Rev

Date: Sheet of

First International Computer,Inc.

8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Penryn

P10~15

P17~22

CORE

Processor

CPU

Intel

P47

P7,8

Cantiga

P9

Thermal

Sensor

DMI

FSB

Mem_A Bus

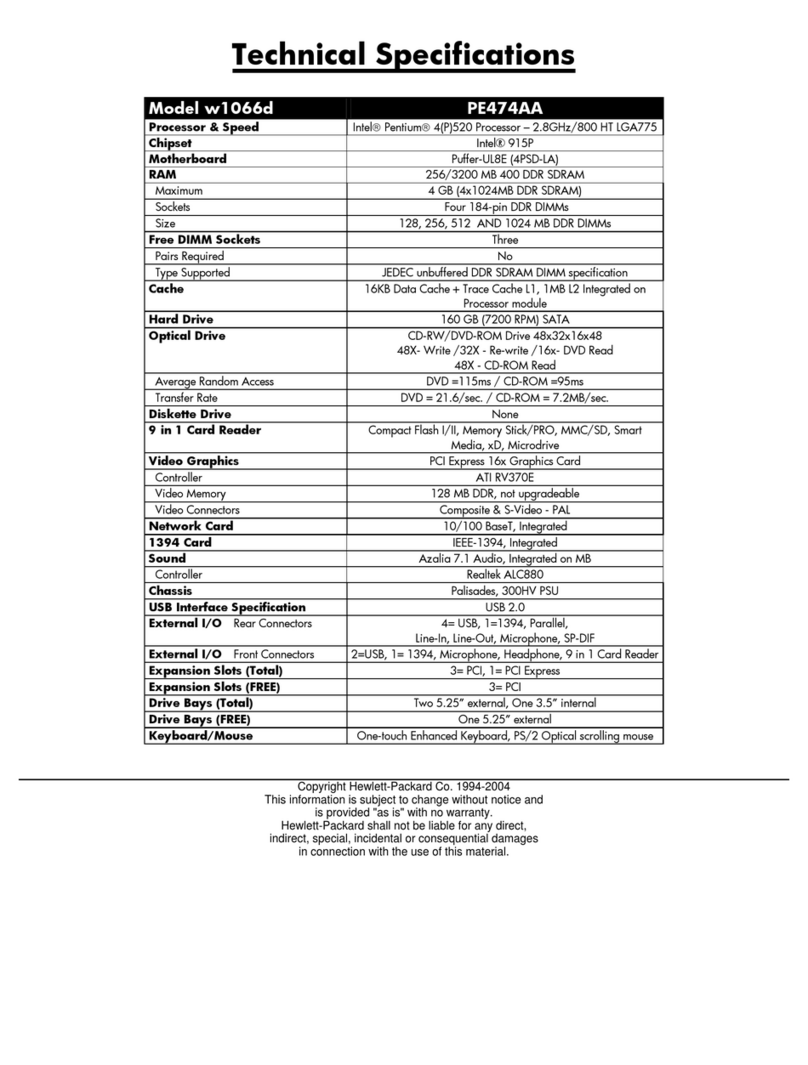

3. Block Diagram :

P46

VCCP

CPU

Lid Switch

USB 2.0

P28

USB 0,1,2

Intel NB

(G)MCH

Intel SB

ICH9M

LCD

P24

P16

DDRII SODIMM0 (A)

DDRII SODIMM1 (B)

P17

Mem_B Bus

PCIE_3

Azalia

LPC BUS

P23

Flash ROM

BIOS

P32

LED

P26

RTS5158E

ALCORCardReader

3 in 1

P32

USB 3,4

MAIN SW CNN/DIP SW

DDR2 800/667 MHz

DDR2 800/667 MHz

(667/800/1066 MHz)

(x4)

PCIE_2

SPI

P35

Speaker

P29

Mini Card (Robson)

P29

Mini Card (WLAN)

LAN 10/100/1000M

P33,34

RTL 8102E

RJ-45

PCIE_6

P35

P28P42

CCD

Glide PadInt. KB

P30

PMX

MB90F372

P30

P37

P31

Express Card

PCIE_1

USB 2.0

MDC

P28

RJ-11

CRT

P25

Reset Circuit

P23

CLKGEN

RTM875N-606-VD-GR

P18

RTC Bat

P20

P27

HDD

P27

SATA BUS

CDROM

SATA BUS

Mic In HP/SPDIF

P36

P36

Line In

P36

ALC269

P35

AzaliaCodec

Charger

P42

P43

P44

1.5VDDM

1.8/1.05/0.9VDD

VDD CORE

P46

CPU CORE

P45

P47

ACIN/ DCIN

P41

3VDD/5VDD

P42

BT

Block Diagram

0.1

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2) 8751-8751

C

2 49Tuesday, November 18, 2008

Penryn+Candiga GM/PM45+ICH9M(VY050)

Title

Size Document Number Rev

Date: Sheet of

FirstInternational Computer, Inc.

8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Voltage Rails

DCIN

VCC_CORE

Primary DC system power supply

Core Voltage for CPU

3.3V switched power rail by SUSTAT_B#

PMU3V 3.3V always on power rail by LATCH or ACIN

PMU5V 5.0V always on power rail by LATCH or ACIN

5VDDA 5.0V power rail by PSUSC#

3VDDM 5.0V switched power rail by SUSTAT_B#5VDDM

F

R

Inductor

Resistor

Q

Connector

C

Fuse

=

CN

Crystal and Osc

RP

D

UResistor Pack

Arbitrary Logic Device

Diode

Part Naming Conventions

Transistor

L

Y

Capacitor

=

=

=

=

=

=

=

=

=

Active Low signal

Net Name Suffix

# =

1.05VDDM 1.8V power rail for DDRII by PSUSC#

0.9V DDRII Termination Voltage by SUSTAT_B#

1.8VDDS

0.9VDDT_DDRII

3VDDA

4. Nat name Description:

1.5VDDM

1.05V power rail for AGTL+ termination/Core for GMCH by SUSTAT_B#

1.5V power rail for CPU PLL/DMI;PCIE;DDRII DLLs for GMCH/Core;PCIE

for ICH7m by SUSTAT_B#

Differential Impedance for Microstrip

55 ohm +/- 15%

100 ohm +/- 15%

PCIE Bus

Single End Impedance

85 ohm +/- 20%

95 ohm +/- 15%

70 ohm +/- 20%

100 ohm +/- 15%

SDVO

70 ohm +/- 20%

95 ohm +/- 15%

DMI Bus

55 ohm +/- 15%

100 ohm +/- 15%

Host Bus

55 ohm +/- 15%

55 ohm +/- 15%

95 ohm +/- 15%

DDR2 Bus

55 ohm +/- 15%

95 ohm +/- 15%

90 ohm +/- 15%

DDR2 CLK

100 ohm +/- 15%

90 ohm +/- 15%

DDR2 Strobe

95 ohm +/- 15%

100 ohm +/- 15%

110 ohm +/- 15%

Lan

SRC Clock

95 ohm +/- 15%

110 ohm +/- 15%

IEEE1394

55 ohm +/- 15%

100 ohm +/- 15%

Host Clock

100 ohm +/- 15%

50 ohm +/- 15%

USB

Differential Impedance for Stripline

55 ohm +/- 15%

55 ohm +/- 15%

LVDS

42 ohm +/- 15%

100 ohm +/- 15%

SATA

5. BoardStackup Description

PCB Layers

Layer 3

Solder Side,Microstrip signal Layer

Layer 5

Layer 6

Component Side, Microstrip signal Layer

Power Plane

Layer 1

Layer 4

Ground Plane

Stripline Layer(High Speed)

Layer 2 Stripline Layer(High Speed)

3.3V power rail by PSUSC#

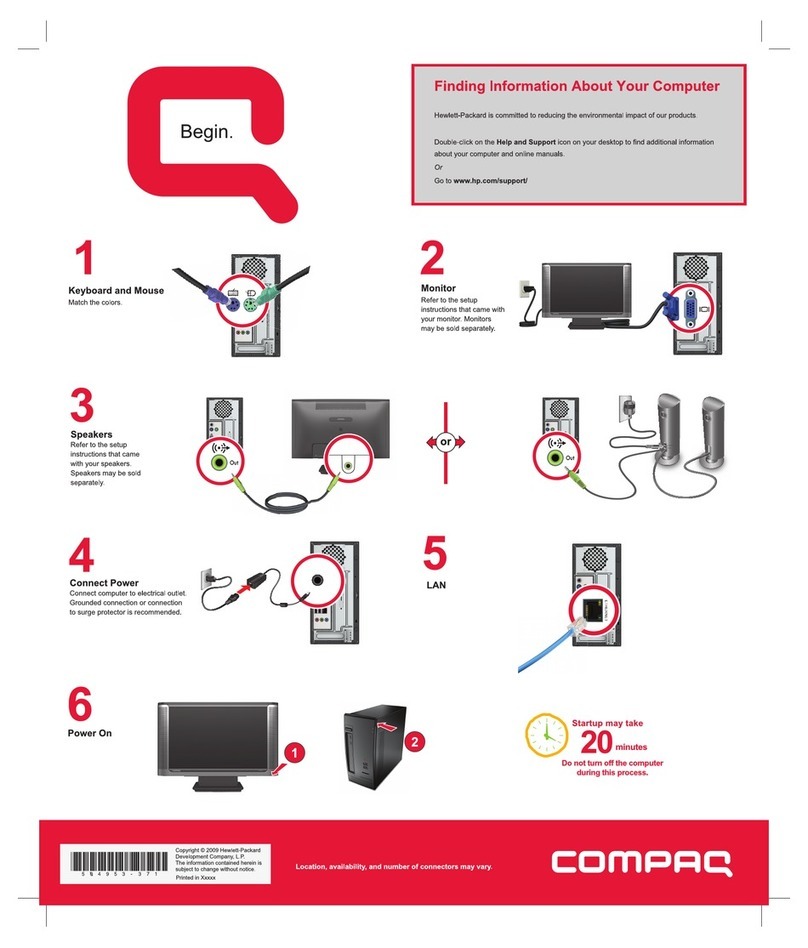

5. Timing Diagram

14. Candiga GM45 Power(5/6)

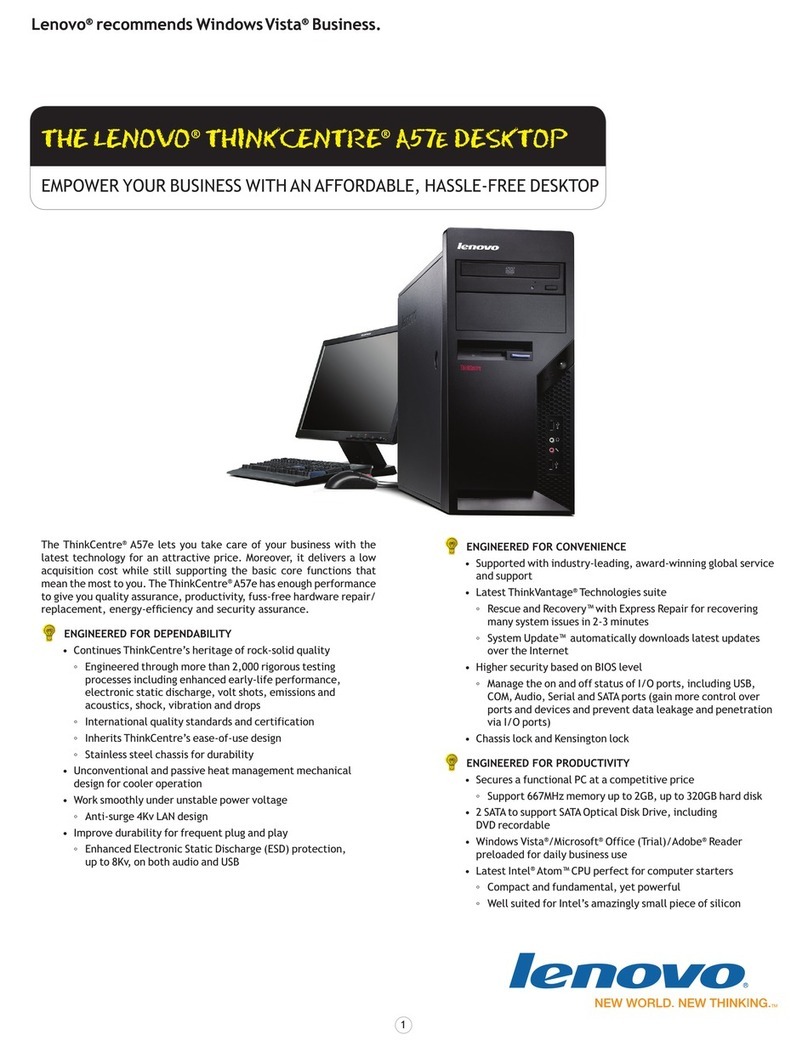

2. Block Diagram

6. Schematic Modify

13. Candiga GM45 Power(4/6)

1. Title

10. Candiga GM45 Host(1/6)

18. DDRII SDRAMSO-DIMM1

11.Candiga GM45 DMI/Graphic(2/6)

15. Candiga GM45 GND(6/6)

17. DDRII SDRAMSO-DIMM0

16. Clock Generator

9. CPU Thermal

12. Candiga GM45 DDRII(3/6)

7. Penryn Processor(1/2)

3. ANNOTATIONS

33. LAN RTL 8111C

27. HDD CNN / ODD CNN

30. INT KB / GP / SW CNN

34. TRANSFORMER

25. CRT CNN

38. ScrewHole

26. DIP SW / LED / LID SW

22. ICH9MPower/GND(4/4)

19. ICH9MPCI/PCIE/DMI(1/4)

23. Reset Circuit / SPI

21. ICH9MGPIO(3/4)

31. Express Card / CCD / BT

24. LCD CNN

32. Card-Reader RTS5158E

28. USB CNN / MDC CNN

20. ICH9MCPU/IDE/SATA(2/4)

42. Charger

47. CPU CORE

35. Azalia ALC269 Codec

37. PMX

36. HP / MIC / Int. MIC

49. SW Board

48. Audio Board

46. VDD CORE

43. 3/5VDDA/M, PMU3/5V

44. 1.5VDDM

45. 1.8VDDS / 0.9VDDS / 1.05VDDM

39. block

41. ADPIN, BATIN, ADPOUT1

29. Mini-WLAN / Robson

40. Power Block

8. Penryn Processor(2/2)

4. DDRII Layout Guideline

Annotations

0.1

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN,ROC

(886-2) 8751-8751

C

349Tuesday, November 18, 2008

Penryn+Candiga GM/PM45+ICH9M(VY050)

Title

Size Document Number Rev

Date: Sheet of

First International Computer,Inc.

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Crestline DDRII Layout Guidelines

DDRII SignalGroups

Data

Group Signal Name

Control-to-Clock

Signal Group Minimum Length Maximum Length

Command-to-Clock

Strobe-to-Clock

Data-to-Strobe

Clock - 1.0"

Clock - 1.0"

Clock - 0.5"

Clock - 0.0"

Clock + 1.0"

Strobe - 220mils

8. Layout Guideline :

SA_DQ[63..0]/SB_DQ[63..0]

SA_DM[7..0]/SB_DM[7..0]

SA_DQS[7..0]/SA_DQS#[7..0]

SB_DQS[7..0]/SB_DQS#[7..0]

SA_RAS#/SB_RAS#

SA_BS[2..0]/SB_BS[2..0]

SA_MA[13..0]/SB_MA[13..0]Address

SA_CAS#/SB_CAS#

SA_WE#/SB_WE#

SM_CS#[3..0]Control SM_CKE[3..0]

SM_ODT[3..0]

Clock SM_CK[3..0]

SM_CK#[3..0]

SA_RCVENOUT#/SB_RCVENOUT#FeedBack SA_RCVENIN#/SB_RCVENIN#

Length Matching and Length Formulas

Clock + 1.0"

Strobe - 180mils

CLK group: SM_CK[3..0],SM_CK#[3..0]

GMCH

P1

P1

L0

L0

L1

L1

L2

L2

S1

S1

SO-DIMM

Topology

Reference Plane

Single Ended Trace Impedance

Differential Mode Impedance

Differential Pair Point-to-Point

Ground

42 +/- 15%

70 +/- 20%

Nominal Trace Width Inner Layer : 7 mils

Outer Layer : 8 mils

Outer Layer : 5 mils

Nominal CKto CK# Spacing

(edge to edge) Inner Layer : 4 mils

Minimum Serpentine Spacing Inner Layer : 12 mils

Outer Layer : 15 mils

Minimum Spacing to Other DDR2 Inner Layer : 16 mils

Outer Layer : 20 mils

Minimum Isolation Spacing to non-DDR2 25 mils

PackageLength Range- P1 1000 mils +/- 250 mils

Trace Length Limit - L0 Max =50 mils (Escape)

Trace Length Limit - L1 Max =500 mils (Breakout)

Stub Length S1-Stub from via to SO-DIMM Max =200 mils (Breakin)

MB Length Limits - L0 +L1 +L2 +S1 Min = 500 mils

Max = 4500 milsTotal Length - P1 +L0 +L1 +L2 +S1 Max = 4000 mils

Total Length for Channel A: X0

TotalLength for Channel B : X1

Maximim Via Count 2 (Per side)

SCK to SCK# Length Matching Match total length to within 5mils

Clock to Clock Length Match

(Total Length) Match Channel A clocks to X0 +/- 20mils

Match Channel A clocks to X1 +/- 20mils

Breakout Exceptions (Reduce geometries

for GMCHbreak-out region) Inner Layer : 4/12 mils to other DDR2

Outer Layer : 5/15 mils to other DDR2

Max. breakout length is 500 m ils

Breakin Exceptions (Reduce geometries

for SO-DIMM break-in region) CK to CK# spacing rule waived at

connector spacing of 15 mils to

other DDR2

Max. breakin length is 2 00 mils

Escape Breakout Breakin

4/4/12 7/4/16 8/5/15

Outer Layer : 5 mils

Inner Layer : 4mils spacing allowe d

L1

Inner Layer : 12 mils

55 +/- 15%

Max =500 mils (Breakout)

Max =50 mils (Escape)

Outer Layer : 10 mils

Point-to-Point with parallel termination

GMCH

Stub Length S1-Stub from via to SO-DIMM

MB Length Limits - L0 +L1 +L2 +S1 -

From GMCH ball to SO-DIMM pad

Trace Length Limit - L1

Package Length P1

Outer Layer : 15 mils

S1

Nominal Trace Width

Max =200 mils (Breakin)

8/5/15

Breakout

3

Total Length - P1 +L0 +L1 +L2 +S1 -

From GMCH die to SO-DIMM pad

Inner Layer : 4 mils

Maximim Via Count

Minimum CTRL Trace Spacing

7/4/16

Max. breakout length is 500 m ils

Min = 500 mils

25 mils

Topology

4/4/12

Max = 4500 mils

Inner Layer : 8 mils

Minimum Spacing to Other DDR2

L2

Reference Plane

Escape

(CLK-1.0") </= CTRL </= (CLK-0.0")

Max = 5000 mils

Ground

P1

750 mils +/- 200 mils

Minimum Isolation Spacing to non-DDR2

SO-DIMM

L0

Control group: SM_CKE[3..0],SM_CS#[3..0],SM_ODT[3..0]

Characteristic Trace Impedance

L3

CTRL to SCK/SCK # Length Matching

(Total Length including package)

Breakout Exceptions (Reduce geometries

for GMCHbreak-out region)

Trace Length Limit - L0

Vtt

Max = 1500 milsTrace Length L3

Parallel Termination Resistor 56 +/- 5%

Outer Layer : 5mils spacing allowed

P1

Max = 5000 mils

Minimum CMD Bus Trace Spacing

750 mils +/- 350 mils

Ground

Package Length P1

L3

Maximim Via Count

Total Length - P1 +L0 +L1 +L2 +S1 -

From GMCH die to SO-DIMM pad

Outer Layer : 10 mils

Min = 500 mils

CTRL to SCK/SCK # Length Matching

(Total Length including package)

Nominal Trace Width

4/4

L1

Max = 1500 mils

3

Max = 4500 mils

Trace Length L3

Breakout

Inner Layer : 6 mils

4/6,5/10

Max =200 mils (Breakin)

55 +/- 15%

Minimum Isolation Spacing to non-DDR2

Parallel Termination Resistor

Vtt

25 mils

Trace Length Limit - L0

Characteristic Trace Impedance

Topology

Outer Layer : 5 mils

SO-DIMM

GMCH

Reference Plane

L2

Trace Length Limit - L1

Point-to-Point with parallel termination

Escape

Inner Layer : 4 mils

Max =500 mils (Breakout)

(CLK-1.0") </= CM D </= (CLK+1.0")

Inner Layer : 12 mils

Max =50 mils (Escape)

Outer Layer : 15 mils

Stub Length S1-Stub from via to SO-DIMM

56 +/- 5%

S1

Minimum Spacing to Other DDR2

L0

Max. breakout length is 500 m ils

Outer Layer : 5mils spacing allowed

MB Length Limits - L0 +L1 +L2 +S1 -

From GMCH ball to SO-DIMM pad

Inner Layer : 4mils spacing allowe dBreakout Exceptions (R educe geometries

for GMCHbreak-out region)

Commandgroup:

SA_MA[13..0],SB_MA[13..0],SA_BS[2..0],SB_BS[2..0],SA_RAS#,

SB_RAS#,SA_CAS#,SB_CAS#,SA_WE#,SB_WE#

4/6,5/10

GMCH

Data group: SA_DQ[63..0],SB_DQ[63..0],SA_DM[7..0],SB_DM[7..0]

Reference Plane

Outer Layer : 5mils spacing allowed

L1

Minimum DQ Bus Trace Spacing

L2

Inner Layer : 6 mils

Max = 5000 mils

Min = 500 mils

Package Length P1

Breakout Exceptions (R educe geometries

for GMCHbreak-out region)

Minimum Isolation Spacing to non-DDR2

DQ/DM to DQS Length Matching

(Total Length including

package)

Max = 4500 mils

750 mils +/- 350 mils

4/4

Escape

25 mils

S1

Trace Length Limit - L0

Stub Length S1-Stubfrom via to SO-DIMM

Ground

P1 L0

MB Length Limits - L0 +L1 +L2 +S1 -

From GMCH ball to SO-DIMM pad

2

Outer Layer : 5 mils

SO-DIMM

Topology

Maximim Via Count

Breakout

Minimum Spacing to Other DDR2

Nominal Trace Width

Outer Layer : 8 mils

Trace Length L3

Max =500 mils (Breakout)

Outer Layer : 15 mils

Max =200 mils (Breakin)

Inner Layer : 12 mils

4/6

Total Length - P1 +L0 +L1 +L2 +S1 -

From GMCH die to SO-DIMM pad Max = 1500 mils

Point-to-Point

Max. breakout length is 500 mi ls

Max =50 mils (Escape)

Match DQ/DM to [SDQS - 200mils]

+/- 20mils, per byte lane

55 +/- 15%

Inner Layer : 4 mils

Trace Length Limit - L1

Characteristic Trace Impedance

Inner Layer : 4mils spacing allowed

Minimum Serpentine Spacing Same as DQ-to-DQ r outing

S1

Breakout Exceptions (R educe geometries

for GMCHbreak-out region)

Minimum Spacing to Other DDR2

P1

Match total length to within 5mils

Max =50 mils (Escape)

Differential Pair Point-to-Point

Max = 5000 mils

Max. breakin length is 2 00 mils

DQS to DQS# Length Matching

Trace Length Limit - L0

L2

Clock to Clock Length Match

(Total Length include package)

2 (Per side)

Ground

Min = 500 mils

DQS to DQS# spacing rule

waived at connector spacing of

10 mils to other DDR2

Outer Layer : 10 mils

SingleEnded Trace Impedance

Breakout

Max =200 mils (Breakin)

55 +/- 15%

Outer Layer : 5 mils

25 mils

Breakin

P1

Breakin Exceptions (Reduce geometries

for SO-DIMM break-in region)

750 mils +/- 350 mils

5/5/10

Data Strobe group: SA_DQS[7..0],SA_DQS[7..0]#,SB_DQS[7..0],SB_DQS[7..0]#

Escape

Stub Length S1-Stubfrom via to SO-DIMM

Differential Mode Impedance

L2

Max = 4500 mils

Inner Layer : 4 mils

SO-DIMM

Inner Layer : 8 mils

85 +/- 20%

Minimum Isolation Spacing to non-DDR2

GMCH

PackageLength Range- P1

4/4/12

Reference Plane

L1

S1

Inner Layer : 4 mils

Outer Layer : 15 mils

Max =500 mils (Breakout)

Nominal Trace Width

Nominal DQS to DQS# Spacing

(edge to edge)

Topology

Max. breakout length is 500 mi ls

Minimum Serpentine Spacing

L1

4/4/8

Inner Layer : 8mils to other DDR2

Inner Layer : 12 mils

L0

Trace Length Limit - L1

Maximim Via Count

Outer Layer : 5 mils

L0

Outer Layer : 10 mils to other DDR2

Outer Layer : 15 mils

Inner Layer : 12 milsMinimum DQS to DQ Spacin g

MB Length Limits - L0 +L1 +L2 +S1 -

From GMCH ball to SO-DIMM pad

Total Length - P1 +L0 +L1 +L2 +S1 -

From GMCH die to SO-DIMM pad

(CLK-0.5") </= D QS </= (CLK+1.0")

Feedback group:

SA_RCVENIN#],SA_RCVENOUT#,SB_RCVENIN#],SB_RCVENOUT#

These signals are routed internally on the GMCH package and don't require an y

routing on the MB. As a result, can be leftas NC.

SL SL MS

MS SLSL MS

SL/MSMS SL MS

SL/MS

SL/MS

SL MS

MS SL/MS

SLMS SL MS

4/4

DDRII Layout Guideline

0.1

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN,ROC

(886-2) 8751-8751

C

449Tuesday, November 18, 2008

Penryn+Candiga GM/PM45+ICH9M(VY050)

Title

Size Document Number Rev

Date: Sheet of

First International Computer,Inc.

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Tsft_star_vcc(3ms max)

GMCHPWRGD

Tcpu_up

Tboot

Vccgmch

Vid

Vcc-core

Tvccp_up

VID

Vccp

CLK_ENABLE#

Tgmch_pwrgd

Vccp_UP

IMVP6 Power On Sequencing Timing Diagram

Tboot-vid-tr(100uS max)

Tcpu_pwrgd(3~20mS)

IMVP4_PWRGD

CPU_UP

Vboot

VR_ON

PSUSC0

VDDM,VDDS

To ODEM and ICH4

PM_PWROK

From ODEM to CPU

AGTL+_CPURST0

PMU5V/PMU3V

BATTERY ONLY POWER ON TIMING

DCON

To ICH4

VDDA

CPU_PWRGD

To clock generator

VCCP/1.2VDDM

To ICH4

VR_ON

VCORE_CPU

From ICH4

PM_SLP_S30/S40/S50

SYS_PWROK

CK408_PWRGD0

From ICH4 to CPU

To ODEM/other PCI device

SUSTAT_B0

PCI_RST0

VCORE_ON

From ASIC_B0

From ASIC_B0

PM_RSTRST0

MAINSW0_ICH

POWSW0

PM_VGATE

VRON_VCCP

H

From ASIC_B0

CPU_PWRGOOD

VR_ON

CK408_PWRGD0

PM_VGATE

DCON

H

S3 SUSPEND AND RESUME TIMING

H

VCCP,1.2VDDM

SYS_PWROK

From ASIC_B0

H

To ICH4_M

H

From ICH4_M

1.5VDDS AND

H

PM_PWROK

SUSTAT_B0

VCORE_CPU

Generator

VDDM

PMU5V/PMU3V

PM_SLP_S40/S50

VRON_VCCP

PM_RSMRST0

H

DDR_PWRGD

To ODEM/other

PCI device

PCI_RST0

VDDA

From ODEM to CPU

To clock

VDDS

PSUSC0

ToICH4 and ODEM

From ICH4_M

VCORE_ON

PM_SLP_S30

POWSW0

From ICH4 to CPU

AGTL+_CPURST0

7. power on& off & S3 Sequence :

Tboot:10-100uS

-12%

t

CPU_UP

-12%

Vccp_UP

t

t

BOOT

BOOT-VID-TR

t

-12%

t

MCH-PWRGD

t

CPU_PWRGD

PSI#

VID

VR_ON

V

CC-CORE

CCP

CC_MCH

CPU_UP

V

Vccp_UP

V

MCH_PWRGD

CLK_ENABLE#

IMVP6_PWRGD

20060117A - DATA FROM NO.16809

Power On Sequencing Timing Diag ram

SFT_START_VCC

t

t

SFT_START_VCC

Max = 3 ms

t

BOOT

Min = 10 us , Max = 100 us

BOOT-VID-TR

t

Max = 100 us

t

CPU_PWRGD

Min = 3 ms , Max = 20 ms

MCH-PWRGD

t

t

Vccp_UP

CPU_UP

t

Min = 10 us , Max = 30 us

Min = 10 us , Max = 30 us

Min = 10 us , Max = 30 us

Timing Diagram

0.1

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN,ROC

(886-2) 8751-8751

C

549Tuesday, November 18, 2008

Penryn+Candiga GM/PM45+ICH9M(VY050)

Title

Size Document Number Rev

Date: Sheet of

First International Computer,Inc.

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

6.Schematic modify Item and History :

Schematic Modify

0.1

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN,ROC

(886-2) 8751-8751

C

649Tuesday, November 18, 2008

Penryn+Candiga GM/PM45+ICH9M(VY050)

Title

Size Document Number Rev

Date: Sheet of

First International Computer,Inc.

A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

Transmission LineType Total TraceLength Normal Impedance Spacing (mils)

ADS# , BNR# , BPRI# , BR0# , DBSY# , DEFER# , DPWR# , DRDY# , HIT# ,HITM# ,LOCK# ,

RS[2..0]# , TRDY# ,RESET#.

Strip-line(Int. Layer)

Micro-strip(Ext. Layer) 1.0 ~ 6.5 inch 55+/-15% 5 & 10 mils

FSB Common Clock Signal Layout Guide :

Normal Impedance

0.5 ~ 5.5 inch

Width & Spacing (mils)

55+/-15%

4 & 8 mils

DATA#[63..0]

FSB Source Synchronous Data Signal Routing Topology#1 :

Signal Name

Strip-line

Total TraceLength

Signals Name

DSTBP0#,DSTBN0#

Strobes associated with thegroup Strobe-to-StrobeComplement Matching

DATA#[15..0] , DINV0#

Signals Matching

+/- 25 mils+/- 100 mils

DATA#[31..16] , DINV1# +/- 100 mils

+/- 100 mils

+/- 100 mils

+/- 25 mils

+/- 25 mils

+/- 25 mils

DATA#[47..32] , DINV2#

DATA#[63..48] , DINV3#

DSTBP1#,DSTBN1#

DSTBP2#,DSTBN2#

DSTBP3#,DSTBN3#

Strobes associated with thegroup

A#[16..3] , REQ#[4..0]

+/- 200 mils

ADSTB0#+/- 200 mils

Strobe to Assoc. Address Signal Matching

ADSTB1#A#[31..17]

+/- 200 mils

ADSTB#[1..0]

Signals MatchingSignals Name

Topology : PWRGOOD

CPU

L1 0.5" - 12" Strip-line

L1

Micro-strip

Transmission Line

0.5" - 12"

Topology : INTR , NMI , A20M# , DPSLP# , IGNNE# , INIT# , SMI# ,STPCLK#

A#[32-39], APM#[0-1]:Leave escape routing on for future functionality

Zo=55ohm, 0.5" max for GTLREF, Space any other switch

signals away from GTLREF with a minimum of 25mils.

Should be connect to ICH8M and Crestline without T-ing(no stub)

Rout to TP via and place gnd via w/in 100mils

Comp0,2 connect with Zo=27.4ohm, make trace

length shorter than 0.5" and width is 18mils.

Comp1,3 connect with Zo=55ohm, make trace

length shorter than 0.5" and width is 5mils

XDP P/U & P/D

DINV#[3..0]

DSTBN#[3..0]

DSTBP#[3..0]

Transmission LineType

Strip-line

Strip-line

Strip-line

0.5 ~ 5.5 inch

0.5 ~ 5.5 inch

0.5 ~ 5.5 inch

55+/-15%

55+/-15%

55+/-15%

Data-to-Data,Strobe-to-strobe Strobe-to-Data

4 & 8 mils

4 & 8 mils

4 & 12 mils

4 & 12 mils

4 & 12 mils

4 & 12 mils

N/A

N/A

FSB Source Synchronous Data Length Variation and Strobe Matching Requirements :

FSB Source Synchronous Address Length Variation and Strobe Matching Requirements :

+/- 200 mils

*** No length matching requirements exist between ADSTB0# and ADSTB1#

55+/-15%Strip-line

55+/-15%

4 & 8 mils

FSB Source Synchronous Address Signal Routing :

Transmission LineType

4 & 8 mils

Signal Name

Strip-line

Total TraceLength Normal Impedance

0.5 ~ 6.5 inch

Width & Spacing (mils)

55+/-15%

Strip-line

Address#[31..3]

REQ#[4..0]

4 & 8 mils

0.5 ~ 6.5 inch

0.5 ~ 6.5 inch

0" - 3.0" Microstrip0.5" - 12"

L2

56 +/-5%

Rtt

Topology : FERR#

Stripline

VCCP L1

0.5" - 12"L1

ICH8MCPU Rtt Transmission Line

0" - 3.0"

56 +/-5%

L2

ICH8M

Strip-line

L1 0.5" - 12"

Transmission Line

0.5" - 12" Micro-strip

L1CPU ICH8M

L4

VCCP

Rtt CPU IMVP6

VCCP

Rtt

L2+L1 L3 Strip-line

Rtt Transmission LineL2L1

Micro-strip75 +/-5%0.5" - 6.5"

75 +/-5%0.5" - 6.5"

0.5" - 6.5"

0.5" - 6.5"

0" - 3.0"

0" - 3.0"

0" - 3.0"

0" - 3.0"

L3 L4

Rtt

VCCP

Topology : THERMTRIP#

GMCH

L2

CPU ICH7m

RttL1 L4

L3

Rtt

56 +/-5%

L1 L2

1" - 6" 0" - 3.0"

Strip-line0" - 3.0"

0" - 3.0"

Transmission LineL4

Micro-strip

L3

0" - 3.0"

1" - 12"

1" - 12" 1" - 6"

L1+L3

1" - 12"

1" - 12"

Rss

24 +/-5%

24 +/-5% 56 +/-5%

Micro-strip

Strip-line

L1

Strip-line

Transmission LineCPU

Topology : CPUSLP#

0.5" - 12"

1" - 6"

Transmission Line

0.5" - 12"

Topology : RESET#

Micro-strip

L1CPU

L1

L1

GMCH

GMCH

1" - 6"

Don't allow the GTLREF routing to create splits or

discontinuities in the reference planes of the FSB

signals

H_PWRGD rise time :

Max : 15ns

Processor ITP Signal Default Strapping When ITP-XDP &

ITP700FLEX Dedbug Port Not Used.

TDI

TMS

TRST#

TCK

TDO

54.9 OHM +/-5%

OPEN

VCCP

VCCP

GND

GND

NC

Within 2.0" of theCPU

Within 2.0" of theCPU

Within 2.0" of theCPU

Within 2.0" of theCPU

N/A

Signal Resistor Value Connect To Resistor Placement

54.9 OHM +/-5%

649 OHM +/-5%

54.9 OHM +/-5%

Place C181 close tothe CPU_TEST4 pin.

Make sure CPU_TEST4 routing is reference toGND

and away from other nossy signale.

VCCP=1.05VDDM

0'' ~ 3''

Confidential

For D.C 2K

For Q.C 1.74K

Don't allow the GTLREF routing to create splits or

discontinuities in the reference planes of the FSB

signals

Zo=55ohm, 0.5" max for GTLREF, Space any other switch

signals away from GTLREF with a minimum of 25mils.

For Q.C CPU

For Q.C CPU

For D.C 56

For Q.C 50

R26,AA1 For D.C 27.4 For Q.C 25.9

U26,Y1 For D.C 54.9 For Q.C 50

For Q.C 51

EMI

EMI

MeromProcessor (1/2)

0.1

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN,ROC

(886-2)8751-8751

C

749Tuesday, November 18, 2008

Penryn+Candiga GM/PM45+ICH9M(VY050)

Title

Size Document Number Rev

Date: Sheet of

First International Computer,Inc.

H_A#[35..3]

XDP_TRST#

XDP_DBRESET#

H_D#32

H_D#33

H_D#34

H_D#36

H_D#35

H_D#38

H_D#40

H_D#39

H_D#37

H_D#46

H_D#42

H_D#44

H_D#47

H_D#43

H_D#45

H_D#41

H_D#57

H_D#53

H_D#49

H_D#56

H_D#51

H_D#63

H_D#54

H_D#50

H_D#52

H_D#61

H_D#62

H_D#58

H_D#55

H_D#59

H_D#48

H_D#60

H_D#23

H_D#31

H_D#1

H_D#10

H_D#13

H_D#21

H_D#22

H_D#[63..0]

H_D#18

H_D#30

H_D#4

H_D#19

H_D#26

H_D#27

H_D#0

H_D#5

H_D#[63..0]

H_D#7

H_D#11

H_D#14

H_D#15

H_D#17

H_D#8

H_D#25

H_D#2

H_D#24

H_D#28

H_D#6

H_D#9

H_D#12

H_D#20

H_D#[63..0]

H_D#3

H_D#16

H_D#29

H_D#[63..0]

COMP2

XDP_TCK

XDP_TDI

XDP_TMS

XDP_BPM#5

H_GTLREF COMP1

COMP3

1.05VDDM

TEST3

TEST5

COMP0

H_REQ#3

H_A#9

H_A#5

H_A#25

XDP_TMS

XDP_DBRESET#

H_A#8

H_A#6

H_A#19

H_A#14

H_A#12

H_A#11

H_A#35

H_REQ#2

H_A#20

H_A#4

H_A#30

H_A#27

H_A#18

H_A#13

H_A#10

H_A#34

H_REQ#4

H_REQ#1

XDP_BPM#5

H_A#17

H_A#16

XDP_TRST#

XDP_TDIH_A#26 XDP_TCK

H_REQ#0

H_A#33

H_A#32

H_A#7

H_A#31

H_A#3

H_A#24

H_A#23

H_A#22

H_IERR#

H_A#28

H_A#21

H_A#[35..3]

H_A#29

H_A#15

H_REQ#[4..0]

3VDDM

H_QCBPM2

H_QCBPM0

H_QCBPM1

H_BPM1

H_BPM3

H_BPM2

H_BPM0

H_GTLREF2

TDO_M

TDI_M

3VDDM(9,11,14,16,17,18,19,20,21,22,23,24,25,26,29,30,31,32,33,35,37,43,45,46,47)

1.05VDDM(8,10,11,13,14,18,20,22,45)

H_A#[35..3](10)

H_A#[35..3](10)

H_ADSTB#0(10)

H_ADSTB#1(10)

H_REQ#[4..0](10)

H_D#[63..0](10)

H_D#[63..0](10)

H_DSTBN#0(10) H_DSTBP#0(10) H_DINV#0(10)

H_DSTBN#1(10)

H_DINV#1(10) H_DSTBP#1(10)

H_D#[63..0] (10)

H_D#[63..0] (10)

H_DSTBN#2 (10)

H_DINV#2 (10)

H_DSTBP#2 (10)

H_DSTBN#3 (10)

H_DINV#3 (10)

H_DSTBP#3 (10)

H_BNR# (10)

H_DBSY# (10)

H_LOCK# (10)

H_DRDY# (10)

H_HITM# (10)

H_HIT# (10)

H_ADS# (10)

H_BREQ# (10)

H_PROCHOT# (47)

H_A20M#(20)

H_IGNNE#(20)

H_STPCLK#(20) H_INTR(20) H_NMI(20) H_SMI#(20)

H_CPUSLP# (10) H_PWRGD (20)

H_DPWR# (10)

H_DPRSTP# (11,20,47)

H_DPSLP# (20)

H_CPURST# (10)

H_RS#2 (10)

H_RS#1 (10)

H_INIT# (20)

H_RS#0 (10)

H_BPRI# (10)

H_TRDY# (10)

H_DEFER# (10)

CLK_CPU_BCLK (18)

CLK_CPU_BCLK# (18)

H_THERMDA (9)

H_FERR#(20)

CPU_BSEL0(18) CPU_BSEL1(18) PSI# (47)CPU_BSEL2(18)

PM_THRMTRIP# (11,20)

H_THERMDC (9) HOT_DOWN# (9,37)

H_QCTHERMDA(9) H_QCTHERMDC(9)

1.05VDDM

1.05VDDM

1.05VDDM

1.05VDDM

3VDDM

1.05VDDM

1.05VDDM

1.05VDDM

1.05VDDM

C167

1000pF 25V+80-20%SMT0603 Y5V LR(NU)

R228 54.9 1%1/16W SMT0402 LR Sn

R290 1K 1%1/16W SMT0402 LR

R278

1.74K 1%1/10W SMT0603 LR(NU)

R213 51 5%1/16W SMT0402 LR(NU)

R286 0 5%1/16W SMT0402 LR(NU)

R218 54.9 1%1/16W SMT0402 LR Sn

C172

1000pF 25V+80-20%SMT0603 Y5V LR(NU)

R214 51 5%1/16W SMT0402 LR(NU)

R287

68 5%1/16W SMT0402 TIN LR

R566

100 1%1/16W SMT0402 LR(NU)

R24151 5%1/16W SMT0402 LR(NU)

R285 54.9 1%1/16W SMT0402 LR Sn

R234

51 5%1/16W SMT0402 LR(NU)

R294 1K 5%1/16W SMT0402 LR(NU)

R217 54.9 1%1/16W SMT0402 LR Sn

R215 51 5%1/16W SMT0402 LR(NU)

R24551 5%1/16W SMT0402 LR(NU)

R289 1K 5%1/16W SMT0402 LR(NU)

R275 1K 5%1/16W SMT0402 LR(NU)

R291 27.4 1%SMT0402 LR

R280 1K 1%1/16W SMT0402 LR(NU)

R222 54.9 1%1/16W SMT0402 LR Sn

R219 54.9 1%1/16W SMT0402 LR Sn

R22751 5%1/16W SMT0402 LR(NU)

R233 54.9 1%1/16W SMT0402 LR Sn

RP17

05%SMT1010 1/16W 4P2R LR(NU)

1

24

3

ADDR GROUP

0ADDR GROUP

1

CONTROL

XDP/ITP SIGNALS

H CLK

THERMAL

RESERVED

ICH

U30A

Penryn Ball-out Rev 1a

N3

P5

P2

L2

P4

P1

R1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

J4

U2

V4

M4

N5

T2

V3

B2

C3

D2

D22

L5

L4

K5

M3

N2

J1

A6

H1

M1

V1

D3

A22

A21

E2

AD4

AD3

AD1

AC4

G5

F1

C20

E1

H5

F21

A5

G6

E4

D20

C4

B3

C6

B4

H4

AC2

AC1

D21

K3

H2

K2

J3

L1

C1

F3

F4

G3

A3

D5

AC5

AA6

AB3

C7

A24

B25

AB5

G2

AB6

W3

AA4

AB2

AA3

F6

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[3]#

A[30]#

A[31]#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

RSVD[08]

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A20M#

ADS#

ADSTB[0]#

ADSTB[1]#

RSVD[09]

BCLK[0]

BCLK[1]

BNR#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

BPRI#

BR0#

DBR#

DBSY#

DEFER#

DRDY#

FERR#

HIT#

HITM#

IERR#

IGNNE#

INIT#

LINT0

LINT1

LOCK#

PRDY#

PREQ#

PROCHOT#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

RESET#

RS[0]#

RS[1]#

RS[2]#

SMI#

STPCLK#

TCK

TDI

TDO

THERMTRIP#

THERMDA

THERMDC

TMS

TRDY#

TRST#

A[32]#

A[33]#

A[34]#

A[35]#

RSVD[10]

C242

0.1uF 10V10%0402 X5R LR(NU)

R221 27.4 1%SMT0402 LR

R288 56 5%1/16W SMT0402 LR

R284

2K 1%1/16W SMT0402 LR

12

DATA GRP 0 DATA GRP 1

DATA GRP 2DATA GRP 3

MISC

U30B

Penryn Ball-out Rev 1a

R26

U26

AA1

Y1

E22

F24

J24

J23

H22

F26

K22

H23

N22

K25

P26

R23

E26

L23

M24

L22

M23

P25

P23

P22

T24

R24

L25

G22

T25

N25

Y22

AB24

V24

V26

V23

T22

U25

U23

F23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

AE24

AD24

G25

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

E25

AC22

AD23

AF22

AC23

E23

K24

G24

AF1

H25

N24

U22

AC20

E5

B5

D24

J26

L26

Y26

AE25

H26

M26

AA26

AF24

AD26

AE6

D6

D7

C24

B22

B23

C21

D25

AF26

A26

C23 COMP[0]

COMP[1]

COMP[2]

COMP[3]

D[0]#

D[1]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

D[16]#

D[17]#

D[18]#

D[19]#

D[2]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[3]#

D[30]#

D[31]#

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[4]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

D[48]#

D[49]#

D[5]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[6]#

D[60]#

D[61]#

D[62]#

D[63]#

D[7]#

D[8]#

D[9]#

TEST5

DINV[0]#

DINV[1]#

DINV[2]#

DINV[3]#

DPRSTP#

DPSLP#

DPWR#

DSTBN[0]#

DSTBN[1]#

DSTBN[2]#

DSTBN[3]#

DSTBP[0]#

DSTBP[1]#

DSTBP[2]#

DSTBP[3]#

GTLREF

PSI#

PWRGOOD

SLP#

TEST3

BSEL[0]

BSEL[1]

BSEL[2]

TEST2

TEST4

TEST6

TEST1

R216 51 5%1/16W SMT0402 LR(NU)

A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

Place theseinside socket cavity on L8

(North side secondary)

Place C?

Close To pin

B26

Route VCCSENSE and VSSSENSE traces

at 27.4 ohms with 50milspacing.

Place PU and PD within 1 inch of CPU

ICCA=130mA, 20mils

HFM

ICC=41A

ICCP=4.5A,180mils

TDK

Place theseinside socket cavity on L1

(South sidePrimary)

Place theseinside socket cavity on L8

(North side secondary)

Place theseinside socket cavity on L1

(North side Primary)

Place these inside socket cavity on

L8 (South side secondary)

South side secondary

North side secondary

Confidential

For Q.C NU

For D.C ON

For D.C

For D.C 0

For Q.C 1.21K

For Q.C ON

Merom Processor (2/2)

0.1

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2)8751-8751

C

8 49Tuesday, November 18, 2008

Penryn+Candiga GM/PM45+ICH9M(VY050)

Title

Size Document Number Rev

Date: Sheet of

FirstInternational Computer, Inc.

1.5VDDM

VCORE_CPU

1.05VDDM

GTREF_CONT

H_QCBPM3

BR1#

1.05VDDM(7,10,11,13,14,18,20,22,45)

1.5VDDM(13,14,19,20,22,29,31,44)

VCORE_CPU(47)

H_VID0 (47)

H_VID1 (47)

H_VID3 (47)

H_VID2 (47)

H_VID5 (47)

H_VID4 (47)

H_VID6 (47)

VCCSENSE (47)

VSSSENSE (47)

1.05VDDM

1.5VDDM

VCORE_CPU

VCORE_CPU

1.5VDDM

R251

05% 1/16WSMT0402 LR

C221 0.1uF 16V ±10% SMD0603 X7R LR

R244

05% 1/16WSMT0402 LR

C519 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

R262

51 5% 1/16WSMT0402 LR(NU)

C213 0.1uF 16V ±10% SMD0603 X7R LR

C189 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C227 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C198 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

R260

05% 1/16WSMT0402 LR

C252 0.1uF 16V ±10% SMD0603 X7R LR

C525 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

R242

05% 1/16WSMT0402 LR

C520 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C513 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C498 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C224 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

U30D

Penryn Ball-out Rev 1a

P6

AE11

A8

A11

A14

A16

A19

A23

AF2

B6

B8

B11

B13

B16

B19

B21

B24

C5

C8

C11

C14

C16

C19

C2

C22

C25

D1

D4

D8

D11

D13

D16

D19

D23

D26

E3

E6

E8

E11

E14

E16

E19

E21

E24

F5

F8

F11

F13

F16

F19

F2

F22

F25

G4

G1

G23

G26

H3

H6

H21

H24

J2

J5

J22

J25

K1

K4

K23

K26

L3

L6

L21

L24

M2

M5

M22

M25

N1

N4

N23

N26

P3 A25

AF21

AF19

AF16

AF13

AF11

AF8

AF6

A2

AE26

AE23

AE19

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

Y6

A4

AE14

AE16

AE8

AF25

VSS[082]

VSS[148]

VSS[002]

VSS[003]

VSS[004]

VSS[005]

VSS[006]

VSS[007]

VSS[008]

VSS[009]

VSS[010]

VSS[011]

VSS[012]

VSS[013]

VSS[014]

VSS[015]

VSS[016]

VSS[017]

VSS[018]

VSS[019]

VSS[020]

VSS[021]

VSS[022]

VSS[023]

VSS[024]

VSS[025]

VSS[026]

VSS[027]

VSS[028]

VSS[029]

VSS[030]

VSS[031]

VSS[032]

VSS[033]

VSS[034]

VSS[035]

VSS[036]

VSS[037]

VSS[038]

VSS[039]

VSS[040]

VSS[041]

VSS[042]

VSS[043]

VSS[044]

VSS[045]

VSS[046]

VSS[047]

VSS[048]

VSS[049]

VSS[050]

VSS[051]

VSS[052]

VSS[053]

VSS[054]

VSS[055]

VSS[056]

VSS[057]

VSS[058]

VSS[059]

VSS[060]

VSS[061]

VSS[062]

VSS[063]

VSS[064]

VSS[065]

VSS[066]

VSS[067]

VSS[068]

VSS[069]

VSS[070]

VSS[071]

VSS[072]

VSS[073]

VSS[074]

VSS[075]

VSS[076]

VSS[077]

VSS[078]

VSS[079]

VSS[080]

VSS[081] VSS[162]

VSS[161]

VSS[160]

VSS[159]

VSS[158]

VSS[157]

VSS[156]

VSS[155]

VSS[154]

VSS[153]

VSS[152]

VSS[151]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[106]

VSS[001]

VSS[149]

VSS[150]

VSS[147]

VSS[163]

C514 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C180 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

R253

05% 1/16WSMT0402 LR

C225 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C511 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

R255

05% 1/16WSMT0402 LR

U30C

Penryn Ball-out Rev 1a

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C10

C12

C13

C15

C17

C18

D9

D10

D12

D14

D15

D17

D18

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

B26

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

AF7

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AE7

C26

G21

V6

VCC[001]

VCC[002]

VCC[003]

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[034]

VCC[035]

VCC[036]

VCC[037]

VCC[038]

VCC[039]

VCC[040]

VCC[041]

VCC[042]

VCC[043]

VCC[044]

VCC[045]

VCC[046]

VCC[047]

VCC[048]

VCC[049]

VCC[050]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCC[066]

VCC[067]

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCA[01]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCSENSE

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VSSSENSE

VCCA[02]

VCCP[01]

VCCP[02]

C524 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C201 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C247 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

R246

05% 1/16WSMT0402 LR

C181 0.1uF 16V ±10% SMD0603 X7R LR

C184 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C196 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C179 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C215 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C523 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C503 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C202 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C246

0.01uF 16V 10% SMT0402 X7R LR

C200 0.1uF 16V ±10% SMD0603 X7R LR

C497 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C188 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C209 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C222 0.1uF 16V ±10% SMD0603 X7R LR

C502 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C197 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C510 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

+

C168

T100uF 2V ±20% ESR=18m SMT7343 EEFCD0D101ER PANASONIC LR

R256

100 1% 1/16WSMT0402 LR

R250

100 1% 1/16WSMT0402 LR R252

05% 1/16WSMT0402 LR

C496 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR

C185 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C216 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

C210 10uF 6.3V 10% SMT0805 X5R C2012X5R0J106K TDK LR(NU)

8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Confidential

10mil

10mil

Dual Core THERMAL SENSOR

20mil

10 mil

10 mil

GND

GND

THERMDA

10 mil

THERMDC

Minimum

10 mil

THERMDA

THERMDC

20mil

10 mil

GND

GND

10mil

10 mil

10 mil

10 mil

Quad Core THERMAL SENSOR

10mil

Minimum

Vo VsetVINVEN

30mil

GND

30mil

GNDGNDGND

V02

CPU Thermal

0.1

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN,ROC

(886-2)8751-8751

C

949Tuesday, November 18, 2008

Penryn+Candiga GM/PM45+ICH9M(VY050)

Title

Size Document Number Rev

Date: Sheet of

First International Computer,Inc.

5VDDM

3VDDA

3VDDM

SMCLK_PMU

HOT_DOWN#

THRM_VCC

SMDAT_PMU

TH_ALRT#

THRM_VCC

TH_ALRT#

HOT_DOWN#

SMDAT_PMU

H_QCTHERMDC

H_QCTHERMDA

SMCLK_PMU

3VDDA(18,19,20,21,22,23,24,26,28,29,31,32,33,37,41,43,44,45)

5VDDM(22,25,27,30,35,36,43,44,46,47)

3VDDM(7,11,14,16,17,18,19,20,21,22,23,24,25,26,29,30,31,32,33,35,37,43,45,46,47)

H_THERMDA (7)

HOT_DOWN# (7,37)

H_THERMDC (7)

SMDAT_PMU(37,41)

SMCLK_PMU(37,41)

H_QCTHERMDC (7)

H_QCTHERMDA (7)

FAN_PWM(37)

FAN_SPEED(37)

5VDDM

3VDDA

3VDDM

5VDDM

5VDDM

U15

LNR-IC Temperature Sensor G780-1P81U 3.0-5.5V MSOP-8 8PIN GMT LR(nu)

1

2

3

45

6

7

8VCC

D+

D-

THM#GND

ALRT#

SDATA

SCLK

C164

2200pF 50V10%SMT0402 X7R LR

R504

10K 5%1/16WSMT0402 LR

C674

2.2uF 10V±10%SMT0603X5R C1608X5R1A225KT TDKLR C675

2.2uF 10V±10%SMT0603X5R C1608X5R1A225KT TDKLR

R211

10K 5%1/16WSMT0402 LR

R203

100 5%1/16W SMT0402 LR(NU)

C166

2200pF 50V10%SMT0402 X7R LR(NU)

U39

LNR-IC FAN DRIVER 1.6XG990P11USOP-8 GMT LR

1

2

3

45

6

7

8VEN

VIN

VO

VSETGND

GND

GND

GND

C162

0.1uF 16V80-20%SMT0402Y5V LR(NU)

R202

100 5%1/16W SMT0402 LR

U14

LNR-IC Temperature Sensor G780P81U 3.0-5.5V MSOP-8 8PIN GMT LR

1

2

3

45

6

7

8VCC

D+

D-

THM#GND

ALRT#

SDATA

SCLK

C460

0.22uF 10V10%0603 X7R

12

R212

10K 5%1/16WSMT0402 LR

CN27

CON ACES SMT TYPE 85205-03001 WIRE1.25P3PIN LR DO'NT CARE

20-24197-20

1

2

3

4

5

C158

0.1uF 16V80-20%0402 Y5VLR

10

10

9

9

8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

H H

G G

F F

E E

D D

C C

B B

A A

Confidential

for D.C 100

for Q.C 75

10 mil wide / 20 mil spacing

for D.C 24.9

for Q.C 16.9

Crestline Host (1/6)

0.1

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2)8751-8751

C

10 49Tuesday, November 18, 2008

Penryn+Candiga GM/PM45+ICH9M(VY050)

Title

Size Document Number Rev

Date: Sheet of

FirstInternational Computer, Inc.

H_A#15

H_A#5

H_A#11

H_A#9

H_A#13

H_A#14

H_A#6

H_A#12

H_A#16

H_A#8

H_A#10

H_A#3

H_A#4

H_A#7

H_A#23

H_A#26

H_A#21

H_A#30

H_A#25

H_A#28

H_A#29

H_A#20

H_A#31

H_A#24

H_A#18

H_A#17

H_A#27

H_A#19

H_A#22

H_A#[35..3]

H_REQ#0

H_REQ#2

H_REQ#4

H_REQ#3

H_REQ#1

H_REQ#[4..0]

H_SWING

H_RCOMP

H_SWING

H_RCOMP

H_AVREF

H_DVREF

H_A#32

H_A#33

H_A#34

H_A#35

1.05VDDM

H_D#17

H_D#46

H_D#14

H_D#42

H_D#61

H_D#44

H_D#18

H_D#53

H_D#43

H_D#41

H_D#62

H_D#27

H_D#28

H_D#8

H_D#31

H_D#34

H_D#19

H_D#47

H_D#45

H_D#55

H_D#[63..0]

H_D#48

H_D#22

H_D#38

H_D#32

H_D#12

H_D#56

H_D#13

H_D#37

H_D#25

H_D#3

H_D#1

H_D#54

H_D#29

H_D#9

H_D#33

H_D#24

H_D#57

H_D#59

H_D#49

H_D#40

H_D#2

H_D#21

H_D#0

H_D#52

H_D#60

H_D#6

H_D#16

H_D#15

H_D#39

H_D#26

H_D#30

H_D#10

H_D#35

H_D#50

H_D#11

H_D#4

H_D#5

H_D#36

H_D#51

H_D#58

H_D#7

H_D#63

H_D#20

H_D#23

1.05VDDM(7,8,11,13,14,18,20,22,45)

H_ADSTB#0 (7)

H_DINV#3 (7)

H_DSTBP#1 (7)

H_BREQ# (7)

H_D#[63..0](7)

H_HITM# (7)

H_DSTBN#3 (7)

H_DINV#1 (7)

H_DBSY# (7)

H_DSTBP#2 (7)

H_HIT# (7)

H_DSTBN#1 (7)

H_DRDY# (7)

H_DINV#2 (7)

H_DINV#0 (7)

H_DSTBN#2 (7)

H_REQ#[4..0] (7)

H_DSTBP#0 (7)

H_DSTBN#0 (7)

H_ADS# (7)

H_ADSTB#1 (7)

H_A#[35..3] (7)

H_BNR# (7)

H_DSTBP#3 (7)

H_DPWR# (7)

CLK_MCH_BCLK (18)

CLK_MCH_BCLK# (18)

H_LOCK# (7)

H_BPRI# (7)

H_CPURST#(7)

H_DEFER# (7)

H_RS#0 (7)

H_RS#1 (7)

H_RS#2 (7)

H_CPUSLP#(7)

H_TRDY# (7)

1.05VDDM

1.05VDDM

R558

RES 24.9 1% 1/16WSMT0402 LR

HOST

U31A

CANTIGA_1p0

P16

R16

N17

M13

E17

P17

F17

G20

B19

J16

E20

H16

J20

L17

A17

B17

L16

C21

J17

H20

A14

B18

K17

C15

F16

H13

C18

M16

J13

H12

B16

G17

A9

F11

G12

AH6

C12

AH7

F2

F13

B13

G8

M9

L6

N10

AA8

AA2

AE11

D4

H3

B10

M11

J1

J2

N12

J6

P2

L2

R2

N9

F8

M5

J3

N2

R1

N5

N6

P13

N8

L7

E6

M3

Y3

AD14

Y6

Y10

Y12

Y14

Y7

W2

G2

Y9

AA13

AA9

AA11

AD11

AD10

AD13

AE12

AE9

H6

AD8

AA3

AD3

AD7

AE14

AF3

AC1

AE3

AC3

H2

AE8

AG2

AD6

F6

E9

J8

L3

Y13

Y1

J11

F9

L10

M7

AA5

AE6

L9

M8

AA6

AE5

A11

B11

C9

H9

E12

H11

B15

K13

B14

B20

F21

K21

L20

C5

E11

E3

B6

F12

C8

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_3

H_A#_30

H_A#_31

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

HPLL_CLK#

H_CPURST#

HPLL_CLK

H_D#_0

H_REQ#_2

H_REQ#_3

H_D#_1

H_D#_10

H_D#_20

H_D#_30

H_D#_40

H_D#_50

H_D#_60

H_D#_8

H_D#_9

H_DBSY#

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_2

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_3

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_4

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_5

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_6

H_D#_61

H_D#_62

H_D#_63

H_D#_7

H_DEFER#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DPWR#

H_DRDY#

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_AVREF

H_DVREF

H_TRDY#

H_HIT#

H_HITM#

H_LOCK#

H_REQ#_0

H_REQ#_1

H_REQ#_4

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_SWING

H_CPUSLP#

H_RCOMP

H_RS#_0

H_RS#_1

H_RS#_2

R553

SPWR 0 5% 1/16W0402

R551

RES 221 1% 1/16WSMT0402 RR0510S-2210-FN CYNTEC LR

C490

0.1uF 10V10% 0402 X5R LR(NU)

R552

100 1% 1/16WSMT0402 LR

R550

1K 1% 1/16WSMT0402 LR

C486

0.1uF 10V10% 0402 X5R LR

R549

2K 1% 1/16WSMT0402 LR

12

C177

0.1uF 10V10% 0402 X5R LR(NU)

10

10

9

9

8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

H H

G G

F F

E E

D D

C C

B B

A A

20miles

0 = Dynamic ODT Disabled

1 = DMI * 4 ( Default )

CFG19

CFG [12:13]

CFG [2:0]

1 = SDVO or PCIE X1 are operatingsimulaneously via the PEG port.

00 = Clock Gating Disable

000=FSB1066

11 = Normal Operation ( Default )

CFG20

CFG5

0 = Only SDVO or PCIE X1 is operationl ( default )

010=FSB800

CFG9

10 = All Z Mode Enable

CFG16

01 = XOR Mode Enabled

0 = DMI * 2

GMCH Strapping Requirements

0 = Lane Reverse 1 = DMI Lane Reversal Enabled ( Default )

1 = Normal Operation ( Default )

Confidential

(DMI lane)

0 = Normal ( Default )

1 = Lanes Reversed

(PCIE)

0.35V

011=FSB667

CFG6 0 = ITPM is enabled

1 = ITPM is disabled ( Default )

CFG7

CFG10

0 = Isolators are bypassed

1= Isolators are active (Default)

1= PCIE loopback disable(Default)

0 = PCIE loopback enable

For checklist v1.2

For checklist v1.2

Install it if GMCH

disable.

Crestline DMI/Graphic (2/6)

0.1

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2)8751-8751

C

11 49Tuesday, November 18, 2008

Penryn+Candiga GM/PM45+ICH9M(VY050)

Title

Size Document Number Rev

Date: Sheet of

FirstInternational Computer, Inc.

PM_EXTTS#0

MCH_CFG_19

PM_EXTTS#1

SM_RCOMP_VOH

MCH_CFG_16

RST_IN#_MCH

MCH_CFG_13

SM_RCOMP_VOL

MCH_CFG_9

MCH_CFG_12

SM_RCOMP_VOH

SM_RCOMP_VOL

MCH_CFG_5

MCH_CFG_20

CLK_MCH_OE#

PEG_COMP

MCH_CFG_19

SM_RCOMP#

SM_RCOMP

3VDDM

1.8VDDS

M_VREF

TV_DCONSEL1

TV_DCONSEL0

DMI_TXP3

DMI_TXP2

DMI_TXP1

DMI_TXP0

DMI_TXN3

DMI_TXN1

DMI_TXN0

DMI_RXP1

DMI_RXP2

DMI_RXP0

DMI_RXP3

DMI_RXN3

DMI_RXN2

DMI_RXN1

DMI_RXN0

CLK_MCH_OE#

1.05VDDM_PEG

DFGT_VID_2

DFGT_VID_3

DFGT_VID_0

DFGT_VID_1

SM_DRAMRST#

DMI_TXN2

CL_REFCL_REF

DFGT_VID_4

1.05VDDM

MCH_CFG_6

SDVO_CTRL_DATA

SDVO_CTRL_CLK

TV_DCONSEL1

TV_DCONSEL0

MCH_CFG_20

PM_EXTTS#0

PM_EXTTS#1

MCH_CFG_12

TV_DCONSEL1

MCH_CFG_6

MCH_CFG_20

TV_DCONSEL0

MCH_CFG_16

MCH_CFG_9

MCH_CFG_5

MCH_CFG_13

1.8VDDS(13,14,16,17,45)

3VDDM(7,9,14,16,17,18,19,20,21,22,23,24,25,26,29,30,31,32,33,35,37,43,45,46,47)

M_VREF(16,17,45)

1.05VDDM_PEG(14)

1.05VDDM(7,8,10,13,14,18,20,22,45)

LVDS_DDC_CLKU(24)LVDS_DDC_DATAU(24)

LVDS_TXOUT_L1PU(24)

LVDS_TXOUT_L1NU(24)

LVDS_TXOUT_L0PU(24)

LVDS_TXCLK_LPU(24)

LVDS_TXOUT_L2PU(24)

LVDS_TXOUT_L0NU(24)

LVDS_TXOUT_L2NU(24)

LVDS_TXCLK_LNU(24)

Q_VEDATU(25) Q_VECLKU(25)

MCH_BSEL0(18)

MCH_BSEL2(18)

CL_DATA0 (21)

CL_CLK0 (21)

CL_RST#0 (21)

MCH_BSEL1(18)

DREFSSCLK# (18)

DREFSSCLK (18)

DREFCLK (18)

DREFCLK# (18)

H_DPRSTP#(7,20,47)

CLK_PCIE_3GPLL (18)

PM_DPRSLPVR(21,46,47)

PLT_RST#(19)

CLK_PCIE_3GPLL# (18)

PM_EXTTS#1(17)

DELAY_VR_PWRGOOD(23,47)

PM_EXTTS#0(16)

MPWROK (21,23,37)

DMI_TXP1 (19)

DMI_TXP2 (19)

DMI_TXP0 (19)

DMI_TXP3 (19)

DMI_TXN1 (19)

DMI_TXN3 (19)

DMI_TXN2 (19)

DMI_TXN0 (19)

SM_PWROK

LCD_BRIGHTNESS(24,37) LVDS_ENABKL(37)

LVDS_ENALCDU(24)

TV_YU

TV_CU

REDU(25)

BLUEU(25)

GREENU(25)

HSYNCU(25) VSYNCU(25)

M_CLK_DDR#1 (16)

M_CLK_DDR#0 (16)

M_CS#1 (16)

M_CS#3 (17)

M_CLK_DDR#4 (17)

M_ODT2 (17)

M_ODT0 (16)

M_CS#2 (17)

M_CLK_DDR#3 (17)

M_CKE3 (17)

M_ODT3 (17)

M_ODT1 (16)

M_CKE4 (17)

M_CLK_DDR1 (16)

MCH_ICH_SYNC# (21)

M_CS#0 (16)

M_CLK_DDR4 (17)

CLK_MCH_OE# (18)

PM_BMBUSY#(21)

M_CKE0 (16)

M_CKE1 (16)

M_CLK_DDR3 (17)

M_CLK_DDR0 (16)

PM_THRMTRIP#(7,20)

DMI_RXP3 (19)

DMI_RXP0 (19)

DMI_RXP2 (19)

DMI_RXP1 (19)

DMI_RXN2 (19)

DMI_RXN0 (19)

DMI_RXN3 (19)

DMI_RXN1 (19)

DFGT_VID_3 (46)

DFGT_VID_2 (46)

DFGT_VID_0 (46)

DFGT_VID_1 (46)

DFGT_VR_EN (46)

DFGT_VID_4 (46)

MCH_TSATN

1.8VDDS

1.05VDDM

3VDDM

3VDDM

1.05VDDM_PEG

1.8VDDS

1.05VDDM

3VDDM

1.8VDDS

M_VREF

R226 10K 5% 1/16WSMT0402 LR

R248

1K 1% 1/16WSMT0402 LR

T11

1

RP57

RP2.2K 5% SMT1010 4P2R 1/16WLR(NU)

R265 75 1% 1/16WSMT0402 LR

R266 0 5% 1/16WSMT0402 LR(NU)

RP40

10K 5% SMT1010 1/16W4P2R LR

1

24

3

R300

1K 1% 1/16WSMT0402 LR

R270 RES 2.2K 1% 1/16WSMT0402 LR

R271

RES 49.9 1% 1/16WSMT0402

R259 75 1% 1/16WSMT0402 LR

RP58

05% SMT1010 1/16W4P2R LR

1

24

3

R283 10K 1% 1/16WSMT0402 LR(NU)

R298 0 5% 1/16WSMT0402 LR

R296

3.01K 1% 1/10W0603 LR

R279

1K 1% 1/16WSMT0402 LR

C228

0.1uF 10V10% 0402 X5R LR

T13 1

R263 RES 150 1% 1/16WSMT0402 LR

R543

10K 5% 1/16WSMT0402 LR

R235 RES 2.2K 1% 1/16WSMT0402 LR(NU)

R247 RES 150 1% 1/16WSMT0402 LR

R236 RES 2.2K 1% 1/16WSMT0402 LR(NU)

R243 0 5% 1/16WSMT0402 LR

PM

MISC

NC

DDR CLK/ CONTROL/COMPENSATIONCLK

DMI

CFG

RSVD

GRAPHICS VIDMEHDA

U31B

CANTIGA_1p0

AP24

AT21

AV24

AR24

AR21

AU24

BC28

AY28

AY36

BB36

BA17

AY16

AV16

AR13

BC36

BD17

AY17

BF15

AY13

BG22

BH21

P29

R28

P25

T25

R25

T28

P20

P24

C25

N24

M24

E21

C23

C24

N21

P21

T21

R20

M20

L21

H21

R29

N33

P32

AT40

AT11

B38

A38

E41

F41

AE41

AE37

AE47

AH39

AE40

AE38

AE48

AH40

AE35

AE43

AE46

AH42

AD35

AE44

AF46

AH43

AL34

AN35

AK34

AM35

BG23

BF23

BH18

BF18

B7

AU20

AV20

AY21

AH9

AH10

AH12

AH13

M36

N36

R33

T33

B33

B32

G33

F33

C34

BF28

BH28

T20

R32

K12

AH37

AH36

AN36

AJ35

AH34

A47

BG48

BF48

BD48

BC48

BH47

BG47

BE47

BH46

BF46

BG45

BH44

BH43

BH6

BH5

BG4

G36

E36

K36

T24

H36

B12

E43

F43

BH3

E33

B31

N28

BF3

BH2

BG2

BE2

BG1

BF1

BD1

BC1

F1

AV42

AR36

BF17

M1

B28

B30

B29

C29

A28

M28

B2

SA_CK_0

SA_CK_1

SB_CK_0

SA_CK#_0

SA_CK#_1

SB_CK#_0

SA_CKE_0

SA_CKE_1

SB_CKE_0

SB_CKE_1

SA_CS#_0

SA_CS#_1

SB_CS#_0

SB_CS#_1

SM_DRAMRST#

SA_ODT_0

SA_ODT_1

SB_ODT_0

SB_ODT_1

SM_RCOMP

SM_RCOMP#

CFG_18

CFG_19

CFG_2

CFG_0

CFG_1

CFG_20

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

PM_SYNC#

PM_EXT_TS#_0

PM_EXT_TS#_1

PWROK

RSTIN#

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

RSVD10

RSVD12

RSVD11

RSVD13

RSVD22

RSVD23

RSVD24

RSVD25

PM_DPRSTP#

SB_CK_1

SB_CK#_1

RSVD20

RSVD5

RSVD6

RSVD7

RSVD8

RSVD1

RSVD2

RSVD3

RSVD4

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VR_EN

SM_RCOMP_VOH

SM_RCOMP_VOL

THERMTRIP#

DPRSLPVR

RSVD9

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

NC_26

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

NC_10

NC_11

NC_12

NC_13

NC_14

NC_15

SDVO_CTRLCLK

SDVO_CTRLDATA

CLKREQ#

RSVD14

ICH_SYNC#

TSATN#

PEG_CLK#

PEG_CLK

NC_16

GFX_VID_4

RSVD15

DDPC_CTRLCLK

NC_17

NC_18

NC_19

NC_20

NC_21

NC_22

NC_23

NC_24

NC_25

SM_VREF

SM_PWROK

SM_REXT

RSVD17

HDA_BCLK

HDA_RST#

HDA_SDI

HDA_SDO

HDA_SYNC

DDPC_CTRLDATA

RSVD16

R230 RES 2.2K 1% 1/16WSMT0402 LR(NU)

R299 10K 1% 1/16WSMT0402 LR(NU)

R257 RES 150 1% 1/16WSMT0402 LR

C255

2.2uF 6.3V 80-20% SMT0603 Y5V LR

LVDS

PCI-EXPRESS GRAPHICS

TV VGA

U31C

CANTIGA_1p0

T37

T36

H44

J46

L44

L40

N41

P48

N44

T43

U43

Y43

Y48

Y36

AA43

AD37

AC47

AD39

H43

J44

L43

L41

N40

P47

N43

T42

U42

Y42

W47

Y37

AA42

AD36

AC48

AD40

J41

Y40

M40

M42

R48

N38

T40

U37

U40

M46

AA46

AA37

AA40

AD43

AC46

M47

J42

L46

M48

M39

M43

R47

N37

T39

U36

U39

Y39

Y46

AA36

AA39

AD42

AD46

M32

M33

K33

J33

M29

C44

B43

E37

E38

C41

C40

H47

E46

G40

D45

F40

B37

A37

A41

H38

G37

G38

F37

G32

F25

H25

K25

H24

E28

H32

J32

G28

J29

E29

J28

G29

L29

H48

B42

L32

C31

E32

A40

B40

J37

K37

PEG_COMPI

PEG_COMPO

PEG_RX#_0

PEG_RX#_1

PEG_RX#_2

PEG_RX#_3

PEG_RX#_4

PEG_RX#_5

PEG_RX#_6

PEG_RX#_7

PEG_RX#_8

PEG_RX#_9

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PEG_RX_0

PEG_RX_1

PEG_RX_2

PEG_RX_3

PEG_RX_4

PEG_RX_5

PEG_RX_6

PEG_RX_7

PEG_RX_8

PEG_RX_9

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

PEG_TX#_0

PEG_TX#_10

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX#_1

PEG_TX#_11

PEG_TX#_12

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_TX#_2

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

L_CTRL_CLK

L_CTRL_DATA

L_DDC_CLK

L_DDC_DATA

L_VDD_EN

LVDS_IBG

LVDS_VBG

LVDS_VREFH

LVDS_VREFL

LVDSA_CLK#

LVDSA_CLK

LVDSA_DATA#_0

LVDSA_DATA#_1

LVDSA_DATA#_2

LVDSA_DATA_1

LVDSA_DATA_2

LVDSB_CLK#

LVDSB_CLK

LVDSB_DATA#_0

LVDSB_DATA#_1

LVDSB_DATA#_2

LVDSB_DATA_1

LVDSB_DATA_2

L_BKLT_EN

TVA_DAC

TVB_DAC

TVC_DAC

TV_RTN

CRT_BLUE

CRT_DDC_CLK

CRT_DDC_DATA

CRT_GREEN

CRT_HSYNC

CRT_TVO_IREF

CRT_RED

CRT_IRTN

CRT_VSYNC

LVDSA_DATA_0

LVDSB_DATA_0

L_BKLT_CTRL

TV_DCONSEL_0

TV_DCONSEL_1

LVDSA_DATA#_3

LVDSA_DATA_3

LVDSB_DATA#_3

LVDSB_DATA_3

R542

10K 5% 1/16WSMT0402 LR

T14 1

R249 75 1% 1/16WSMT0402 LR

R223 4.02K 1% 1/10WSMT0603 LR(NU)

R282 10K 1% 1/16WSMT0402 LR

R239 56 5% 1/16WSMT0402 LR

R544

100 5% 1/16WSMT0402 LR

C253

0.01uF 16V 10% SMT0402 X7R LR

C251

0.01uF 16V 10% SMT0402 X7R LR

R548

100K 1% 1/16WSMT0402 LR(NU)

C248

2.2uF 6.3V 80-20% SMT0603 Y5V LR

R297 499 1% 1/16WSMT0402 LR

R220 4.02K 1% 1/10WSMT0603 LR

R240

RES 2.4K 1% 1/16WSMT0402 LR

T12

1

R237 RES 2.2K 1% 1/16WSMT0402 LR(NU)

R238 RES 2.2K 1% 1/16WSMT0402 LR(NU)

R295

1K 1% 1/16WSMT0402 LR

R261 100K 5% 1/16WSMT0402 LR

R277

499 1% 1/16WSMT0402 LR

R577 RES 80.6 1% 1/10WSMT 0603 LR

R576 RES 80.6 1% 1/10WSMT 0603 LR

R231 RES 2.2K 1% 1/16WSMT0402 LR(NU)

10

10

9

9

8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

H H

G G

F F

E E

D D

C C

B B

A A

Mini

DIN7

2. RGB signals should be routed on the same layer, have a similar number of bends,

same number of vias

0.5"

150ohm

1. The minimum spacing between each RGB is 40-mils while 50-mils is preferred

Zo=37.5

Filter

TV DAC

Zo=75

0.5"

4. TV DAC route lengths should be lenght match to within 200 mils

TVDAC RoutingGuideline

TV IRTN 150ohm

0.2"

3. All routing should be done with ground referencing as well

12"

Zo=50

GMCH

Confidential

Crestline DDR2 (3/6)

0.1

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN,ROC

(886-2)8751-8751

C

12 49Tuesday, November 18, 2008

Penryn+Candiga GM/PM45+ICH9M(VY050)

Title

Size Document Number Rev

Date: Sheet of

First International Computer,Inc.

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ6

M_A_DQ5

M_A_DQ7

M_A_DQ15

M_A_DQ14

M_A_DQ13

M_A_DQ8

M_A_DQ10

M_A_DQ9

M_A_DQ11

M_A_DQ12

M_A_DQ23

M_A_DQ22

M_A_DQ31

M_A_DQ21

M_A_DQ24

M_A_DQ16

M_A_DQ27

M_A_DQ18

M_A_DQ17

M_A_DQ19

M_A_DQ28

M_A_DQ30

M_A_DQ26

M_A_DQ20

M_A_DQ29

M_A_DQ25

M_A_DQ56

M_A_DQ39

M_A_DQ61

M_A_DQ53

M_A_DQ54

M_A_DQ38

M_A_DQ60

M_A_DQ57

M_A_DQ47

M_A_DQ63

M_A_DQ48

M_A_DQ37

M_A_DQ40

M_A_DQ58

M_A_DQ32

M_A_DQ49

M_A_DQ52

M_A_DQ50

M_A_DQ43

M_A_DQ34

M_A_DQ33

M_A_DQ62

M_A_DQ35

M_A_DQ44

M_A_DQ46

M_A_DQ42

M_A_DQ59

M_A_DQ36

M_A_DQ51

M_A_DQ45

M_A_DQ41

M_A_DQ55

M_A_DQ[63..0]

M_A_DM[7..0]

M_B_DQ[63..0]

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ7

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ11

M_B_DQ13

M_B_DQ14

M_B_DQ8

M_B_DQ9

M_B_DQ12

M_B_DQ10

M_B_DQ15

M_B_DQ30

M_B_DQ27

M_B_DQ25

M_B_DQ29

M_B_DQ19

M_B_DQ28

M_B_DQ21

M_B_DQ22

M_B_DQ26

M_B_DQ16

M_B_DQ17

M_B_DQ20

M_B_DQ18

M_B_DQ31

M_B_DQ23

M_B_DQ24

M_B_DQ59

M_B_DQ50

M_B_DQ56

M_B_DQ63

M_B_DQ46

M_B_DQ48

M_B_DQ61

M_B_DQ43

M_B_DQ41

M_B_DQ45

M_B_DQ35

M_B_DQ54

M_B_DQ44

M_B_DQ53

M_B_DQ37

M_B_DQ38

M_B_DQ60

M_B_DQ42

M_B_DQ32

M_B_DQ33

M_B_DQ62

M_B_DQ52

M_B_DQ36

M_B_DQ58

M_B_DQ57

M_B_DQ34

M_B_DQ51

M_B_DQ47

M_B_DQ39

M_B_DQ55

M_B_DQ40

M_B_DQ49

M_A_A7

M_A_A4

M_A_A8M_A_A8

M_A_A[14..0]

M_A_A2M_A_A2

M_A_A11

M_A_A13

M_A_A5M_A_A5

M_A_A6M_A_A6

M_A_A0M_A_A0

M_A_A12

M_A_A1M_A_A1

M_A_A10

M_A_A9

M_A_A3

M_A_DQS#2M_A_DQS#2

M_A_DQS7M_A_DQS7

M_A_DQS1M_A_DQS1

M_A_DQS#5M_A_DQS#5

M_A_DQS#6M_A_DQS#6

M_A_DQS0M_A_DQS0

M_A_DQS2M_A_DQS2

M_A_DQS[7..0]

M_A_DQS#7M_A_DQS#7

M_A_DQS3M_A_DQS3

M_A_DQS6M_A_DQS6 M_A_DQS#[7..0]

M_A_DQS#0M_A_DQS#0

M_A_DQS4M_A_DQS4

M_A_DQS#1M_A_DQS#1

M_A_DQS#4M_A_DQS#4

M_A_DQS5

M_A_DQS#3M_A_DQS#3

M_A_DM0M_A_DM0

M_A_DM3M_A_DM3

M_A_DM4M_A_DM4

M_A_DM5M_A_DM5

M_A_DM2M_A_DM2

M_A_DM6M_A_DM6

M_A_DM7M_A_DM7

M_A_DM1M_A_DM1

M_A_A14 M_B_A13

M_B_A9

M_B_A2

M_B_A8

M_B_A1

M_B_A12

M_B_A0

M_B_A7

M_B_A11

M_B_A6

M_B_A4

M_B_A[14..0]

M_B_A10

M_B_A5

M_B_A3

M_B_A14

M_B_DQS#6

M_B_DQS3

M_B_DQS#1

M_B_DQS2

M_B_DQS#0

M_B_DQS#5

M_B_DQS6

M_B_DQS7

M_B_DQS1

M_B_DQS[7..0]

M_B_DQS#4

M_B_DQS5

M_B_DQS#[7..0]

M_B_DQS0

M_B_DQS#3

M_B_DQS#7

M_B_DQS4

M_B_DQS#2

M_B_DM6

M_B_DM2

M_B_DM1

M_B_DM0

M_B_DM5

M_B_DM4

M_B_DM[7..0]

M_B_DM7

M_B_DM3

M_A_DQ[63..0](16) M_B_DQ[63..0](17)

M_A_A[14..0] (16)

M_A_DQS#[7..0] (16)

M_A_DQS[7..0] (16)

M_B_A[14..0] (17)

M_B_DQS#[7..0] (17)

M_B_DQS[7..0] (17)

M_A_BS0 (16)

M_A_BS1 (16)

M_A_BS2 (16)

M_A_CAS# (16)

M_A_DM[7..0] (16)

M_A_RAS# (16)

M_A_WE# (16)

M_B_BS2 (17)

M_B_BS1 (17)

M_B_BS0 (17)

M_B_RAS# (17)

M_B_WE# (17)