Force Computers SYS68K/CPU-40 User manual

P/N 202368

FORCE COMPUTERS Inc./GmbH

All Rights Reserved

This document shall not be duplicated, nor its contents used

for any purpose, unless express permission has been granted.

Copyright by FORCE COMPUTERS

SYS68K/CPU-40/41

User’s Manual

Edition No. 8

February 1997

INTRODUCTION

This page was intentionally left blank

i

TABLE OF CONTENTS

1. GENERAL INFORMATION ........................................... 1-1

1.1 Features of the CPU Board ........................................... 1-4

2. THE PROCESSOR ................................................. 2-1

2.1 The CPU 68040 ................................................... 2-1

2.2 The Shared RAM .................................................. 2-3

2.2.1 The DRM-01/4 ..................................................... 2-3

2.2.2 The DRM-01/16 .................................................... 2-4

2.2.3 The SRM-01/4 ..................................................... 2-5

2.2.4 The SRM-01/8 ..................................................... 2-6

2.3 The System EPROM ................................................ 2-7

2.4 The Local SRAM ................................................... 2-7

2.5 The Local FLASH EPROM ........................................... 2-7

2.6 The Boot EPROM .................................................. 2-7

2.7 The FGA-002 ..................................................... 2-8

2.8 The PI/T 68230 .................................................... 2-9

2.8.1 The I/O Configuration of PI/T1 ........................................ 2-10

2.8.2 The I/O Configuration of PI/T2 ........................................ 2-10

2.9 The Real Time Clock 72423 ......................................... 2-11

2.10 The DUSCC 68562 ................................................ 2-12

2.10.1 The I/O Configuration of DUSCC1 and DUSCC2 .......................... 2-13

2.11 The EAGLE Modules ............................................... 2-15

2.12 The VMEbus Interface .............................................. 2-15

2.13 The Monitor of the CPU board ........................................ 2-17

2.14 Default Jumper Settings on the CPU Board .............................. 2-18

3. SPECIFICATIONS OF THE CPU BOARD ................................ 3-1

4. ORDERING INFORMATION .......................................... 4-1

5. HISTORY OF MANUAL REVISIONS .................................... 5-1

ii

LIST OF FIGURES

Figure 1-1: Photo of the CPU Board ............................................. 1-2

Figure 1-2: Block Diagram of the CPU Board ...................................... 1-3

Figure 2-1: Location Diagram for All Jumperfields ................................. 2-20

Figure 2-2: The Front Panel of the CPU Board .................................... 2-21

LIST OF TABLES

Table 1-1: The Memory Map .................................................. 1-6

Table 1-2: The Base Addresses of the Local I/O Devices ............................. 1-7

iii

This page was intentionally left blank

SECTION 1 INTRODUCTION

1-1

1. GENERAL INFORMATION

This CPU board is a high performance single board computer based on the 68040 microprocessor and the

VMEbus. The board incorporates a modular I/O subsystem which provides a high degree of flexibility for

a wide variety of applications. The CPU board can be used with or without an I/O subsystem, called an

"EAGLE" module.

The board is able to hold a RAM Module which can be DRAM (CPU-40) or SRAM (CPU-41) based.

The CPU-40/41 family design utilizes all of the features of the powerful FORCE Gate Array (FGA-002).

Among its features is a 32-bit DMA controller which supports local (shared) memory, VMEbus and I/O data

transfers for maximum performance, parallel real time operation and responsiveness.

The EAGLE modules are installed on the CPU board via the FLXi (FORCE Local eXpansion interface). This

provides a full 32-bit interface between the base board and the EAGLE module I/O subsystem, providing

a range of I/O options.

Four multiprotocol serial I/O channels, a parallel I/O channel and a Real Time Clock with on-board battery

backup are installed on the base board which, in combination with EAGLE modules, make the CPU board

a true single board computer system.

A broad range of operating systems and kernels is available for the CPU board. However, as with all

FORCE COMPUTERS' CPU cards, VMEPROM firmware is provided with the board at no extra cost.

VMEPROM is a Real Time Kernel and is installed on the CPU board in the two16-bit wide EPROM sockets,

which results in a 32-bit wide System EPROM area. This ensures that the board is supplied ready to use.

SYS68K/CPU-40/41 USER'S MANUAL FORCE COMPUTERS

1-2

Figure 1-1: Photo of the CPU Board

SECTION 1 INTRODUCTION

1-3

Figure 1-2: Block Diagram of the CPU Board

SYS68K/CPU-40/41 USER'S MANUAL FORCE COMPUTERS

1-4

1.1 Features of the CPU 3Board

!

68040 microprocessor: 25.0 MHz on CPU-40B/41B/x

!

68040 microprocessor: 33.0 MHz on CPU-40D/41D/x

!

Shared DRAM Module: 4 Mbyte DRAM with Burst Read/Write and Parity Generation and

Checking (DRM-01/4)

16 Mbyte DRAM with Burst Read/Write and Parity Generation and

Checking (DRM-01/16)

!

Shared SRAM Module: 4 Mbyte SRAM with Burst Read/Write (SRM-01/4)

8 Mbyte SRAM with Burst Read/Write (SRM-01/8)

!

32-bit high speed DMA controller for data transfers to/from the shared RAM, VMEbus memory and

EAGLE modules; DMA controller is installed in the FGA-002.

!

Two system EPROM devices supporting 40-pin devices. Access from the 68040 using a 32-bit data

path

!

One boot EPROM for local booting, initialization of the I/O chips and configuration of the FGA-002

!

128 Kbyte SRAM with on-board battery backup

!

128 Kbyte FLASH EPROM

!

FLXi interface for installation of one EAGLE module

!

Four Serial I/O interfaces, configurable as RS232/RS422/RS485, available on the front panel

!

8-bit parallel interface with 4-bit handshake

!

Two 24-bit timers with 5-bit prescaler

!

One 8-bit timer

!

Real Time Clock with calendar and on-board battery backup

!

Full 32-bit VMEbus master/slave interface, supporting the following data transfer types:

#

A32, A24, A16 : D8, D16, D32 - Master

#

A32, A24 : D8, D16, D32 - Slave

#

UAT, RMW, ADO

!

FORCE Message Broadcast (FMB), two channels

SECTION 1 INTRODUCTION

1-5

Features of the CPU Board (cont'd)

!

Four-level VMEbus arbiter

!

SYSCLK driver

!

VMEbus interrupter (IR 1-7)

!

VMEbus interrupt handler (IH 1-7)

!

Support for ACFAIL* and SYSFAIL

!

Bus timeout counters for local and VMEbus access (15 µsec)

!

VMEPROM, Real Time Multitasking Kernel with monitor, file manager and debugger

SYS68K/CPU-40/41 USER'S MANUAL FORCE COMPUTERS

1-6

The following table summarizes the memory map of the CPU board.

Table 1-1: The Memory Map

Start End

Address Address Type

00000000 003FFFFF Shared Memory (4 Mbyte)

00000000 007FFFFF Shared Memory (8 Mbyte) or

00000000 00FFFFFF Shared Memory (16 Mbyte)

00400000 F9FFFFFF VMEbus Addresses (4 Mbyte Shared Memory)

A32: D32, D24, D16, D8

00800000 F9FFFFFF VMEbus Addresses (8 Mbyte Shared Memory)

A32: D32, D24, D16, D8

01000000 F9FFFFFF VMEbus Addresses (16 Mbyte Shared Memory)

A32: D32, D24, D16, D8

FA000000 FAFFFFFF Message Broadcast Area

FB000000 FBFEFFFF VMEbus

A24: D32, D24, D16, D8

FBFF0000 FBFFFFFF VMEbus

A16: D32, D24, D16, D8

FC000000 FCFEFFFF VMEbus

A24: D16, D8

FCFF0000 FCFFFFFF VMEbus

A16: D16, D8

FD000000 FEFFFFFF Reserved

FF000000 FF7FFFFF SYSTEM EPROM

FF800000 FFBFFFFF Local I/O

FFC00000 FFC7FFFF LOCAL SRAM

FFC80000 FFCFFFFF Local FLASH EPROM

FFD00000 FFDFFFFF Registers of FGA-002

FFE00000 FFEFFFFF BOOT EPROM

FF803E00 FF803FFF VMEbus Arbiter

FFF00000 FFFFFFFF Reserved

SECTION 1 INTRODUCTION

1-7

This table gives a brief overview of the local I/O devices and the equivalent base address.

Table 1-2: The Base Addresses of the Local I/O Devices

BASE ADDRESS DEVICE

$FF803000 RTC 72423

$FF802000 DUSCC1 68562

$FF802200 DUSCC2 68562

$FF800C00 PI/T1 68230

$FF800E00 PI/T2 68230

SECTION 1 INTRODUCTION

2-1

2. THE PROCESSOR

2.1 The CPU 68040

The 68040 is a third generation full 32 bit enhanced microprocessor. The 68040 is upward object code

compatible with the 68030, 68020, 68010 and 68000 line of microprocessors.

The 68040 combines a central processing unit core, an instruction cache, a data cache, a memory

management unit, and an enhanced bus controller.

This virtual memory processor utilizes multiple, concurrent execution units and a highly integrated

architecture providing a high level of performance.

The 68040 processor combines a 68030 compatible integer unit, a 68881/68882 compatible floating point

unit (FPU), memory management units (MMUs), and a 4 Kbyte instruction and data cache. Cache

functionality is strengthened by the built-in on-chip bus snooping logic which instantly supports cache logic

during multimaster applications.

Instruction administration is routed through both the integer unit and FPU, which link to the fully independent

data and instruction memory units. Each memory unit consists of an MMU, an address translation cache

(ATC), a main cache, and a snoop controller.

The internal blocks are designed to operate in parallel, allowing instruction execution to be overlapped. In

addition, the internal caches, the on-chip memory management unit, and the enhanced bus controller

operate parallel to one another.

The 68040 contains an enhanced bus controllerthat supports both synchronous/ asynchronous bus cycles

and burst data transfers. It contains a nonmultiplexed address bus and data bus and supports 32 bits of

address and data.

SYS68K/CPU-40/41 USER'S MANUAL FORCE COMPUTERS

2-2

Features of the 68040

!

Nonmultiplexed 32 bit address and data buses

!

16 general purpose address and data registers (32 bit wide)

!

8 floating point data registers (80 bit wide)

!

Two supervisor stack pointers (32 bit wide)

!

19 special purpose control registers

!

4 Kbyte instruction and 4 Kbyte data cache

!

On-chip paged memory management unit

!

Pipelined architecture with parallelism allowing accesses to internal caches, bus transfers, and

instruction execution in parallel

!

Synchronous bus cycles and burst read and write data transfers

!

Complete floating point support given to the 68882 FPCP subset and software emulation

!

68030 compatible

!

Low latency bus accesses to reduce cache miss penalty

!

Maximized throughput from the integer unit, FPU, MMU and bus controller

!

4 Gbyte direct addressing range

SECTION 1 INTRODUCTION

2-3

2.2 The Shared RAM

On this CPU board the shared RAM is placed on a module to allow the adaption of DRAM or SRAM to the

base board.

All signals which are needed to control the shared RAM are available on the RAM module connector.

Therefore RAM devices with different access times can also be used on this CPU board to take advantage

of the 68040 with higher frequency if it becomes available.

2.2.1 The DRM-01/4

The DRM-01/4 is a 4 Mbyte RAM module which is used on the CPU-40B/4.

Features of the DRM-01/4

!

4 Mbyte DRAM

!

Burst READ and Burst WRITE capability

!

Parity Generation and Checking

!

Asynchronous refresh is provided every 14µs

!

Accessible via VMEbus

The access address for the 68040 is $00000000 to $003FFFFF.

The access address for the VMEbus is programmable in 4 Kbyte steps through the FGA-002. The defined

memory range can be write protected in coordination with the address modifier codes. For example, in

supervisor mode the memory can be read and written, in user mode memory can only be read.

The DRAM module includes byte paritycheck for local and VMEbus accesses. If a parity error is detected

on a VMEbus cycle, a BERR is forced to the VMEbus informing the requestor that a parity error has

occurred. On local accesses, a Transfer Error Acknowledge (TEA) is forced to the processor if a parity

error was detected.

The following chart lists the required CPU clock cycles and wait states for accessing the shared RAM.

Board 68040 Clock No. of CPU Clock No. of CPU Clock No. of Wait No. of Wait

Type Frequency Cycles Counted Cycles for States for States for

From TS to TA Burst Cycles Normal Cycles Burst Cycles

for Normal Cycles

CPU-40/B 25 MHz 4 1 3 0

SYS68K/CPU-40/41 USER'S MANUAL FORCE COMPUTERS

2-4

2.2.2 The DRM-01/16

The DRM-01/16 is a 16 Mbyte RAM module which is used on the CPU-40B/16.

Features of the DRM-01/16

!

16 Mbyte DRAM

!

Burst READ and Burst WRITE capability

!

Parity Generation and Checking

!

Asynchronous refresh is provided every 14µs

!

Accessible via VMEbus

The access address for the 68040 is $00000000 to $00FFFFFF.

The access address for the VMEbus is programmable in 4 Kbyte steps through the FGA-002. The defined

memory range can be write protected in coordination with the address modifier codes. For example, in

supervisor mode the memory can be read and written, in user mode memory can only be read.

The DRAM module includes byte paritycheck for local and VMEbus accesses. If a parity error is detected

on a VMEbus cycle, a BERR is forced to the VMEbus informing the requestor that a parity error has

occurred. On local accesses, a Transfer Error Acknowledge (TEA) is forced to the processor if a parity

error was detected.

The following chart lists the required CPU clock cycles and wait states for accessing the shared RAM.

Board 68040-B Clock No. of CPU Clock No. of CPU Clock No. of Wait No. of Wait

Type Frequency Cycles Counted Cycles for States for States for

From TS to TA Burst Cycles Normal Cycles Burst Cycles

for Normal

Cycles

CPU-40/B 25 MHz 4 1 3 0

SECTION 1 INTRODUCTION

2-5

2.2.3 The SRM-01/4

The SRM-01/4 is a 4 Mbyte RAM module which is used on the CPU-41B/4.

Features of the SRM-01/4

!

4 Mbyte SRAM

!

Burst READ and Burst WRITE capability

!

Battery Backup via VMEbus

!

Accessible via VMEbus

The access address for the 68040 is $00000000 to $003FFFFF.

The access address for the VMEbus is programmable in 4 Kbyte steps through the FGA-002. The defined

memory range can be write protected in coordination with the address modifier codes. For example, in

supervisor mode the memory can be read and written, in user mode memory can only be read.

Parity check is not necessary for SRAM devices, because these components are protected against soft

errors owing alpha emission. The following chart lists the required CPU clock cycles and wait states for

accessing the shared RAM.

Board 68040 Clock No. of CPU Clock No. of CPU Clock No. of Wait No. of Wait

Type Frequency Cycles Counted Cycles for States for States for

From TS to TA Burst Cycles Normal Cycles Burst Cycles

for Normal Cycles

CPU-41/B 25 MHz 3 1 2 0

SYS68K/CPU-40/41 USER'S MANUAL FORCE COMPUTERS

2-6

2.2.4 The SRM-01/8

The SRM-01/8 is an 8 Mbyte RAM module which is used on the CPU-41B/8.

Features of the SRM-01/8

!

8 Mbyte SRAM

!

Burst READ and Burst WRITE capability

!

Battery Backup via VMEbus

!

Accessible via VMEbus

The access address for the 68040 is $00000000 to $007FFFFF.

The access address for the VMEbus is programmable in 4 Kbyte steps through the FGA-002. The defined

memory range can be write protected in coordination with the address modifier codes.

For example, in supervisor mode the memory can be read and written, in user mode memory can only be

read.

Parity check is not necessary for SRAM devices, because these components are protected against soft

errors owing alpha emission. The following chart lists the required CPU clock cycles and wait states for

accessing the shared RAM.

Board 68040 Clock No. of CPU Clock No. of CPU Clock No. of Wait No. of Wait

Type Frequency Cycles Counted Cycles for States for States for

From TS to TA Burst Cycles Normal Cycles Burst Cycles

for Normal

Cycles

CPU-41/B 25 MHz 3 1 2 0

SECTION 1 INTRODUCTION

2-7

2.3 The System EPROM

The CPU board offers two 40-pin EPROM sockets for the installation of two 16-bit wide EPROM devices.

The EPROMs present a full 32-bit data path to the processor enabling maximum performance. The

following devices are supported in the system EPROM area:

Supported Device Types in the System EPROM Area:

Organization Total Memory Capacity

64K x 16 256 Kbytes

128K x 16 512 Kbytes

256K x 16 1 Mbyte

512K x 16 2 Mbytes

2.4 The Local SRAM

The CPU board contains a 128K * 8 bit SRAM. Battery backup is provided via the on-board battery or the

VMEbus +5VSTDBY line.

2.5 The Local FLASH EPROM

A 128 Kbyte FLASH EPROM is included on the base board of the CPU-40 which can be used as additional

data backup under conditions of power down for long periods. FLASH EPROM is ideal to hold details of

the board status, such as software revision or user data which is to be kept permanently.

2.6 The Boot EPROM

The CPU board contains, in addition to the two system EPROMs, a single boot EPROM to boot the local

microprocessor, initialize all I/O devices and program the board-dependent functions of the FGA-002. All

basic initialization of the I/O devices and the FGA-002 are made through the boot EPROM.

In addition, the boot EPROM contains user utility routines,which may be called out of the user's application

program. These routines provide easysoftware access to the functionality of the FGA-002 (DMA controller,

FORCE Message Broadcast, Interrupt Management, etc.).

This manual suits for next models

1

Table of contents

Popular Control Unit manuals by other brands

PRASTEL

PRASTEL MT15000/EXT-IO Technical instructions

Moog

Moog 760K Series Installation and operation instruction

Stobag

Stobag SRCR 100 A Instructions and warnings for the fitter

CLA-VAL

CLA-VAL 90-01 Installation operation & maintenance

Trycom Technology

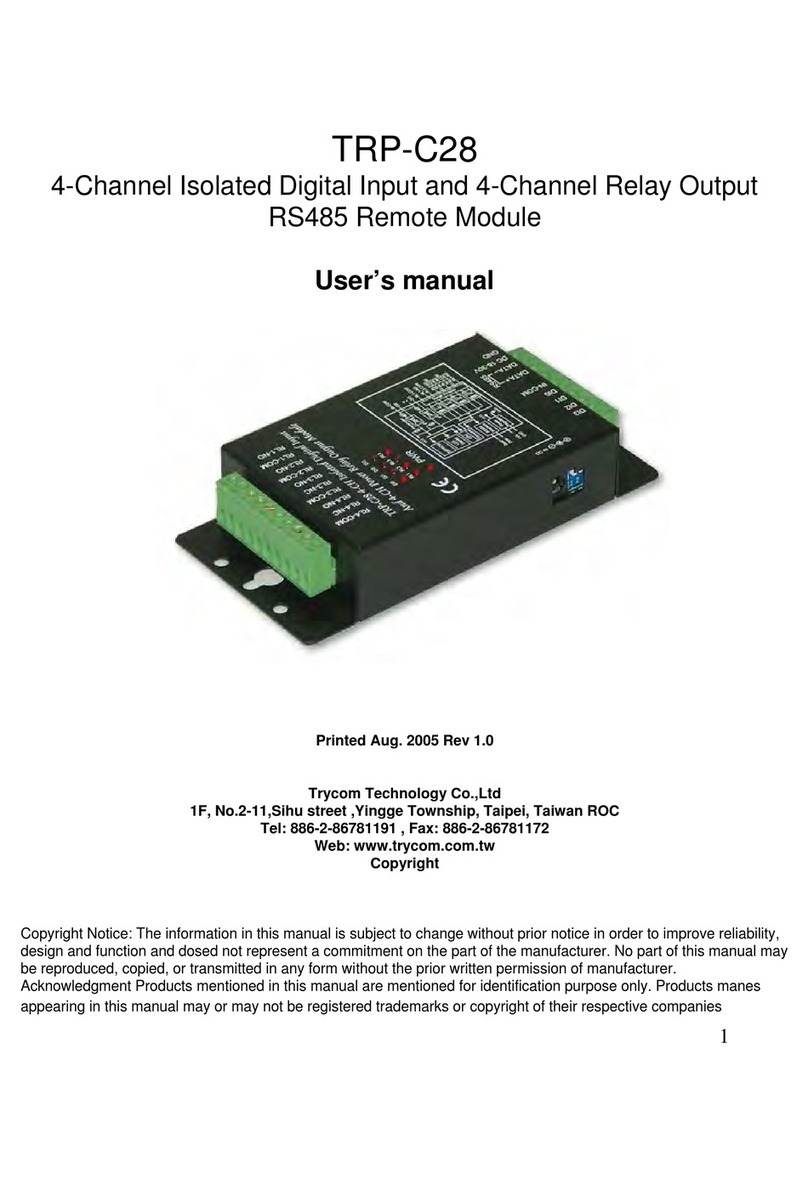

Trycom Technology TRP-C28 user manual

Pyle

Pyle Home PVC2 user manual

Mitsubishi Electric

Mitsubishi Electric QJ71MT91 user manual

INOXPA

INOXPA INNOVA F Ex Installation, service and maintenance instructions

Graco

Graco PD44 Setup & operation

HDL

HDL M/P2R.1 manual

JAUDT

JAUDT DKV 6008 Series Translation of the original operating instructions

Riello

Riello RMG 8862 A2 Installation, use and maintenance instructions