Haier L42V6-A8K User manual

Other Haier TV manuals

Haier

Haier HT-3788 User manual

Haier

Haier 28T9G User manual

Haier

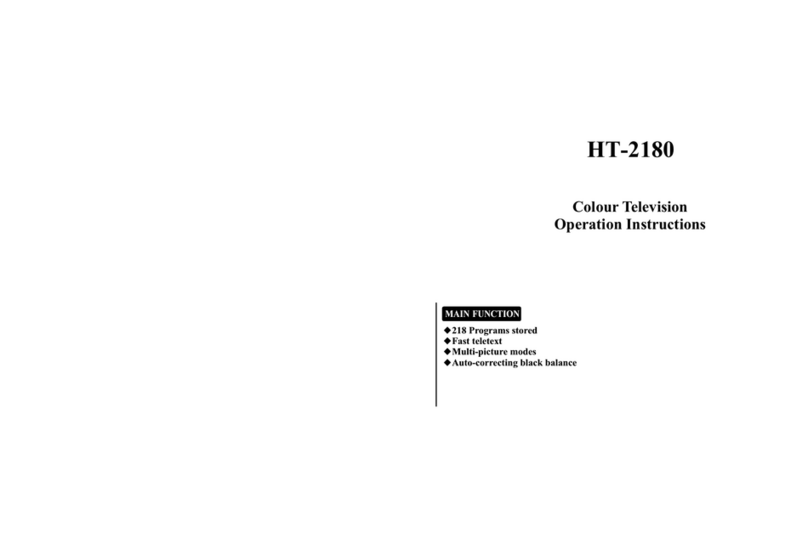

Haier HT-2180 User manual

Haier

Haier HE32A4VHA User manual

Haier

Haier HP-2999 User manual

Haier

Haier HL32R-B (MTK5380-AU) User manual

Haier

Haier HP-2999 User manual

Haier

Haier 55dr3505 User manual

Haier

Haier L22T6 User manual

Haier

Haier HT-3718 User manual

Haier

Haier HTX21S31 User manual

Haier

Haier HT-2599 User manual

Haier

Haier HTX25S31, HTX29S31S, HTX34S31 User manual

Haier

Haier HL42XP22 User manual

Haier

Haier TN131 AUV - 07-00 User manual

Haier

Haier L42S9 User manual

Haier

Haier NS-F27C User manual

Haier

Haier 29FV6H User manual

Haier

Haier L32A9 User manual

Haier

Haier HTAF29S User manual