Table of Contents

1. ADDRESSING MODE..............................................................................................................1

1.1. Inherent Addressing Mode....................................................................................................................................2

1.2. Immediate Addressing Mode

#imm................................................................................................................3

1.3. Direct Page Addressing Mode

dp...................................................................................................................4

1.4. Absolute Addressing Mode

!abs...................................................................................................................5

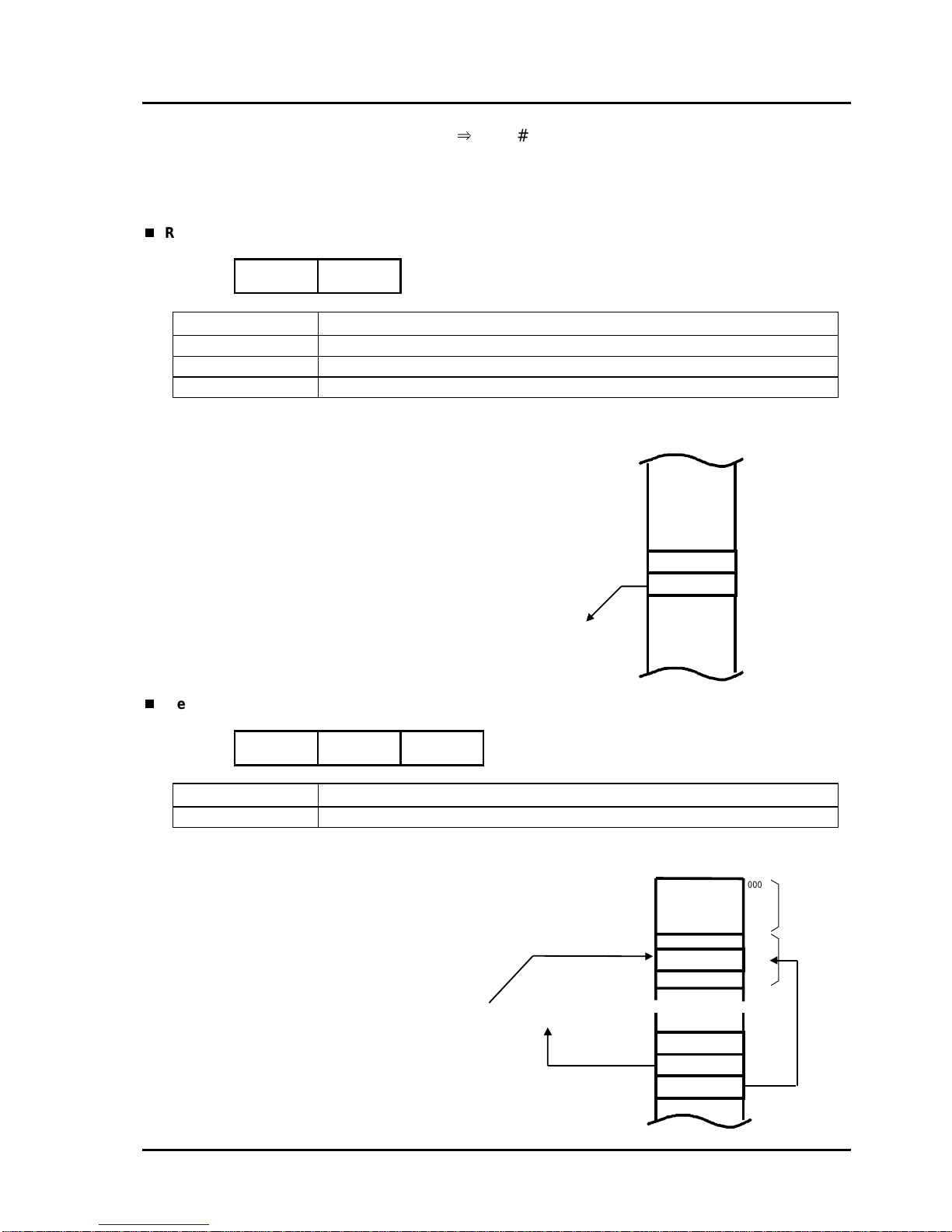

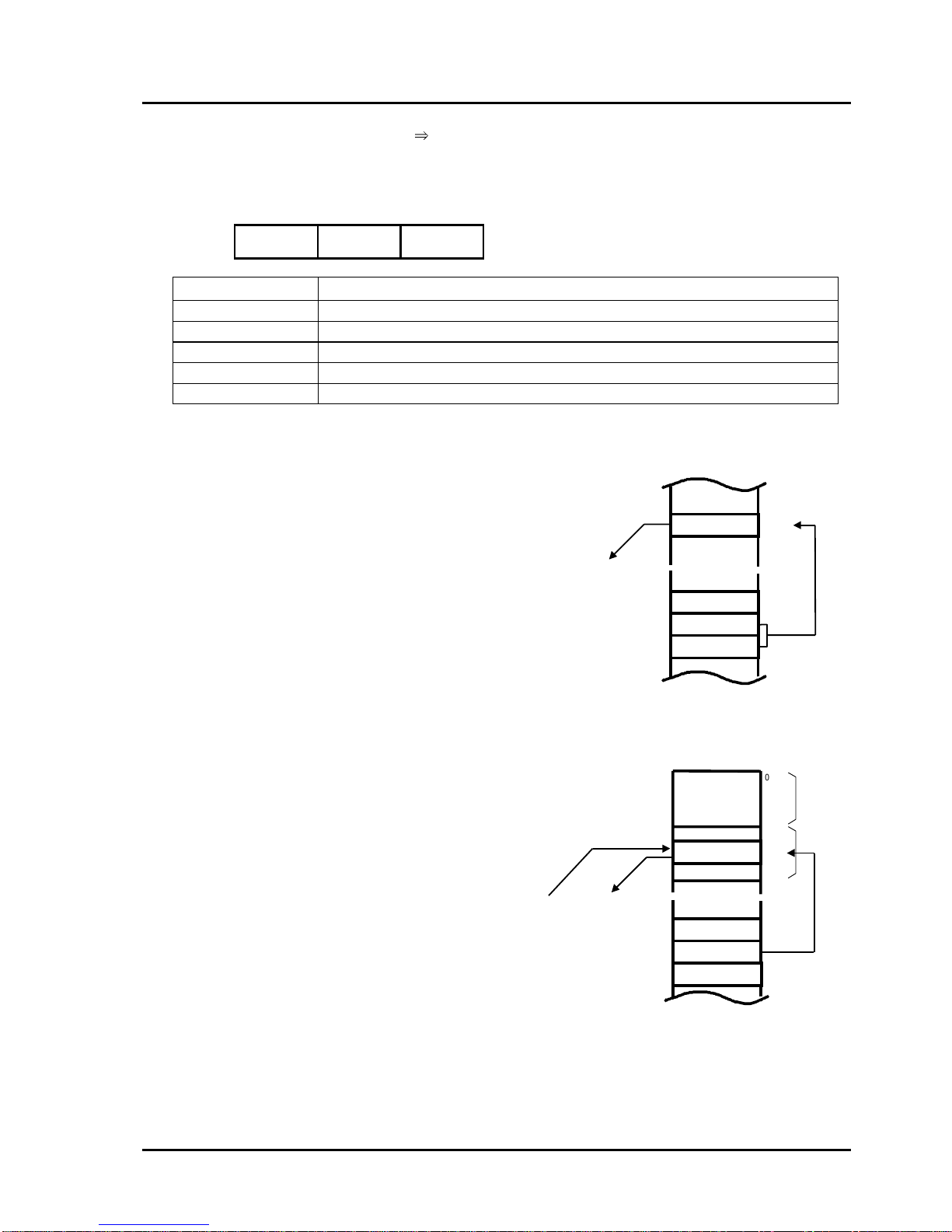

1.5. Indexed Addressing Mode....................................................................................................................................6

1.6. Indirect Addressing Mode.....................................................................................................................................8

1.7. Relative Addressing Mode.................................................................................................................................. 11

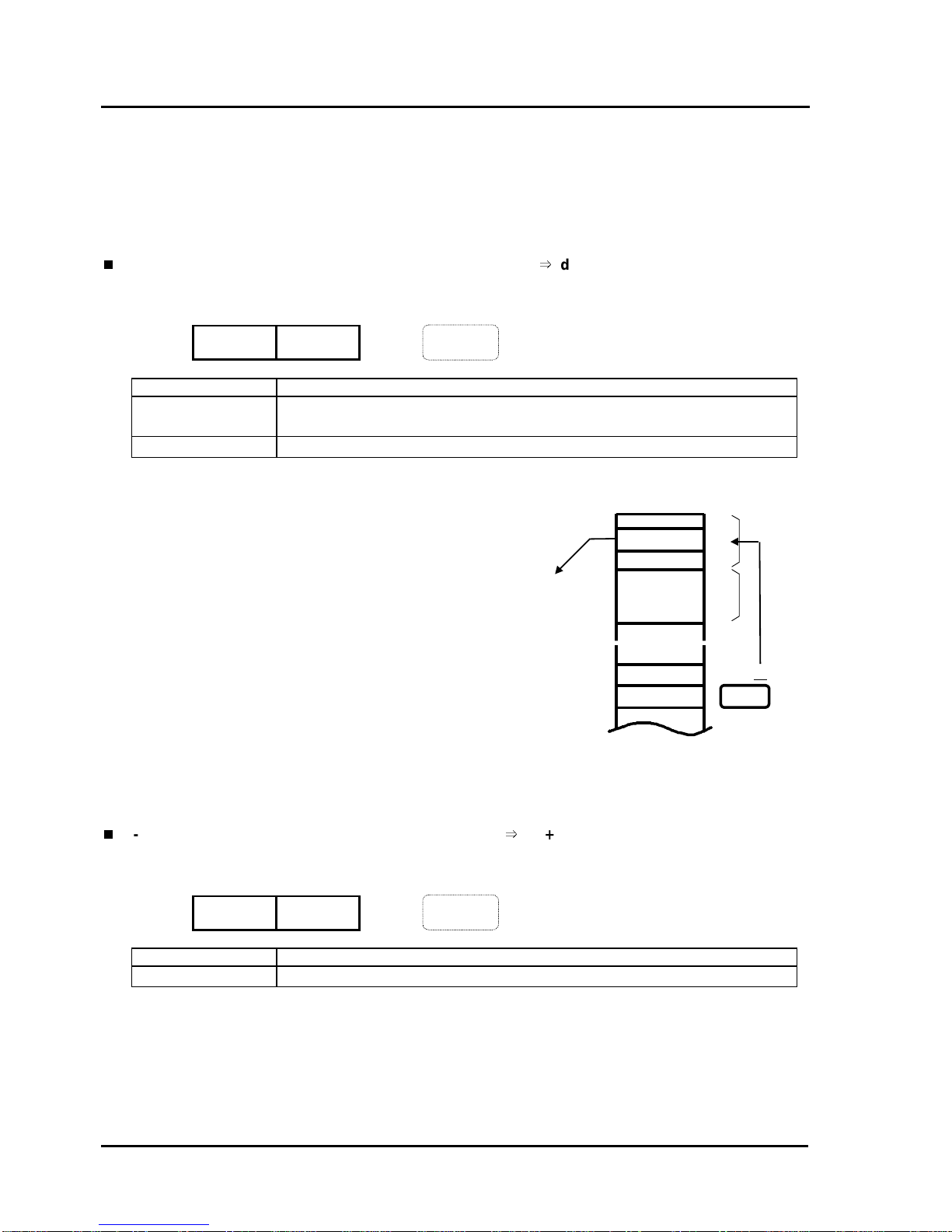

1.8. Bit Manipulation Mode.......................................................................................................................................13

1.9. 16 Bit Operation Mode

dp.......................................................................................................................... 14

1.10. Etc.................................................................................................................................................................... 15

2. INSTRUCTION SET ..............................................................................................................17

3. APPENDIX..............................................................................................................................65

3.1. Instruction Map.................................................................................................................................................. 65

3.2. Alphabetic Order Table of Instruction.................................................................................................................66

3.3. Instruction Table by Function ............................................................................................................................. 71