3-2 TRANSMITTER CIRCUITS

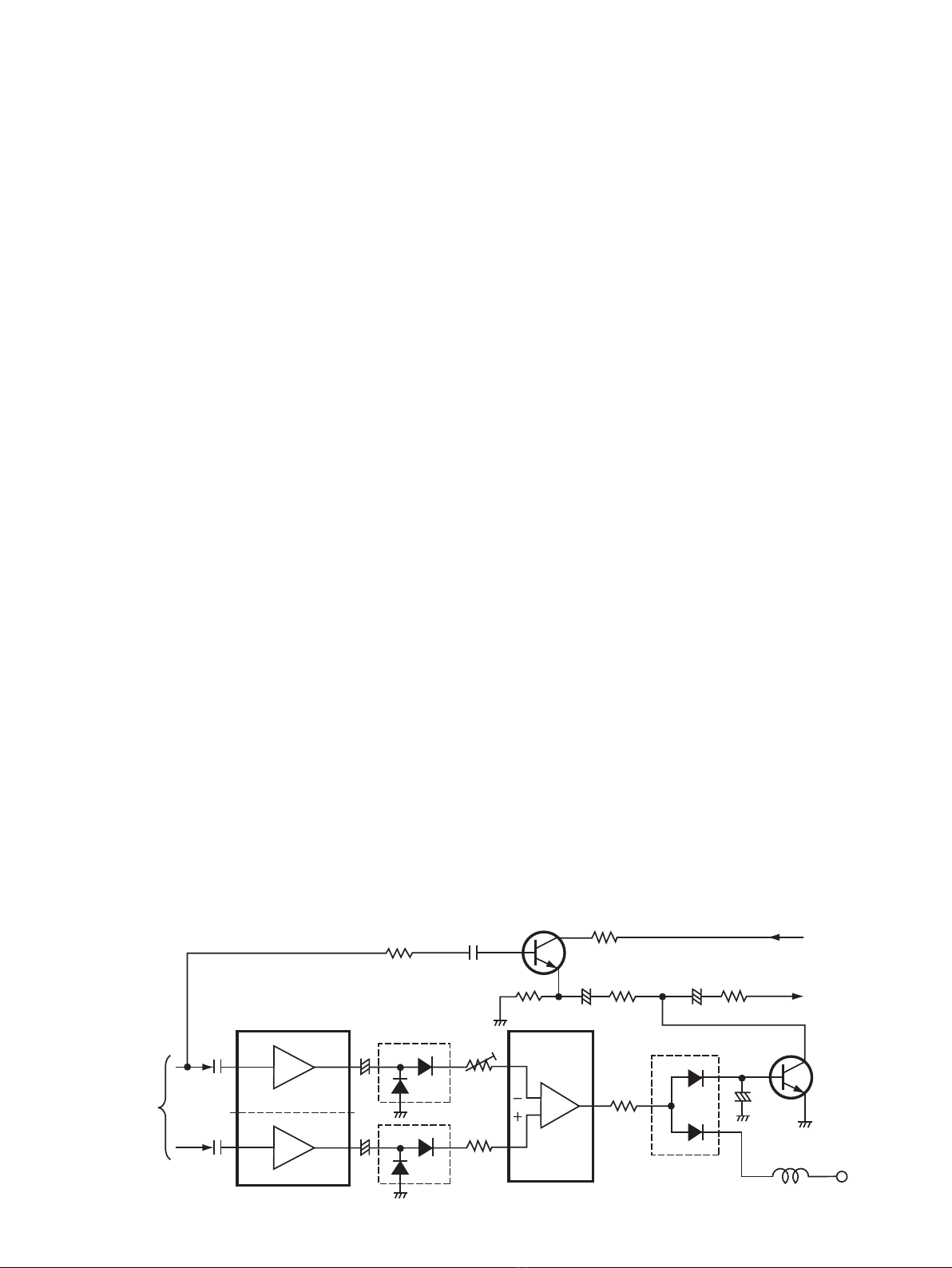

3-2-1 MIC AMPLIFIER CIRCUIT (MAIN UNIT)

The mic amplifier circuit amplifies the mic audio with the

limiter circuit to a level needed for the AM modulator.

Mic audio signals pass through the mic switch (Q4) and are

then applied to the limiter amplifier (IC13, pin 2). The mic

switch cuts out the mic audio signal while receiving.

IC13 has an ALC limiter circuit that controls the amplifier

gain to prevent signal distortion. A portion of the output

signals from IC13 (pin 3) is detected by D18 and its

detected voltages feed back to IC13 (pin 4) to control the

gain.

The output signals from IC13 (pin 3) pass through the active

low-pass filter (Q47) to cut out components higher than 2.5 kHz

and are then amplified at the mic amplifier (Q40). The signals

are then applied to the AM modulator (Q36, Q31).

3-2-2 MODULATOR CIRCUIT (MAIN UNIT)

The modulator circuit controls the collector voltage of the

transmitter linear amplifier to obtain amplitude modulation.

The modulator circuit consists of a current amplifier and a

linear amplifier. Amplified audio signals are applied to the

current amplifier (Q36) which controls the collector voltage

of the linear amplifier (Q31). The LO signal is amplified at

Q31 with variable voltage related to the mic input level so

that the LO signal level is varied as an AM modulation.

3-2-3 LOCAL SIGNAL AMPLIFIER CIRCUIT

(MAIN UNIT)

The LO signal (118.00–136.975 MHz) is obtained by mixing

the PLL output frequency (150.00–168.975 MHz) and

reference oscillator signal (32.00 MHz).

The PLL output and the reference oscillator signals are

amplified at Q29 and Q20 respectively and are then applied

to the transmitter mixer circuit (IC15). The mixed signal

is passed through the transmitter bandpass filter to re

move the out-of-band signals. Q30 is a buffer amplifier to

compensate for bandpass filter attenuation.

The passed signal is modulated at Q31 and amplified at

Q44. The attenuator-type ALC control circuit (D33, D34,

R356) reduces the signal level when a mismatched load

occurs.

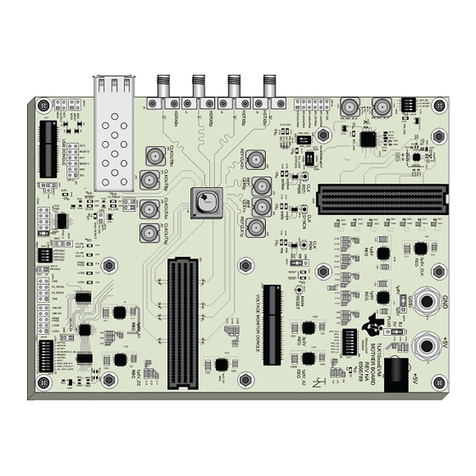

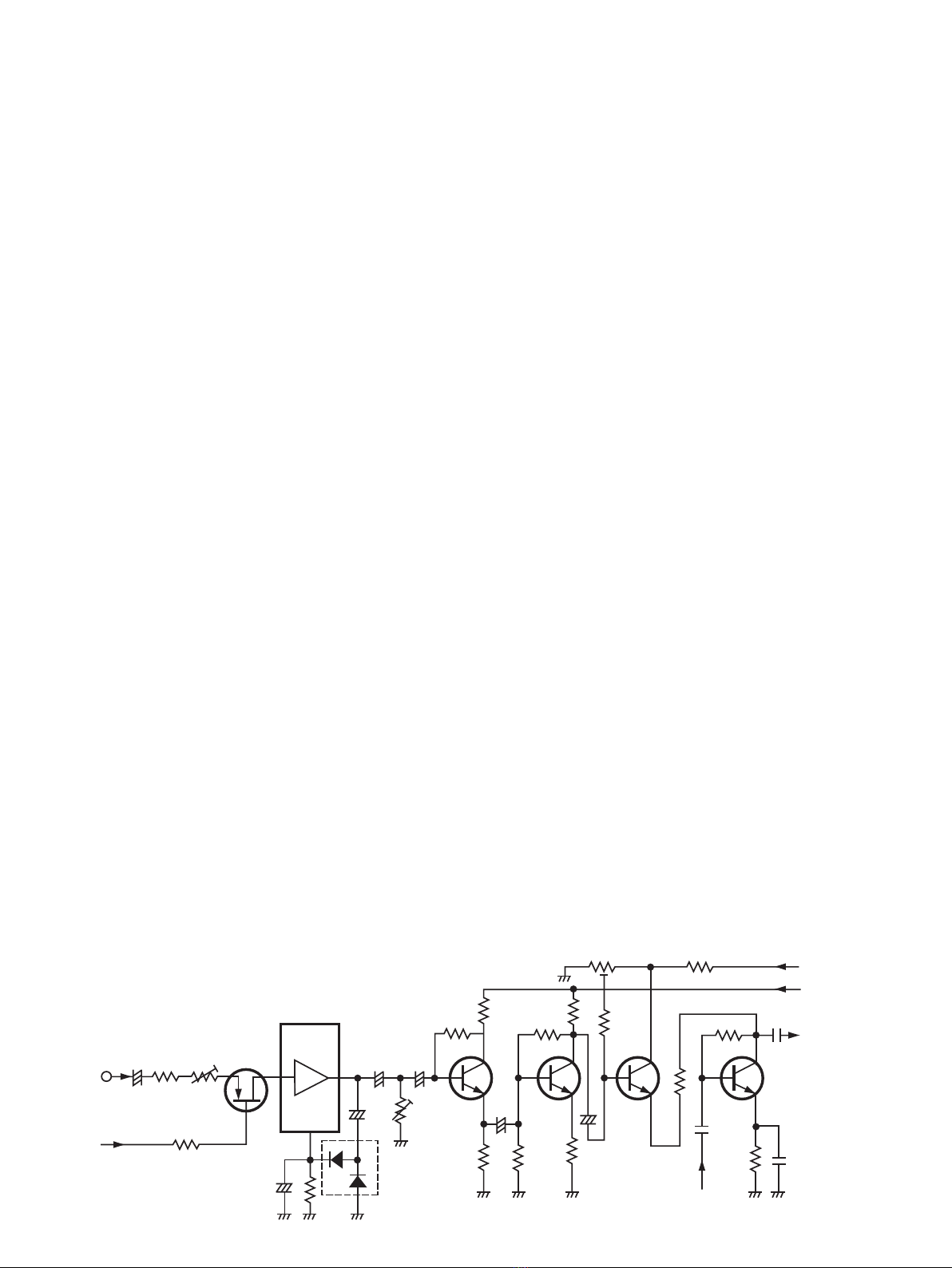

3-2-4 DRIVE AND POWER AMPLIFIERS (PA UNIT)

The signal from the MAIN unit is amplified at 3 amplifiers,

the pre-driver (Q5001), the driver (Q5003) and the final

amplifier (Q5005) in the PA unit to obtain the stable 7 W

output power.

The amplified signal passes thorough the matching circuit

(C34, C35, C59–C61), the ALC detector circuit (L13, D3–

D6), the antenna switching circuit (D7), and the low-pass

filter (L14–L16, C54–C57, C66). The signal is then applied

to the antenna connector.

3-2-5 ALC CIRCUIT (MAIN AND PA UNITS)

The RF ALC circuit protects the final amplifier (Q5005) from

a mismatched output load.

A portion of the output power from the final amplifier

(Q5005) is detected at the ALC detector (D5003–D5005)

on the PA unit. This detected voltage is set at a minimum

value when the output load is correct. However, when

mismatching occurs the detected voltage is increased.

The detected voltage is applied to the MAIN unit as an ALC

signal. The comparator (IC18) in the MAIN unit compares

the difference between the detected voltage (pin 5) and

reference voltage (pin 6). The comparator outputs "HIGH"

when mismatching occurs. The output current flows through

the attenuator-type ALC circuit (D33, D34, R356) to change

the attenuation ratio and to decrease the RF signal level.