IDT Tsi350A User manual

®

6024 Silver Creek Valley Road, San Jose, California 95138

Telephone: (800) 345-7015 • (408) 284-8200 • FAX: (408) 284-2775

Printed in U.S.A.

©2009 Integrated Device Technology, Inc.

Tsi350A™PCI-to-PCI Bridge

User Manual

80D5000_MA001_08

September 5, 2009

GENERAL DISCLAIMER

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance

and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitryembodied in an IDT product. The

Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is

granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

CODE DISCLAIMER

Code examples providedby IDT arefor illustrative purposes only and should not be relieduponfordeveloping applications. Any use of thecode examplesbelow is completely

at your own risk. IDT MAKES NOREPRESENTATIONSOR WARRANTIES OFANY KIND CONCERNING THE NONINFRINGEMENT, QUALITY, SAFETY OR SUITABILITY

OF THE CODE, EITHER EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICU-

LAR PURPOSE, ORNON-INFRINGEMENT.FURTHER,IDT MAKES NO REPRESENTATIONS OR WARRANTIESASTOTHE TRUTH,ACCURACYOR COMPLETENESS

OF ANY STATEMENTS, INFORMATION OR MATERIALS CONCERNING CODE EXAMPLES CONTAINED IN ANY IDT PUBLICATION OR PUBLIC DISCLOSURE OR

THAT ISCONTAINED ON ANY IDT INTERNET SITE. IN NO EVENT WILL IDT BE LIABLE FOR ANY DIRECT, CONSEQUENTIAL, INCIDENTAL, INDIRECT, PUNITIVE OR

SPECIAL DAMAGES, HOWEVER THEY MAY ARISE, AND EVEN IF IDT HAS BEEN PREVIOUSLY ADVISED ABOUT THE POSSIBILITY OF SUCH DAMAGES. The code

examples also may be subject to UnitedStates export control lawsand maybe subject to theexportorimportlawsof other countries andit is your responsibility to comply with

any applicable laws or regulations.

LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in lifesupport devices or systemsunless a specific written agreement pertaining to

such intended use is executed between the manufacturer and an officer of IDT.

1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform,

when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is anycomponents of a life supportdevice or system whosefailure to performcanbe reasonably expected tocause the failure of thelife support device

or system, or to affect its safety or effectiveness.

IDT, the IDT logo, and Integrated Device Technology are trademarks or registered trademarks of Integrated Device Technology, Inc.

3

Tsi350A User Manual

80D5000_MA001_08

Integrated Device Technology

www.idt.com

About this Document

This section discusses the following topics:

•“Scope” on page 3

•“Document Conventions” on page 3

•“Revision History” on page 4

Scope

The Tsi350A PCI-to-PCI Bridge User Manual discusses the features, capabilities, and configuration

requirements for the Tsi350A. It is intended for hardware and software engineers who are designing

system interconnect applications with the device.

Document Conventions

This document uses the following conventions.

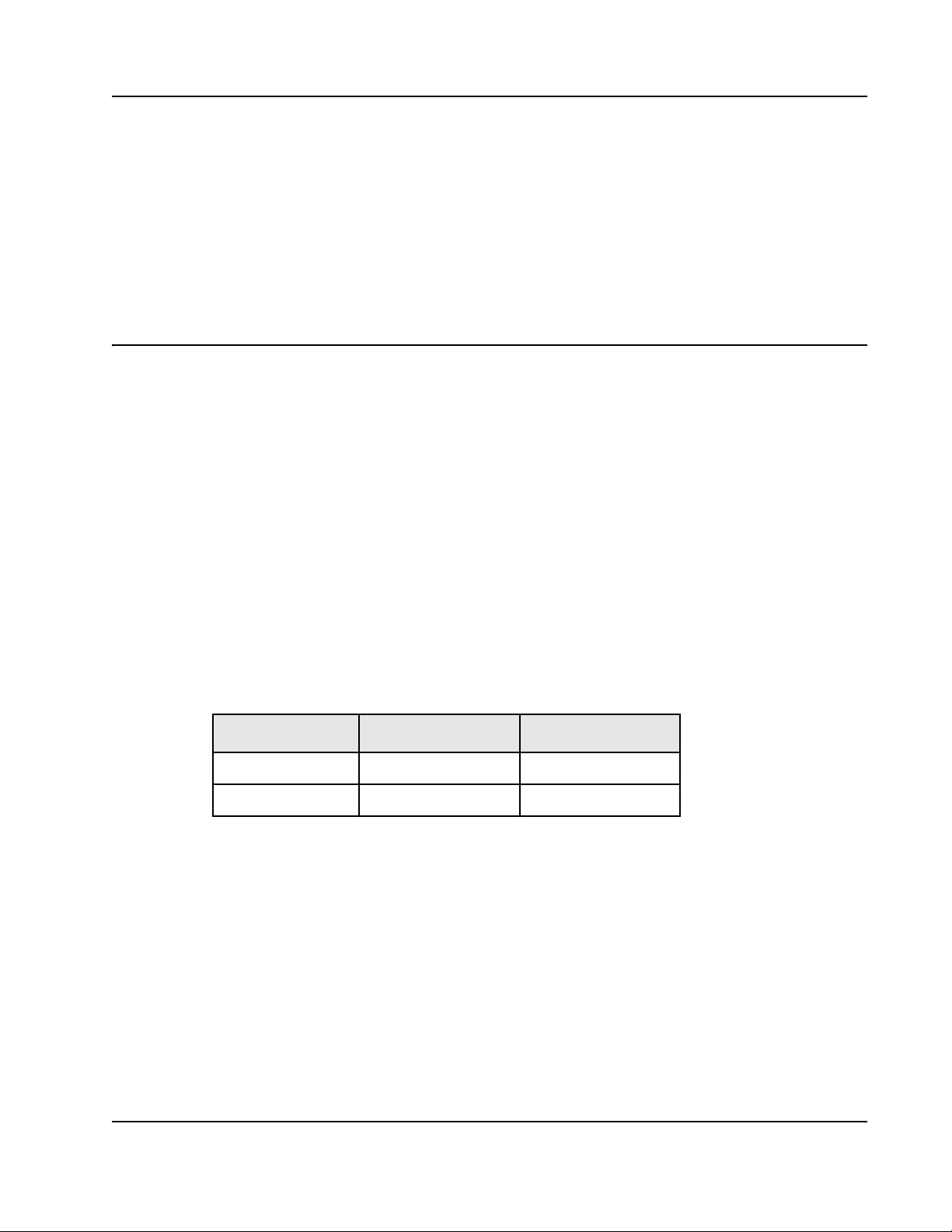

Non-differential Signal Notation

Non-differential signals are either active-low or active-high. An active-low signal has an active state of

logic 0 (or the lower voltage level), and is denoted by a lowercase “b”. An active-high signal has an

active state of logic 1 (or the higher voltage level), and is not denoted by a special character. The

following table illustrates the non-differential signal naming convention.

Object Size Notation

•Abyte is an 8-bit object.

•Aword is a 16-bit object.

•Adoubleword (Dword) is a 32-bit object.

Numeric Notation

• Hexadecimal numbers are denoted by the prefix 0x (for example, 0x04).

State Single-line signal Multi-line signal

Active low NAME_b NAMEn[3]

Active high NAME NAME[3]

About this Document4

Tsi350A User Manual

80D5000_MA001_08 Integrated Device Technology

www.idt.com

• Binary numbers are denoted by the prefix 0b (for example, 0b010).

• Registers that have multiple iterations are denoted by {x..y} in their names; where xis first register

and address, and yis the last register and address. For example, REG{0..1} indicates there are two

versions of the register at different addresses: REG0 and REG1.

Symbols

Document Status Information

• Advance – Contains information that is subject to change, and is available once prototypes are

released to customers.

• Preliminary – Contains information about a product that is near production-ready, and is revised as

required.

• Formal – Contains information about a final, customer-ready product, and is available once the

product is released to production.

Revision History

80D5000_MA001_08, Formal, September 2009

This document was rebranded as IDT. It does not include any technical changes.

80D5000_MA001_07, Formal, April 2008

This document supports the production version of the Tsi350A. The asynchronous mode functionality

was removed from this document. Information has been removed from “Secondary Clock Outputs” on

page 84 and pin 52 in “208-pin PQFP Pin List” on page 104 was changed from ASYNC_MODE to

VSS.

80D5000_MA001_06, Formal, January 2008

This document supported the production version of the Tsi350A. The Tsi350A is a performance

enhancement of the Tsi350 and there are no functional changes between the devices. All technical

information in this document applies to both the Tsi350 and the Tsi350A.

Tip

This symbol indicates a basic design concept or information considered helpful.

This symbol indicates important configuration information or suggestions.

This symbol indicates procedures or operating levels that may result in misuse or damage to

the device.

About this Document 5

Tsi350A User Manual

80D5000_MA001_08

Integrated Device Technology

www.idt.com

80D5000_MA001_05, Formal, August 2007

The changes to this document were minor and include register address clarifications in the register

chapter and a compliance list added to the overview chapter.

80D5000_MA001_04, Formal, March 2007

The following chapters were extensively edited:

•“Signals and Pinout” on page 93

•“Electrical Characteristics” on page 119

•“Package Information” on page 169

Table of contents