5

dc1403af

DEMO MANUAL DC1403A

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representa-

tion that the interconnection of its circuits as described herein will not infringe on existing patent rights.

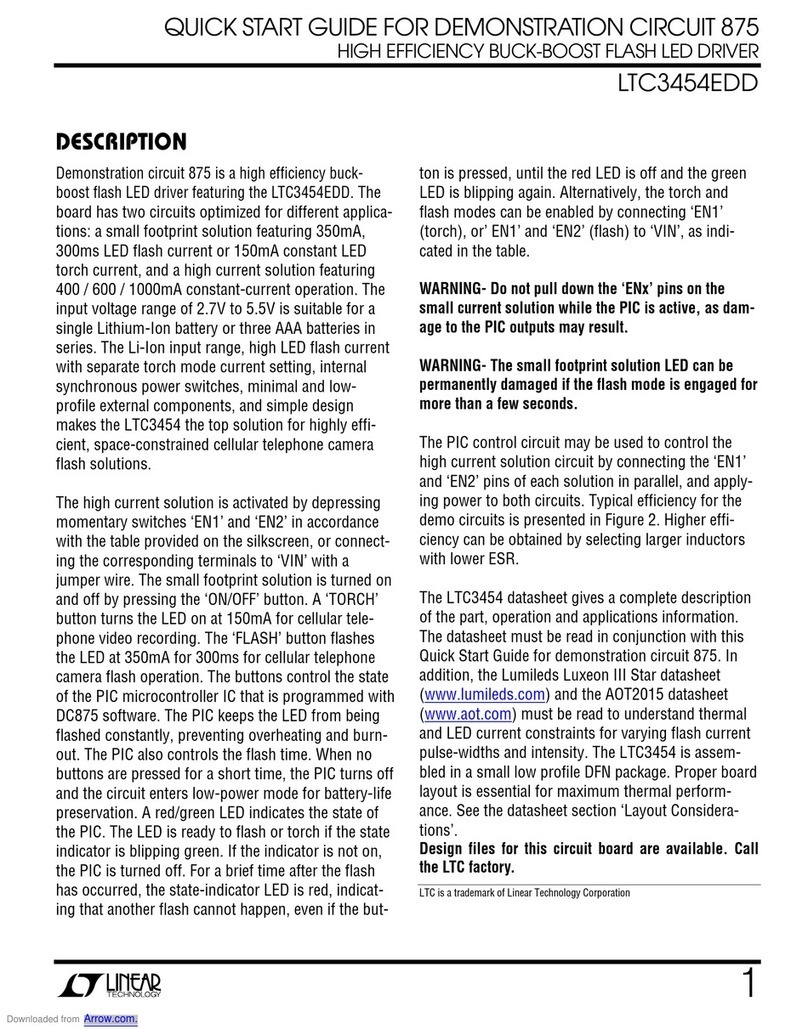

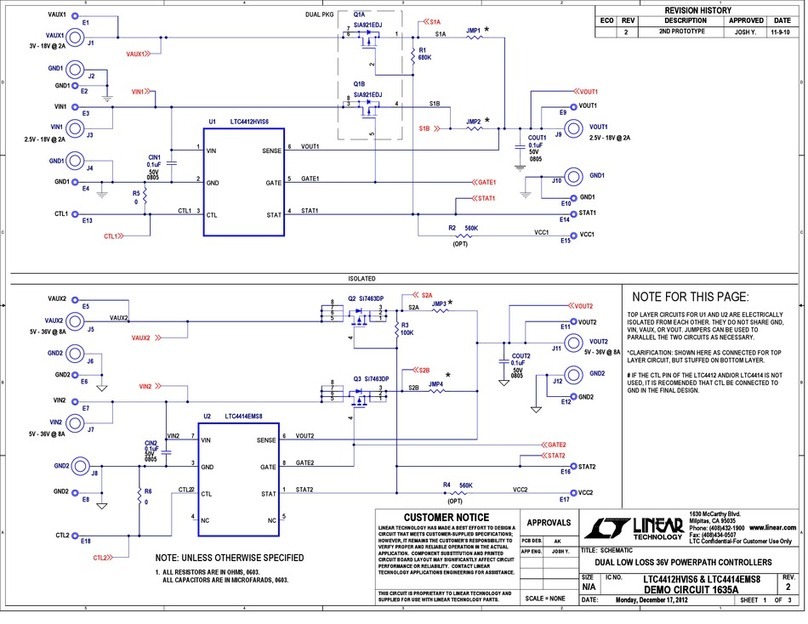

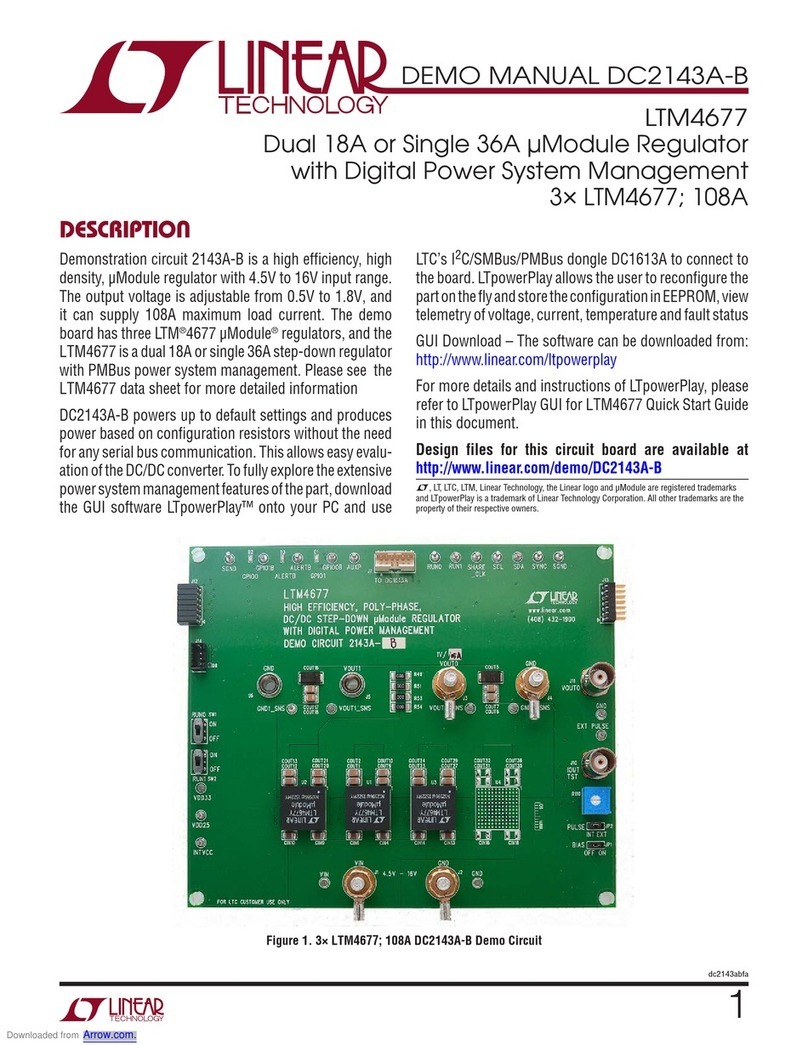

SCHEMATIC DIAGRAM

Figure 5. Demo Circuit Schematic

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

9$

NOTES: UNLESS OTHERWISE SPECIFIED,

OPT OPT

237,21$/&,5&8,7

237

237

237 237

237

OPT

(400kHz)

1. ALL CAPACITORS AND RESISTORS ARE 0402.

OPT

[2] SEE QUICK START GUIDE FOR DETAILS ON JP1 SETTING

AND INPUT VOLTAGE IMPLEMENTATION ORDER.

[2] [2]

OPT

VOUT1 VOUT2

VOUT1

VIN1

VIN1 VIN2VOUT1

VIN1 VIN1

VIN2

VOUT2

6,=(

'$7(

,&12 5(9

6+((7 2)

7,7/(

$33529$/6

3&%'(6

$33(1*

TECHNOLOGY )D[

0LOSLWDV&$

3KRQH

0F&DUWK\%OYG

/7&&RQILGHQWLDO)RU&XVWRPHU8VH2QO\

&86720(5127,&(

/,1($57(&+12/2*<+$60$'($%(67())25772'(6,*1$

&,5&8,77+$70((76&86720(56833/,('63(&,),&$7,216

+2:(9(5,75(0$,167+(&86720(565(63216,%,/,7<72

9(5,)<3523(5$1'5(/,$%/(23(5$7,21,17+($&78$/

$33/,&$7,21&20321(1768%67,787,21$1'35,17('

&,5&8,7%2$5'/$<2870$<6,*1,),&$17/<$))(&7&,5&8,7

3(5)250$1&(255(/,$%,/,7<&217$&7/,1($5

7(&+12/2*<$33/,&$7,216(1*,1((5,1*)25$66,67$1&(

7+,6&,5&8,7,635235,(7$5<72/,1($57(&+12/2*<$1'

6&+(0$7,&

6833/,(')2586(:,7+/,1($57(&+12/2*<3$576

6&$/( 121(

ZZZOLQHDUFRP

Wednesday, February 23, 2011

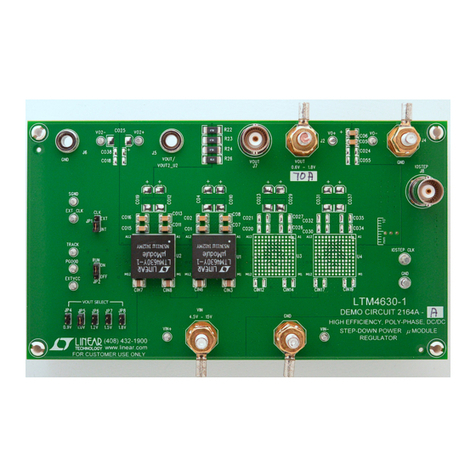

DUAL MONOLITHIC STEP-DOWN

0,

(':,1/

1$

LT3692AEFE

DEMO CIRCUIT 1403A

CONVERTER

6,=(

'$7(

,&12 5(9

6+((7 2)

7,7/(

$33529$/6

3&%'(6

$33(1*

TECHNOLOGY )D[

0LOSLWDV&$

3KRQH

0F&DUWK\%OYG

/7&&RQILGHQWLDO)RU&XVWRPHU8VH2QO\

&86720(5127,&(

/,1($57(&+12/2*<+$60$'($%(67())25772'(6,*1$

&,5&8,77+$70((76&86720(56833/,('63(&,),&$7,216

+2:(9(5,75(0$,167+(&86720(565(63216,%,/,7<72

9(5,)<3523(5$1'5(/,$%/(23(5$7,21,17+($&78$/

$33/,&$7,21&20321(1768%67,787,21$1'35,17('

&,5&8,7%2$5'/$<2870$<6,*1,),&$17/<$))(&7&,5&8,7

3(5)250$1&(255(/,$%,/,7<&217$&7/,1($5

7(&+12/2*<$33/,&$7,216(1*,1((5,1*)25$66,67$1&(

7+,6&,5&8,7,635235,(7$5<72/,1($57(&+12/2*<$1'

6&+(0$7,&

6833/,(')2586(:,7+/,1($57(&+12/2*<3$576

6&$/( 121(

ZZZOLQHDUFRP

Wednesday, February 23, 2011

DUAL MONOLITHIC STEP-DOWN

0,

(':,1/

1$

LT3692AEFE

DEMO CIRCUIT 1403A

CONVERTER

6,=(

'$7(

,&12 5(9

6+((7 2)

7,7/(

$33529$/6

3&%'(6

$33(1*

TECHNOLOGY )D[

0LOSLWDV&$

3KRQH

0F&DUWK\%OYG

/7&&RQILGHQWLDO)RU&XVWRPHU8VH2QO\

&86720(5127,&(

/,1($57(&+12/2*<+$60$'($%(67())25772'(6,*1$

&,5&8,77+$70((76&86720(56833/,('63(&,),&$7,216

+2:(9(5,75(0$,167+(&86720(565(63216,%,/,7<72

9(5,)<3523(5$1'5(/,$%/(23(5$7,21,17+($&78$/

$33/,&$7,21&20321(1768%67,787,21$1'35,17('

&,5&8,7%2$5'/$<2870$<6,*1,),&$17/<$))(&7&,5&8,7

3(5)250$1&(255(/,$%,/,7<&217$&7/,1($5

7(&+12/2*<$33/,&$7,216(1*,1((5,1*)25$66,67$1&(

7+,6&,5&8,7,635235,(7$5<72/,1($57(&+12/2*<$1'

6&+(0$7,&

6833/,(')2586(:,7+/,1($57(&+12/2*<3$576

6&$/( 121(

ZZZOLQHDUFRP

Wednesday, February 23, 2011

DUAL MONOLITHIC STEP-DOWN

0,

(':,1/

1$

LT3692AEFE

DEMO CIRCUIT 1403A

CONVERTER

REVISION HISTORY

DESCRIPTION DATE APPROVEDECO REV

EDWIN L.IC Change

302/23/11

REVISION HISTORY

DESCRIPTION DATE APPROVEDECO REV

EDWIN L.IC Change

302/23/11

REVISION HISTORY

DESCRIPTION DATE APPROVEDECO REV

EDWIN L.IC Change

302/23/11

D5

CMDSH-4E

D5

CMDSH-4E

L3

IHLP4040DZ-01

22uHL3

IHLP4040DZ-01

22uH

R8

100K

R8

100K

L1

6.8uH

L1

6.8uH

+

C1

22uF

50V

+

C1

22uF

50V

C3

4.7uF

50V

1210

C3

4.7uF

50V

1210

C14 680pFC14 680pF

C16 33pFC16 33pF

R9 8.06K 1%R9 8.06K 1%

C4 0.47uF

0603

C4 0.47uF

0603

C10

22pF

C10

22pF

R16

20k

1%

R16

20k

1%

TP4

SHDN2

TP4

SHDN2

TP6

VOUT2

TP6

VOUT2

C12

0.1uF

C12

0.1uF

C24

10nF

C24

10nF

R12 100K 1%R12 100K 1%

D6

CMDSH-4E

D6

CMDSH-4E

TP13

SYNC

TP13

SYNC

D7

OPT

D7

OPT

R6

24.9K

1%

R6

24.9K

1%

TP5

VOUT1

9$

TP5

VOUT1

9$

TP10

CMPO2

TP10

CMPO2

TP1

VIN1

TP1

VIN1

L2

4.7uH

L2

4.7uH

TP14

CLKOUT

TP14

CLKOUT

D3

CMDSH-4E

D3

CMDSH-4E

TP16

VIN2

TP16

VIN2

C2

4.7uF

50V

1210

C2

4.7uF

50V

1210

TP12

SS2

TP12

SS2

D2

B340A

D2

B340A

+

C21

22uF

50V

+

C21

22uF

50V

C11

22pF

C11

22pF

R17

40.2k

1%

R17

40.2k

1%

TP17

GND

TP17

GND

R11 100K 1%R11 100K 1%

R2

1k

1%

R2

1k

1%

10uF

C6

16V

0805

10uF

C6

16V

0805

+

C18

22uF

50V

+

C18

22uF

50V

TP15

TEMP

TP15

TEMP

R5

42.2K

1%

R5

42.2K

1%

10uF

C9

16V

0805

10uF

C9

16V

0805

R1

1k

1%

R1

1k

1%

R10 8.06K 1%R10 8.06K 1%TP9

CMPO1

TP9

CMPO1

100uF

C7

10V

1210

100uF

C7

10V

1210

R15

10.2k

1%

R15

10.2k

1%

D1

CMDSH-4E

D1

CMDSH-4E

D8

OPT

D8

OPT

FB1

FBMJ3216HS800

BEADFB1

FBMJ3216HS800

BEAD

R14 30k 1%

R14 30k 1%

100uF

C8

10V

1210

100uF

C8

10V

1210

TP3

SHDN1

TP3

SHDN1

TP8

GND

TP8

GND

C17 33pFC17 33pF

R13 30k 1%

R13 30k 1%

C5 0.47uF

0603

C5 0.47uF

0603

R7

100K

R7

100K

JP1

SINGLE

DUAL

INPUT MODE

CASCADE

JP1

SINGLE

DUAL

INPUT MODE

CASCADE

1

3

2

4

TP7

GND

TP7

GND

C13

0.1uF

C13

0.1uF

U1

LT3692AEFE

U1

LT3692AEFE

SW1

38

DIV

27

VC2 26

SS2 24

FB1

9FB2 11

CMPI2 12

CMPO2 13

BST2 14

CMPI1

8

IND2 18

SW2 20

VIN2 22

SHDN2 23

VOUT2 16

CMPO1

7

BST1

6

ILIM1

33

TJ 28

CLKOUT 29

RT/SYNC

30

VC1

32

VOUT1

4

SHDN1

35

VIN1 36

PGND

39

SS1

34

IND1

2

ILIM2 25

NC

10

NC

15

NC 21

NC 31

NC

1

NC

3

NC

5

NC 17

NC 19

NC 37

TP11

SS1

TP11

SS1

C15 680pFC15 680pF

R18

OPT

R18

OPT

C20

2.2uF

50V

1210

C20

2.2uF

50V

1210

D4

B340A

D4

B340A

C25

10nF

C25

10nF

C19

0.01uF

0603

C19

0.01uF

0603

TP2

GND

TP2

GND