Mesa 6i68 User manual

6I68

3X2X MOTHERBOARD

MANUAL

Version 1.3

This page intentionally not blank

-

Table of Contents

GENERAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

HARDWARE CONFIGURATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

GENERAL .................................................... 2

EEPROM DISABLE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

CONNECTOR POWER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

BUS SWITCH MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

AUTCONFIG .................................................. 4

VIOSELECT................................................... 4

6I68 / MODULE PIN CORRESPONDENCE

CONNECTORS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

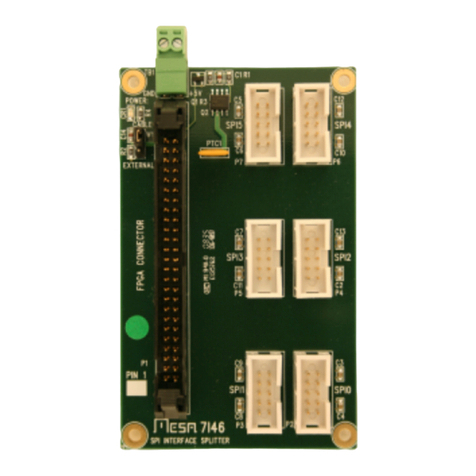

CONNECTOR LOCATIONS AND DEFAULT JUMPER POSITIONS . . . . . . . . 5

I/O CONNECTOR PIN-OUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

DIFFERENTIAL PAIRS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

JTAG PINOUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

PCIE PINOUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

LEDS ....................................................... 13

I/O LEVELS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

STARTUP I/O VOLTAGE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

POWER SUPPLY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

REFERENCE INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

6I68 Manual 1

GENERAL

DESCRIPTION

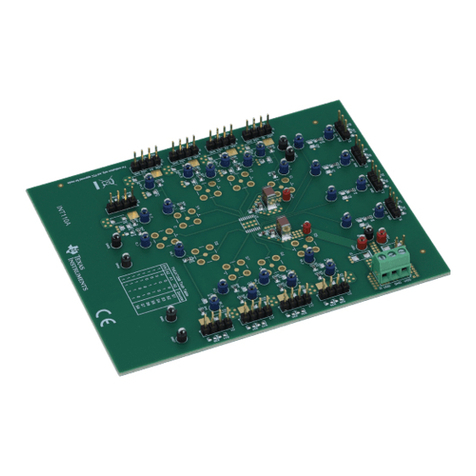

The MESA 6I68 is a 1 lane PCIE plug-in motherboard for Mesas’ 3X2X series of

FPGA daughtercards. The 6I68 breaks out the high densitydaughterboard I/O connections

into six 50 pin .1" headers with standard AnythingIO pinouts. The 6I68 also provides up to

4A of 5V power for I/O connectors via an on card switching regulator. Bus switches are

provided on all 144 I/O pins to allow interfacing with 5V I/O.

6I68 Manual 2

HARDWARE CONFIGURATION

GENERAL

Hardware setup jumper positionsassume that the 6I68card is oriented inan upright

position, that is, with the PCI connector facing the user, and the white PCB markings right

side up.

DEFAULT SETUP

EEPROM ENABLED W8 UP

AUTOCONFIG ENABLED W7 UP

RIGHT AND LEFT VIO = 3.3V W4,W5,W9,W10 UP

CONNECTOR POWER = 5V (ALL) W1,W2,W3,W12,W13,W14 LEFT

BUS SWITCH MODE = 3.3V W6,W11 DOWN

These default jumper positions are shown in the default jumper position picture on

page 5.

EEPROM ENABLE

On the 3X20 module, the PCI9056 part of thePEX8311 PCIE-Local bus bridge chip

is configured at power up via a serial EEPROM. If the EEPROM is somehow mis-

programmed orcorrupted, it can be impossible to re-write the EEPROM from the PCI bus.

To avoid this problem, The EEPROM can be temporarily disabled. W8 controls the

EEPROM enable function, When W8 is in the up position (default) the EEPROM is

enabled. When W8 is in the down position, the EEPROM is disabled. To fix a broken

EEPROMsetup,youmustpowerupthe6I68andmodulecardwiththeEEPROMdisabled,

Enable the EEPROM, and re-write the EEPROM.

.

6I68 Manual 3

HARDWARE CONFIGURATION

CONNECTOR POWER

The power connection on the I/O connectors pin 49 can supply either 3.3V or 5V

power. Supplied power should be limited to 400 mA per connector.

When the following jumpers are in the left position, 5V power is supplied to pin 49

of the associated connector. When the jumper is in the right position, 3.3V power is

supplied to to pin 49 of the associated connector.

W12 selects the voltage supplied to P2. (I/O connector for bits 0..23)

W13 selects the voltage supplied to P3. (I/O connector for bits 24..47)

W14 selects the voltage supplied to P4. (I/O connector for bits 48..71)

W3 selects the voltage supplied to P7. (I/O connector for bits 72..95)

W2 selects the voltage supplied to P6. (I/O connector for bits 96.119)

W1 selects the voltage supplied to P5. (I/O connector for bits 120..143)

BUS SWITCH MODE

The 6I68uses bus switch devices in series withall I/O pins. These devicesallowthe

3X2X inputs to be 5V tolerant and allow the I/O pins to be pulled up to 5V. The bus switch

input protection function works by disconnecting the FPGA from the IO pins when the IO

pin voltage rises above a preset threshold. This threshold determines the bus switch

operationalmodeandisselectableforthethreelefthandI/Oconnectorsandthethreeright

hand I/O connectors separately. We refer to the modes as 5V mode and 3.3V mode.

When in 5V mode, the inputs and tri-stated outputs may be pulled up to 5V. This

allows driving 5V referred loads such as I/O module racks. The disadvantage of 5V mode

is that the output impedance is higher in the high output state (when the FPGA pins are at

3.3V) as the bus switch is off when the FPGA pin is at 3.3V. When 3.3Vmode is selected,

the bus switch is always fully on unless input voltages >4V are applied, at which point the

bus switch disconnects the FPGA from the I/O pin. 3.3V mode is suggested for general

use.

When the bus switch mode jumper is in theUP position, 5Vmode is selected, when

DOWN, 3.3V bus switch mode is selected.

W6 Sets bus switch mode for P2,P3,P4, = IO 0..71

W11 Sets bus switch mode for P7,P6,P5 = IO 72..143

6I68 Manual 4

HARDWARE CONFIGURATION

AUTOCONFIG

The3X2XmodulescanbeconfiguredviathePCIEbusorfromtheirlocalEEPROM.

W7 determines the configuration mode. When W7 is in the down position, the 3X2X

module will start up unconfigured and must be configured from the PCIE host. When W7

is in the up position, the 3X2X module will be configured via its on card EEPROM.

I/O VOLTAGE SELECT

The 3X2X modules have three separate I/O power supplies, with each I/O bank

having 48 I/O signals. One bank has a fixed I/O voltage of 3.3V, while the other 2 banks

have selectable I/O voltages. Two voltage select pins are provided for each of the banks

with selectable voltages :

W4 W5 LEFT VIO

DOWN DOWN 1.5V

DOWN UP 1.8V

UP DOWN 2.5V

UP UP 3.3V

W9 W10 RIGHT VIO

DOWN DOWN 1.5V

DOWN UP 1.8V

UP DOWN 2.5V

UP UP 3.3V

6I68 / MODULE PIN CORRESPONDENCE

Inorder to simplify the differential pair routing on the 6I68, the 6I68s’ I/O pin names

have been changed from the 3X2X pin names. This affects the pins with selectable I/O

voltages. The 6I68s’ I/O connectors all end up with 16 I/O pins with selectable VIO and 8

pins with a fixed 3.3VIO on each connector. Note that FPGA configuration used with a 6I68

needs to use the proper ucf file with 6I68 pinouts. These ucf files should have 6I68 or 7I68

in their name.

6I68 Manual 5

CONNECTORS

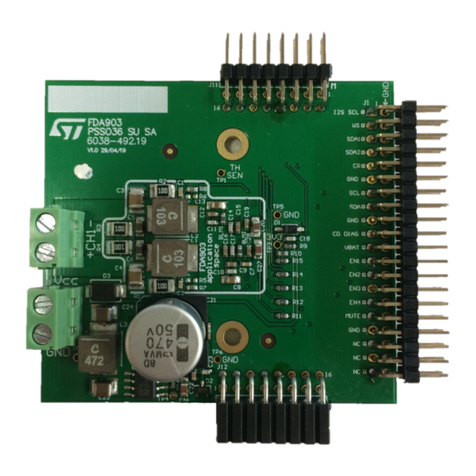

CONNECTOR LOCATIONS AND DEFAULT JUMPER POSITIONS

6I68 Manual 6

CONNECTORS

I/O CONNECTORS

P2, P3, P4,P7,P6, and P5 are the 6I68s I/O connectors. These are 50 pin box

headers that mate with standard 50 conductor female IDC connectors. Suggested mating

connector is AMP PN 1-1658621-0.. P2 pinout with 3X20 is as follows:

6I68 I/O 3X20 I/O FPGA BALL P2 PIN VIO GROUP

IO0 IO2 D11 1 LEFT VIO

IO1 IO3 C11 3 LEFT VIO

IO2 IO8 B8 5 LEFT VIO

IO3 IO9 A8 7 LEFT VIO

IO4 IO14 E7 9 LEFT VIO

IO5 IO15 D7 11 LEFT VIO

IO6 IO20 D5 13 LEFT VIO

IO7 IO21 C5 15 LEFT VIO

IO8 IO26 D3 17 LEFT VIO

IO9 IO27 D2 19 LEFT VIO

IO10 IO32 F4 21 LEFT VIO

IO11 IO33 E3 23 LEFT VIO

IO12 IO38 G3 25 LEFT VIO

IO13 IO39 G4 27 LEFT VIO

IO14 IO44 J1 29 LEFT VIO

IO15 IO45 J2 31 LEFT VIO

IO16 IO50 M4 33 FIXED 3.3VIO

IO17 IO51 M3 35 FIXED 3.3VIO

IO18 IO56 P2 37 FIXED 3.3VIO

IO19 IO57 P1 39 FIXED 3.3VIO

IO20 IO62 T2 41 FIXED 3.3VIO

IO21 IO63 T1 43 FIXED 3.3VIO

IO22 IO68 V4 45 FIXED 3.3VIO

IO23 IO69 V3 47 FIXED 3.3VIO

6I68 Manual 7

CONNECTORS

I/O CONNECTORS

P3 pinout with 3X20 is as follows:

6I68 I/O 3X20 I/O FPGA BALL P3 PIN VIO GROUP

IO24 IO4 C10 1 LEFT VIO

IO25 IO5 B10 3 LEFT VIO

IO26 IO10 E8 5 LEFT VIO

IO27 IO11 D8 7 LEFT VIO

IO28 IO16 C6 9 LEFT VIO

IO29 IO17 B6 11 LEFT VIO

IO30 IO22 B5 13 LEFT VIO

IO31 IO23 A5 15 LEFT VIO

IO32 IO28 E4 17 LEFT VIO

IO33 IO29 D4 19 LEFT VIO

IO34 IO34 F2 21 LEFT VIO

IO35 IO35 F3 23 LEFT VIO

IO36 IO40 H1 25 LEFT VIO

IO37 IO41 H2 27 LEFT VIO

IO38 IO46 K1 29 LEFT VIO

IO39 IO47 K2 31 LEFT VIO

IO40 IO52 N2 33 FIXED 3.3VIO

IO41 IO53 N1 35 FIXED 3.3VIO

IO42 IO58 R2 37 FIXED 3.3VIO

IO43 IO59 R1 39 FIXED 3.3VIO

IO44 IO64 U3 41 FIXED 3.3VIO

IO45 IO65 U2 43 FIXED 3.3VIO

IO46 IO70 W2 45 FIXED 3.3VIO

IO47 IO71 W1 47 FIXED 3.3VIO

6I68 Manual 8

CONNECTORS

I/O CONNECTORS

P4 pinout with 3X20 is as follows:

6I68 I/O 3X20 I/O FPGA BALL P4 PIN VIO GROUP

IO48 IO0 B11 1 LEFT VIO

IO49 IO1 A11 3 LEFT VIO

IO50 IO6 B9 5 LEFT VIO

IO51 IO7 A9 7 LEFT VIO

IO52 IO12 B7 9 LEFT VIO

IO53 IO13 A7 11 LEFT VIO

IO54 IO18 E6 13 LEFT VIO

IO55 IO19 D6 15 LEFT VIO

IO56 IO24 D1 17 LEFT VIO

IO57 IO25 C1 19 LEFT VIO

IO58 IO30 E1 21 LEFT VIO

IO59 IO31 E2 23 LEFT VIO

IO60 IO36 G1 25 LEFT VIO

IO61 IO37 G2 27 LEFT VIO

IO62 IO42 J4 29 LEFT VIO

IO63 IO43 H4 31 LEFT VIO

IO64 IO48 M2 33 FIXED 3.3VIO

IO65 IO49 M1 35 FIXED 3.3VIO

IO66 IO54 N4 37 FIXED 3.3VIO

IO67 IO55 N3 39 FIXED 3.3VIO

IO68 IO60 T3 41 FIXED 3.3VIO

IO69 IO61 R4 43 FIXED 3.3VIO

IO70 IO66 V2 45 FIXED 3.3VIO

IO71 IO67 V1 47 FIXED 3.3VIO

6I68 Manual 9

CONNECTORS

I/O CONNECTORS

P7 pinout with 3X20 is as follows:

6I68 I/O 3X20 I/O FPGA BALL P7 PIN VIO GROUP

IO72 IO72 W22 1 RIGHT VIO

IO73 IO73 Y22 3 RIGHT VIO

IO74 IO78 U21 5 RIGHT VIO

IO75 IO79 U20 7 RIGHT VIO

IO76 IO84 R22 9 RIGHT VIO

IO77 IO85 R21 11 RIGHT VIO

IO78 IO90 N20 13 RIGHT VIO

IO79 IO91 N19 15 RIGHT VIO

IO80 IO96 L21 17 RIGHT VIO

IO81 IO97 L22 19 RIGHT VIO

IO82 IO102 K19 21 RIGHT VIO

IO83 IO103 K20 23 RIGHT VIO

IO84 IO108 H21 25 RIGHT VIO

IO85 IO109 H22 27 RIGHT VIO

IO86 IO114 E21 29 RIGHT VIO

IO87 IO115 E22 31 RIGHT VIO

IO88 IO120 A19 33 FIXED 3.3VIO

IO89 IO121 B19 35 FIXED 3.3VIO

IO90 IO126 B17 37 FIXED 3.3VIO

IO91 IO127 C17 39 FIXED 3.3VIO

IO92 IO132 C16 41 FIXED 3.3VIO

IO93 IO133 D16 43 FIXED 3.3VIO

IO94 IO138 A13 45 FIXED 3.3VIO

IO95 IO139 B13 47 FIXED 3.3VIO

6I68 Manual 10

CONNECTORS

I/O CONNECTORS

P6 pinout with 3X20 is as follows:

6I68 I/O 3X20 I/O FPGA BALL P6 PIN VIO GROUP

IO96 IO74 W21 1 RIGHT VIO

IO97 IO75 W20 3 RIGHT VIO

IO98 IO80 T22 5 RIGHT VIO

IO99 IO81 T21 7 RIGHT VIO

IO100 IO86 P22 9 RIGHT VIO

IO101 IO87 P21 11 RIGHT VIO

IO102 IO92 M22 13 RIGHT VIO

IO103 IO93 M21 15 RIGHT VIO

IO104 IO98 L19 17 RIGHT VIO

IO105 IO99 L20 19 RIGHT VIO

IO106 IO104 J21 21 RIGHT VIO

IO107 IO105 J22 23 RIGHT VIO

IO108 IO110 G21 25 RIGHT VIO

IO109 IO111 G22 27 RIGHT VIO

IO110 IO116 E19 29 RIGHT VIO

IO111 IO117 E20 31 RIGHT VIO

IO112 IO122 A18 33 FIXED 3.3VIO

IO113 IO123 B18 35 FIXED 3.3VIO

IO114 IO128 D17 37 FIXED 3.3VIO

IO115 IO129 E17 39 FIXED 3.3VIO

IO116 IO134 B15 41 FIXED 3.3VIO

IO117 IO135 A15 43 FIXED 3.3VIO

IO118 IO140 C13 45 FIXED 3.3VIO

IO119 IO141 D13 47 FIXED 3.3VIO

6I68 Manual 11

CONNECTORS

I/O CONNECTORS

P5 pinout with 3X20 is as follows:

6I68 I/O 3X20 I/O FPGA BALL P5 PIN VIO GROUP

IO120 IO76 V22 1 RIGHT VIO

IO121 IO77 V21 3 RIGHT VIO

IO122 IO82 T20 5 RIGHT VIO

IO123 IO83 T19 7 RIGHT VIO

IO124 IO88 N22 9 RIGHT VIO

IO125 IO89 N21 11 RIGHT VIO

IO126 IO94 M20 13 RIGHT VIO

IO127 IO95 M19 15 RIGHT VIO

IO128 IO100 K21 17 RIGHT VIO

IO129 IO101 K22 19 RIGHT VIO

IO130 IO106 J18 21 RIGHT VIO

IO131 IO107 J19 23 RIGHT VIO

IO132 IO112 F20 25 RIGHT VIO

IO133 IO113 F21 27 RIGHT VIO

IO134 IO118 D21 29 RIGHT VIO

IO135 IO119 D22 31 RIGHT VIO

IO136 IO124 C18 33 FIXED 3.3VIO

IO137 IO125 D18 35 FIXED 3.3VIO

IO138 IO130 A16 37 FIXED 3.3VIO

IO139 IO131 B16 39 FIXED 3.3VIO

IO140 IO136 A14 41 FIXED 3.3VIO

IO141 IO137 B14 43 FIXED 3.3VIO

IO142 IO142 B12 45 FIXED 3.3VIO

IO143 IO143 C12 47 FIXED 3.3VIO

6I68 Manual 12

CONNECTORS

DIFFERENTIAL PAIRS

The 6I68 supports LVDS signaling on all I/O pairs, that is all even/odd I/O pins

starting with 0 comprise a differential pair on the 6I68. Which FPGA pins can have LVDS

capability depends on the specific daughterboard module.

JTAG CONNECTOR

The 6I68 brings out the 3X2Xmodules JTAG interface toa 6pin .1" inline connector

P1. P1 pinout is as follows:

PIN FUNCTION PIN FUNCTION

1 TMS 4 TCK

2 TDI 5 GND

3 TDO 6 2.5V

6I68 Manual 13

OPERATION

LEDS

The 6I68 has 3 status LEDS, CR3: a RED PWRFAIL LED that indicates that the

3.3V output is out of regulation, CR1: a RED /DONE LED tha indicates that the FPGA is

not configured, and CR2: a green power on LED.

IO LEVELS

The FPGA chips used in the 3X2X modules are not 5V tolerant but external bus

switch parts are used on the 6I68 to make the I/O pins 5V tolerant. The bus switch parts

disconnect the FPGA pinsfrom the I/O pins when theI/O pins are driven to positive voltage

levels that would damage the FPGA.

The voltage level that causes disconnect can be selected to be ~4V (3.3V mode) or

~3.3V (5Vmode). For most applications, the 3.3V mode should be used. The 5V mode is

useful when driving 5V referred loads.

Note that there is no protection against negative input voltages other than the input

clamp diodes in the FPGA and bus switches, so negative input voltages must be limited

to -.5V

STARTUP I/O VOLTAGE

After power-up or system reset and before the the FPGA is configured, the FPGAs

pull-up resistors will pull all I/O signals to a high level. If the FPGA is used for motion

control or controlling devices that could present a hazard when enabled, external circuitry

should be designed so that this initial state results in a safe condition.

POWER SUPPLY

The 6I68 uses a on card switching regulator from the bus +12V to supply the 5V

power to the I/O connectors. Maximum total 5V current is 4A. 3.3V module power is taken

directly from the PCIE bus connector.

6I68 Manual 14

REFERENCE

SPECIFICATIONS

POWER MIN MAX NOTES:

12V POWER SUPPLY 8V 13.2V From PCIE

3.3V POWER SUPPLY 3.15V 3.45V From PCIE

POWER CONSUMPTION: ---- 2A Depends on FPGA

Configuration and

external load

MAX 5V CURRENT TO I/O CONNS --- 300 mA Per Connector

MAX 3.3V CURRENT TO I/O CONNS --- 300 mA Per Connector

ABSOLUTE MAX I/O PIN VOLTAGE -.5V 7V 5V tolerant mode

ABSOLUTE MAX I/O PIN VOLTAGE -.5V 4V 3.3V mode

TEMPERATURE RANGE -C version 0 oC +70 oC

TEMPERATURE RANGE -I version -40 oC +85 oC

Other manuals for 6i68

1

Table of contents

Other Mesa Motherboard manuals