Micrel KS8852HLE User manual

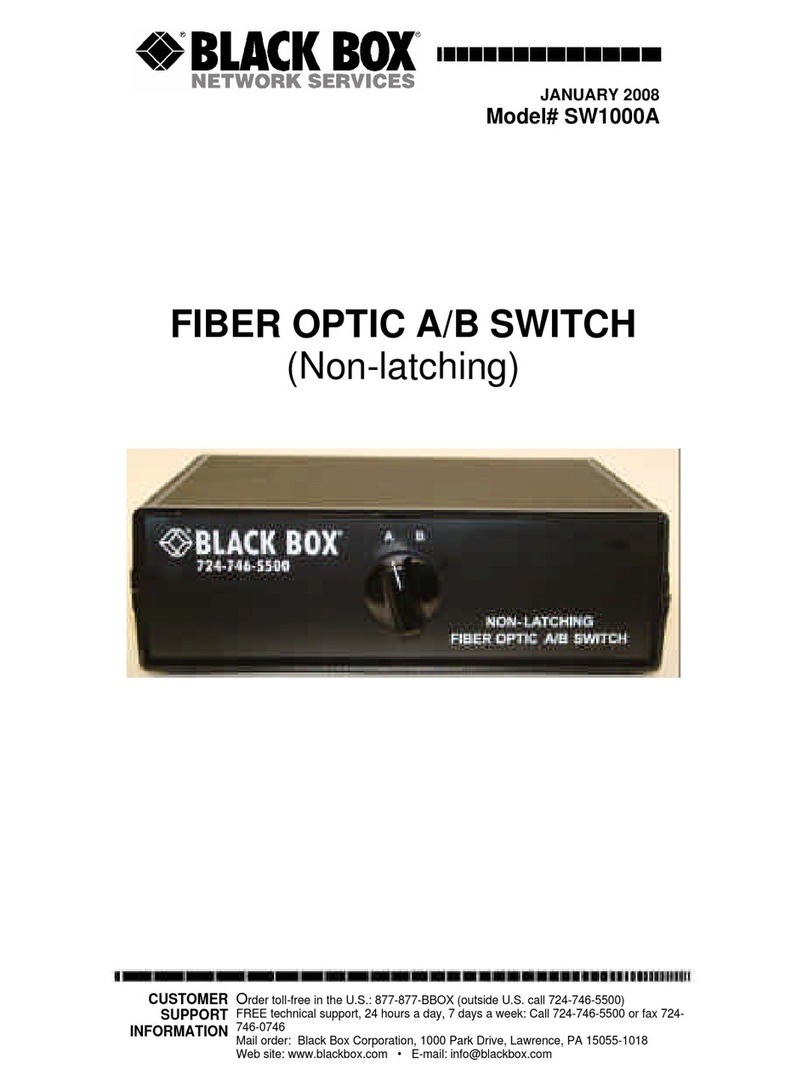

KS8852HLE

Two-Port 10/100 Mb/s Ethernet Switch with

8 or 16-Bit Host Interface

Revision 1.0

General Description

The KSZ8852 product line consists of industrial capable

Ethernet switches, providing integrated communication for

a range of Industrial Ethernet and general Ethernet

applications.

The KSZ8852 product enables distributed, daisy-chained

topologies preferred for industrial Ethernet networks.

Conventional centralized (i.e., star-wired) topologies are

also supported for fault tolerant arrangements.

A flexible 8 or 16-bit general bus interface is provided for

interfacing to an external host processor.

The wire-speed, store-and-forward switching fabric

provides a full complement of QoS and congestion control

features optimized for real-time Ethernet.

The KSZ8852 product is built upon Micrel’s industry-

leading Ethernet technology, with features designed to

offload host processing and streamline your overall design:

•Wire-speed Ethernet switching fabric with extensive

filtering

•Two integrated 10/100BASE-TX PHY transceivers,

featuring the industry’s lowest power consumption

•Full-featured QoS support

•Flexible management options that support common

standard interfaces

A robust assortment of power management features

including energy-efficient Ethernet (EEE) have been

designed in to satisfy energy-efficient environments.

Datasheets and support documentation are available on

Micrel’s web site at: www.micrel.com.

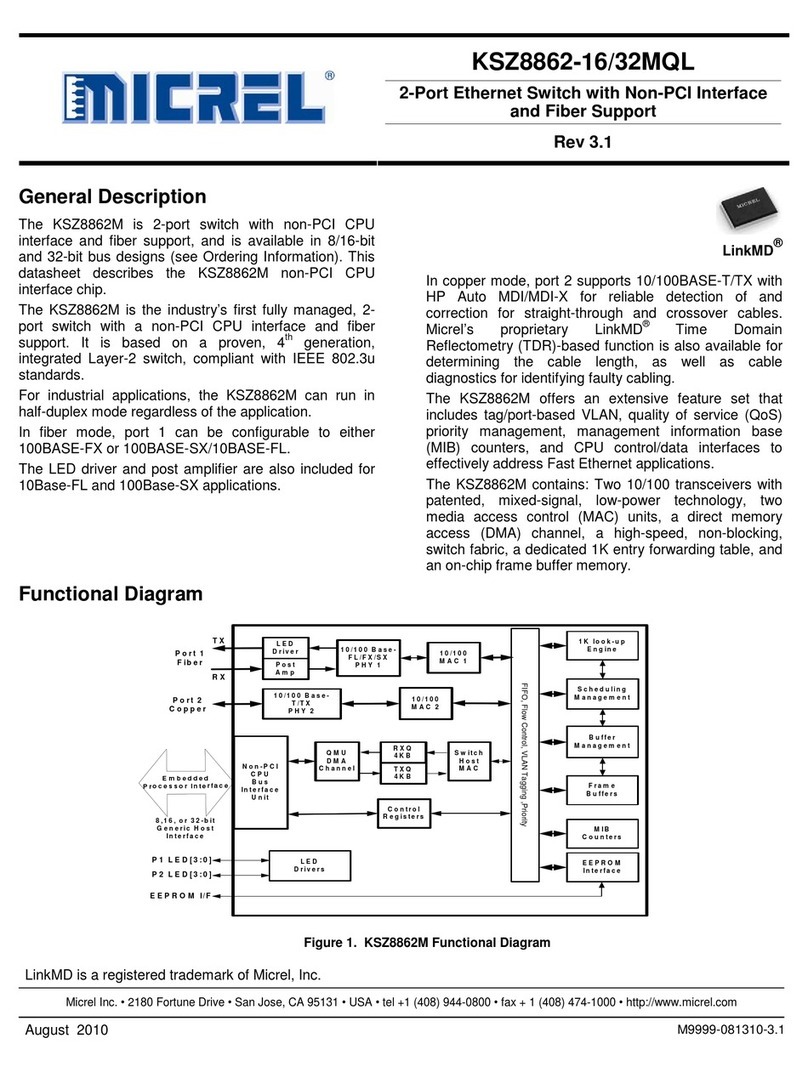

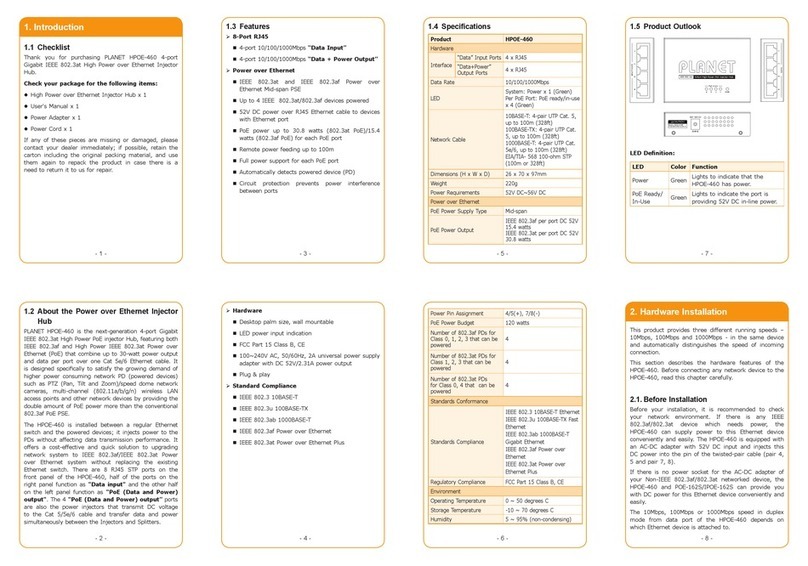

KSZ8852 Top Level Architecture

LinkMD is a registered trademark of Micrel, Inc.

ETHERSYNCH is a trademark of Micrel, Inc.

Magic Packet is a registered trademark of Advanced Micro Devices, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

June 23, 2014 Revision 1.0

Micrel, Inc.

KSZ8852HLE

Functional Diagram

KSZ8852HLE Functional Diagram

June 23, 2014 2 Revision 1.0

Micrel, Inc.

KSZ8852HLE

Features

Management Capabilities

•The KSZ8852 includes all the functions of a

10/100BASE-T/TX switch system which combines a

switch engine, frame buffer management, address

look−up table, queue management, MIB counters,

media access controllers (MAC) and PHY transceivers

•Non-blocking store-and-forward switch fabric assures

fast packet delivery by utilizing 1024 entry forwarding

table

•Port mirroring/monitoring/sniffing: ingress and/or egress

traffic to any port

•MIB counters for fully compliant statistics gathering −

34 counters per port

•Loopback modes for remote failure diagnostics

•Rapid spanning tree protocol support (RSTP) for

topology management and ring/linear recovery

Robust PHY Ports

•Two integrated IEEE 802.3 / 802.3u compliant Ethernet

transceivers supporting 10BASE-T and 100BASE-TX

•On-Chip termination resistors and internal biasing for

differential pairs to reduce power

•HP Auto MDI/MDI-X™ crossover support eliminating the

need to differentiate between straight or crossover

cables in applications!

MAC Ports

•Three internal media access control (MAC) units

•2Kbyte Jumbo packet support

•Tail tagging mode (one byte added before FCS) support

at Port 3 to inform the processor which ingress port

receives the packet and its priority

•Programmable MAC addresses for Port 1 and Port 2

and self-address filtering support

•MAC filtering function to filter or forward unknown

unicast packets

Advanced Switch Capabilities

•Non-blocking store-and-forward switch fabric assures

fast packet delivery by utilizing 1024 entry forwarding

table

•IEEE 802.1Q VLAN for up to 16 groups with full range of

VLAN IDs

•IEEE 802.1p/Q tag insertion or removal on a per port

basis (egress) and support double-tagging

•VLAN ID tag/untag options on per port basis

•Fully compliant with IEEE 802.3 / 802.3u standards

•IEEE 802.3x full-duplex with force mode option and

half−duplex backpressure collision flow control

•IEEE 802.1w rapid spanning tree protocol support

•IGMP v1/v2/v3 snooping for multicast packet filtering

•QoS/CoS packets prioritization support: 802.1p,

DiffServ-based and re-mapping of 802.1p priority field

per port basis on four priority levels

•IPv4/IPv6 QoS support

•IPv6 multicast listener discovery (MLD) snooping

Support

•Programmable rate limiting at the ingress and egress

ports

•Broadcast storm protection

•1K entry forwarding table with 32K frame buffer

•4 priority queues with dynamic packet mapping for IEEE

802.1P, IPv4 TOS (DIFFSERV), IPv6 Traffic Class, etc.

•Source address filtering for implementing ring topologies

Comprehensive Configuration Registers Access

•Complete register access via the parallel Host Interface

•Facility to load MAC Address from EEPROM at power

up & reset time

•I/O Pin Strapping facility to set certain register bits from

I/O pins at reset time

•Control registers configurable on-the-fly

Host Interface

•Selectable 8 or 16 bit wide interface

•Supports Big- and Little-endian processors

•Indirect data bus for data, address and byte enable to

access any I/O registers and RX/TX FIFO buffers

•Large internal memory with 12KByte for RX FIFO and

6Kbytes for TX FIFO.

•Programmable low, high and overrun water marks for

flow control in RX FIFO

•Efficient architecture design with configurable host

interrupt schemes to minimize host CPU overhead and

utilization

•Queue management unit (QMU) supervises data

transfers across this interface

June 23, 2014 3 Revision 1.0

Micrel, Inc.

KSZ8852HLE

Power and Power Management

•Single 3.3V power supply with optional VDD I/O for

1.8V, 2.5V or 3.3V

•Integrated low voltage (~1.3V) low-noise regulator

(LDO) output for digital and analog core power

•Supports IEEE P802.3az™ Energy Efficient Ethernet

(EEE) to reduce power consumption in transceivers in

LPI state

•Full-chip hardware or software power down (all registers

value are not saved and strap-in value will re-strap after

release the power down)

•Energy detect power down (EDPD), which disables the

PHY transceiver when cables are removed

•Wake On LAN supported with configurable packet

control

•Dynamic clock tree control to reduce clocking in areas

not in use

•Power consumption less than 0.5W

Additional Features

•Single 25MHz +50 ppm reference clock requirement

•Comprehensive programmable two LED indicators

support for link, activity, full/half duplex and 10/100

speed

Packaging

•Commercial Temperature Range: 0°C to +70°C and

Extended Industrial Temperature Ranges: -40°C to

+105°C and -40°C to +115°C

•64−pin (10mm x 10mm) lead free (ROHS) LQFP

package with heat exposed ground paddle for low

thermal resistance

•0.11µm technology for lower power consumption

Target Applications

•General and Industrial Ethernet applications

•Wireless LAN Access Point and Gateway

•Set top / Game box

•Test and measurement equipment

•Automotive

June 23, 2014 4 Revision 1.0

Micrel, Inc.

KSZ8852HLE

Ordering Information

Part Number Temperature

Range Package Lead Finish Description

KSZ8852HLECA(1) 0°C to +70°C 64−Pin 10x10mm

LQFP with

exposed pad Sn Commercial Temperature Range Switch

KSZ8852HLEWA −40°C to +105°C 64−Pin 10x10mm

LQFP with

exposed pad Sn Extended (105°C) Industrial Temperature

Range Switch

KSZ8852HLEYA −40°C to +115°C 64−Pin 10x10mm

LQFP with

exposed pad Sn Extended (115°C) Industrial Temperature

Range Switch

KSZ8852HLE-EVAL KSZ8852 Evaluation Board

Note:

1. Contact Micrel for availability.

Revision History

Revision

Date

Summary of Changes

1.0 11/21/13 Initial Draft

June 23, 2014 5 Revision 1.0

Micrel, Inc.

KSZ8852HLE

Contents

General Description ................................................................................................................................................................1

Functional Diagram.................................................................................................................................................................2

Features..................................................................................................................................................................................3

Management Capabilities....................................................................................................................................................3

Robust PHY Ports ...............................................................................................................................................................3

MAC Ports ...........................................................................................................................................................................3

Advanced Switch Capabilities .............................................................................................................................................3

Comprehensive Configuration Registers Access................................................................................................................3

Host Interface ......................................................................................................................................................................3

Power and Power Management..........................................................................................................................................4

Additional Features..............................................................................................................................................................4

Packaging............................................................................................................................................................................4

Target Applications..............................................................................................................................................................4

Ordering Information...............................................................................................................................................................5

Revision History ......................................................................................................................................................................5

Contents..................................................................................................................................................................................6

List of Figures........................................................................................................................................................................13

List of Tables.........................................................................................................................................................................14

Acronyms ..............................................................................................................................................................................15

Pin Configuration...................................................................................................................................................................17

Pin Description......................................................................................................................................................................18

Strapping Options .................................................................................................................................................................23

Functional Description...........................................................................................................................................................24

Direction Terminology...........................................................................................................................................................24

Physical (PHY) Block............................................................................................................................................................25

100BASE-TX Transmit......................................................................................................................................................25

100BASE−TX Receive ......................................................................................................................................................25

Scrambler/De−Scrambler (100BASE−TX Only)................................................................................................................25

PLL Clock Synthesizer (Recovery)....................................................................................................................................25

10BASE-T Receive............................................................................................................................................................25

MDI/MDI−X Auto Crossover..................................................................................................................................................26

Straight Cable................................................................................................................................................................26

Crossover Cable............................................................................................................................................................27

Auto Negotiation....................................................................................................................................................................28

LinkMD®Cable Diagnostics..................................................................................................................................................29

Access............................................................................................................................................................................29

Usage.............................................................................................................................................................................29

On−Chip Termination Resistors ........................................................................................................................................29

Loopback Support .............................................................................................................................................................30

Far-End Loopback .........................................................................................................................................................30

Near−End (Remote) Loopback......................................................................................................................................30

Media Access Controller (MAC) Block..................................................................................................................................31

Mac Operation...................................................................................................................................................................31

Address Lookup.................................................................................................................................................................31

Learning.............................................................................................................................................................................31

Migration............................................................................................................................................................................31

Aging..................................................................................................................................................................................31

Forwarding.........................................................................................................................................................................31

Inter Packet Gap (IPG)......................................................................................................................................................34

Back-Off Algorithm ............................................................................................................................................................34

Late Collision.....................................................................................................................................................................34

Legal Packet Size..............................................................................................................................................................34

Flow Control.......................................................................................................................................................................34

Half-Duplex Backpressure.................................................................................................................................................34

Broadcast Storm Protection...............................................................................................................................................35

Port Individual MAC Address and Source Port Filtering ...................................................................................................35

June 23, 2014 6 Revision 1.0

Micrel, Inc.

KSZ8852HLE

Address Filtering Function.................................................................................................................................................35

Switch Block..........................................................................................................................................................................37

Switching Engine...............................................................................................................................................................37

Spanning Tree Support .....................................................................................................................................................37

Rapid Spanning Tree Support...........................................................................................................................................38

Discarding State.............................................................................................................................................................38

Learning State................................................................................................................................................................38

Forwarding State............................................................................................................................................................38

Tail Tagging Mode.........................................................................................................................................................38

IGMP Support....................................................................................................................................................................39

“IGMP” Snooping...........................................................................................................................................................39

“Multicast Address Insertion” in the Static MAC Table..................................................................................................39

IPv6 MLD Snooping.......................................................................................................................................................39

Port Mirroring Support.......................................................................................................................................................40

“Receive Only” Mirror-on-a-Port.....................................................................................................................................40

“Transmit Only” Mirror-on-a-Port....................................................................................................................................40

“Receive and Transmit” Mirror-on-Two-Ports................................................................................................................40

IEEE 802.1Q VLAN Support..............................................................................................................................................40

QoS Priority Support..........................................................................................................................................................41

Port-Based Priority ............................................................................................................................................................41

802.1p-Based Priority........................................................................................................................................................41

802.1p Priority Field Re-mapping......................................................................................................................................42

DiffServ-Based Priority......................................................................................................................................................42

Rate-Limiting Support........................................................................................................................................................42

MAC Address Filtering Function........................................................................................................................................43

Queue Management Unit (QMU)..........................................................................................................................................44

Transmit Queue (TXQ) Frame Format..............................................................................................................................44

Frame Transmitting Path Operation in TXQ......................................................................................................................45

Driver Routine for Transmitting Packets from Host Processor to KSZ8852 .....................................................................46

Receive Queue (RXQ) Frame Format...............................................................................................................................47

Frame Receiving Path Operation in RXQ .........................................................................................................................48

Driver Routine for Receiving Packets from the KSZ8852 to the Host Processor .............................................................48

Device Clocks........................................................................................................................................................................50

Power....................................................................................................................................................................................51

Internal Low Voltage LDO Regulator....................................................................................................................................52

Power Management..............................................................................................................................................................53

Normal Operation Mode....................................................................................................................................................53

Energy Detect Mode..........................................................................................................................................................53

Global Soft Power-Down Mode.........................................................................................................................................54

Energy-Efficient Ethernet (EEE)........................................................................................................................................54

Wake-On-LAN ...................................................................................................................................................................55

Detection of Energy...........................................................................................................................................................55

Detection of Linkup............................................................................................................................................................55

Wake-Up Packet................................................................................................................................................................55

Magic Packet™ .................................................................................................................................................................55

Interrupt Generation on Power Management Related Events.......................................................................................56

To Generate an Interrupt on the PME Signal Pin..........................................................................................................56

To Generate an Interrupt on the INTRN Signal Pin.......................................................................................................56

Interfaces...............................................................................................................................................................................57

Bus Interface Unit (BIU) / Host Interface...........................................................................................................................57

Supported Transfers......................................................................................................................................................57

Physical Data Bus Size..................................................................................................................................................57

Little and Big Endian Support........................................................................................................................................58

Asynchronous Interface.................................................................................................................................................58

BIU Summary.................................................................................................................................................................59

Serial EEPROM Interface..................................................................................................................................................60

Device Registers...................................................................................................................................................................61

June 23, 2014 7 Revision 1.0

Micrel, Inc.

KSZ8852HLE

Register Map of CPU Accessible I/O Registers....................................................................................................................63

I/O Registers......................................................................................................................................................................63

Internal I/O Register Space Mapping for Switch Control and Configuration (0x000 - 0x0FF).......................................63

Internal I/O Register Space Mapping for Host Interface Unit (0x100 - 0x16F)..............................................................69

Internal I/O Register Space Mapping for the QMU (0x170 −0x1FF) ............................................................................71

Special Control Registers (0x700 −0x7FF)...................................................................................................................73

Register Bit Definitions..........................................................................................................................................................74

Internal I/O Register Mapping for Switch Control and Configuration (0x000 - 0x0FF)......................................................74

Chip ID and Enable Register (0x00 - 0x001): CIDER....................................................................................................74

Switch Global Control Register 1 (0x002 - 0x003): SGCR1..............................................................................................74

Switch Global Control Register 2 (0x004 – 0x005): SGCR2.............................................................................................76

Switch Global Control Register 3 (0x006 - 0x007): SGCR3..............................................................................................77

0x008 – 0x00B: Reserved.................................................................................................................................................77

Switch Global Control Register 6 (0x00C - 0x00D): SGCR6 ............................................................................................78

Switch Global Control Register 7 (0x00E - 0x00F): SGCR7.............................................................................................79

MAC Address Register 1 (0x010 - 0x011): MACAR1 .......................................................................................................80

MAC Address Register 2 (0x012 - 0x013): MACAR2 .......................................................................................................80

MAC Address Register 3 (0x014 - 0x015): MACAR3 .......................................................................................................80

Type-of-Service (TOS) Priority Control Registers.................................................................................................................81

TOS Priority Control Register 1 (0x016-– 0x017): TOSR1 ...............................................................................................81

TOS Priority Control Register 2 (0x018 - 0x019): TOSR2 ................................................................................................82

TOS Priority Control Register 3 (0x01A - 0x01B): TOSR3................................................................................................83

TOS Priority Control Register 4 (0x01C - 0x1D): TOSR4.................................................................................................83

TOS Priority Control Register 5 (0x01E - 0x1F): TOSR5..................................................................................................84

TOS Priority Control Register 6 (0x020 - 0x021): TOSR6 ................................................................................................85

TOS Priority Control Register 7 (0x022 - 0x023): TOSR7 ................................................................................................85

TOS Priority Control Register 8 (0x024 - 0x025): TOSR8 ................................................................................................86

Indirect Access Data Registers.............................................................................................................................................87

Indirect Access Data Register 1 (0x026 - 0x027): IADR1.................................................................................................87

Indirect Access Data Register 2 (0x028 - 0x029): IADR2.................................................................................................87

Indirect Access Data Register 3 (0x02A - 0x02B): IADR3 ................................................................................................87

Indirect Access Data Register 4 (0x02C - 0x02D): IADR4................................................................................................87

Indirect Access Data Register 5 (0x02E - 0x02F): IADR5 ................................................................................................88

Indirect Access Control Register (0x030 - 0x031): IACR..................................................................................................88

Power Management Control and Wake-Up Event Status.....................................................................................................89

Power Management Control and Wake-Up Event Status (0x032 – 0x033): PMCTRL.....................................................89

Power Management Event Enable Register (0x034 - 0x035): PMEE...............................................................................90

Go Sleep Time and Clock Tree Power-Down Control Registers..........................................................................................91

Go Sleep Time Register (0x036 - 0x037): GST ................................................................................................................91

Clock Tree Power-Down Control Register (0x038 - 0x039): CTPDC................................................................................91

0x03A – 0x04B: Reserved.................................................................................................................................................91

PHY and MII Basic Control Registers...................................................................................................................................92

PHY 1 and MII Basic Control Register (0x04C-– 0x04D): P1MBCR.................................................................................92

PHY 1 and MII Basic Status Register (0x04E - 0x04F): P1MBSR....................................................................................93

PHY 1 PHYID Low Register (0x050 - 0x051): PHY1ILR...................................................................................................94

PHY 1 PHYID High Register (0x052 - 0x053): PHY1IHR.................................................................................................94

PHY 1 Auto-Negotiation Advertisement Register (0x054 - 0x055): P1ANAR...................................................................95

PHY 1 Auto−Negotiation Link Partner Ability Register (0x056 - 0x057): P1ANLPR.........................................................96

PHY 2 and MII Basic Control Register (0x058 - 0x059): P2MBCR...................................................................................96

PHY 2 and MII Basic Status Register (0x05A - 0x05B): P2MBSR....................................................................................98

PHY2 PHYID Low Register (0x05C - 0x05D): PHY2ILR ..................................................................................................99

PHY 2 PHYID High Register (0x05E - 0x05F): PHY2IHR.................................................................................................99

PHY 2 Auto-Negotiation Advertisement Register (0x060 - 0x061): P2ANAR...................................................................99

PHY 2 Auto-Negotiation Link Partner Ability Register (0x062 -0x063): P2ANLPR.........................................................100

0x0x064 - 0x065: Reserved.............................................................................................................................................100

PHY1 Special Control and Status Register (0x066 - 0x067): P1PHYCTRL...................................................................100

0x068 –-0x069: Reserved ...............................................................................................................................................100

June 23, 2014 8 Revision 1.0

Micrel, Inc.

KSZ8852HLE

PHY2 Special Control and Status Register (0x06A - 0x06B): P2PHYCTRL ..................................................................101

Port 1 Control Registers......................................................................................................................................................102

Port 1 Control Register 1 (0x06C - 0x06D): P1CR1........................................................................................................102

Port 1 Control Register 2 (0x06E - 0x06F): P1CR2........................................................................................................104

Port 1 VID Control Register (0x070 - 0x071): P1VIDCR.................................................................................................105

Port 1 Control Register 3 (0x072 - 0x073): P1CR3.........................................................................................................105

Port 1 Ingress Rate Control Register 0 (0x074 - 0x075): P1IRCR0................................................................................106

Port 1 Ingress Rate Control Register 1 (0x076 - 0x077): P1IRCR1................................................................................107

Port 1 Egress Rate Control Register 0 (0x078 - 0x079): P1ERCR0...............................................................................107

Port 1 Egress Rate Control Register 1 (0x07A - 0x07B): P1ERCR1..............................................................................107

Port 1 PHY Special Control/Status, LinkMD (0x07C - 0x07D): P1SCSLMD ..................................................................108

Port 1 Control Register 4 (0x07E - 0x07F): P1CR4........................................................................................................109

Port 1 Status Register (0x080 - 0x081): P1SR................................................................................................................110

0x082 - 0x083: Reserved ................................................................................................................................................111

Port 2 Control Registers......................................................................................................................................................112

Port 2 Control Register 1 (0x084 - 0x085): P2CR1.........................................................................................................112

Port 2 Control Register 2 (0x086 - 0x087): P2CR2.........................................................................................................114

Port 2 VID Control Register (0x088 - 0x089): P2VIDCR.................................................................................................115

Port 2 Control Register 3 (0x08A-0x08B): P2CR3..........................................................................................................115

Port 2 Ingress Rate Control Register 0 (0x08C - 0x08D): P2IRCR0...............................................................................116

Port 2 Ingress Rate Control Register 1 (0x08E - 0x08F): P2IRCR1...............................................................................116

Port 2 Egress Rate Control Register 0 (0x090 - 0x091): P2ERCR0...............................................................................117

Port 2 Egress Rate Control Register 1 (0x092 – 0x093): P2ERCR1..............................................................................117

Port 2 PHY Special Control/Status, LinkMD(0x094 - 0x095): P2SCSLMD....................................................................118

Port 2 Control Register 4 (0x096 - 0x097): P2CR4.........................................................................................................119

Port 2 Status Register (0x098 - 0x099): P2SR................................................................................................................121

0x09A – 0x09B: Reserved...............................................................................................................................................122

Port 3 Control Registers......................................................................................................................................................123

Port 3 Control Register 1 (0x09C - 0x09D): P3CR1........................................................................................................123

Port 3 Control Register 2 (0x09E - 0x09F): P3CR2........................................................................................................124

Port 3 VID Control Register (0x0A0 - 0x0A1): P3VIDCR................................................................................................125

Port 3 Control Register 3 (0x0A2 - 0x0A3): P3CR3........................................................................................................125

Port 3 Ingress Rate Control Register 0 (0x0A4 - 0x0A5): P3IRCR0...............................................................................126

Port 3 Ingress Rate Control Register 1 (0x0A6 - 0x0A7): P3IRCR1...............................................................................126

Port 3 Egress Rate Control Register 0 (0x0A8 - 0x0A9): P3ERCR0..............................................................................126

Port 3 Egress Rate Control Register 1 (0x0AA - 0x0AB): P3ERCR1 .............................................................................127

Switch Global Control Registers.........................................................................................................................................128

Switch Global Control Register 8 (0x0AC - 0x0AD): SGCR8..........................................................................................128

Switch Global Control Register 9 (0x0AE - 0x0AF): SGCR9..........................................................................................129

Source Address Filtering Registers ....................................................................................................................................130

Source Address Filtering MAC Address 1 Register Low (0x0B0 - 0x0B1): SAFMACA1L..............................................130

Source Address Filtering MAC Address 1 Register Middle (0x0B2 - 0x0B3): SAFMACA1M.........................................130

Source Address Filtering MAC Address 1 Register High (0x0B4 - 0x0B5): SAFMACA1H ............................................130

Source Address Filtering MAC Address 2 Register Low (0x0B6 - 0x0B7): SAFMACA2L..............................................130

Source Address Filtering MAC Address 2 Register Middle (0x0B8 - 0x0B9): SAFMACA2M.........................................130

Source Address Filtering MAC Address 2 Register High (0x0BA - 0x0BB): SAFMACA2H............................................130

0x0BC - 0x0C7: Reserved...............................................................................................................................................130

TXQ Rate Control Registers ...............................................................................................................................................131

Port 1 TXQ Rate Control Register 1 (0x0C8 - 0x0C9): P1TXQRCR1.............................................................................131

Port 1 TXQ Rate Control Register 2 (0x0CA - 0x0CB): P1TXQRCR2............................................................................131

Port 2 TXQ Rate Control Register 1 (0x0CC - 0x0CD): P2TXQRCR1 ...........................................................................132

Port 2 TXQ Rate Control Register 2 (0x0CE - 0x0CF): P2TXQRCR2............................................................................132

Port 3 TXQ Rate Control Register 1 (0x0D0 - 0x0D1): P3TXQRCR1.............................................................................133

Port 3 TXQ Rate Control Register 2 (0x0D2 - 0x0D3): P3TXQRCR2.............................................................................133

0x0D4 - 0x0DB: Reserved...............................................................................................................................................133

Auto-Negotiation Next Page Registers...............................................................................................................................134

Port 1 Auto-Negotiation Next Page Transmit Register (0x0DC - 0x0DD): P1ANPT.......................................................134

June 23, 2014 9 Revision 1.0

Micrel, Inc.

KSZ8852HLE

Port 1 Auto-Negotiation Link Partner Received Next Page Register (0x0DE - 0x0DF): P1ALPRNP.............................135

EEE and Link Partner Advertisement Registers.................................................................................................................136

Port 1 EEE and Link Partner Advertisement Register (0x0E0 – 0x0E1): P1EEEA.........................................................136

Port 1 EEE Wake Error Count Register (0x0E2 - 0x0E3): P1EEEWEC.........................................................................137

Port 1 EEE Control/Status and Auto-Negotiation Expansion Register (0x0E4 - 0x0E5): P1EEECS..............................137

Port 1 LPI Recovery Time Counter Register (0x0E6): P1LPIRTC..................................................................................139

Buffer Load to LPI Control 1 Register (0x0E7): BL2LPIC1.............................................................................................139

Port 2 Auto−Negotiation Next Page Transmit Register (0x0E8 - 0x0E9): P2ANPT .......................................................139

Port 2 Auto-Negotiation Link Partner Received Next Page Register (0x0EA - 0x0EB): P2ALPRNP.............................140

Port 2 EEE and Link Partner Advertisement Register (0x0EC - 0x0ED): P2EEEA........................................................140

Port 2 EEE Wake Error Count Register (0x0EE - 0x0EF): P2EEEWEC ........................................................................141

Port 2 EEE Control/Status and Auto-Negotiation Expansion Register (0x0F0 - 0x0F1): P2EEECS..............................142

Port 2 LPI Recovery Time Counter Register (0x0F2): P2LPIRTC..................................................................................143

PCS EEE Control Register (0x0F3): PCSEEEC.............................................................................................................144

Empty TXQ to LPI Wait Time Control Register (0x0F4 - 0x0F5): ETLWTC ...................................................................144

Buffer Load to LPI Control 2 Register (0x0F6 - 0x0F7): BL2LPIC2................................................................................144

0x0F8 - 0x0FF: Reserved................................................................................................................................................144

Internal I/O Register Space Mapping for Interrupts, BIU, and Global Reset (0x100 - 0x1FF) ..........................................145

0x100 - 0x107: Reserved ................................................................................................................................................145

Chip Configuration Register (0x108 - 0x109): CCR........................................................................................................145

0x10A - 0x10F: Reserved................................................................................................................................................145

Host MAC Address Registers: MARL, MARM and MARH .................................................................................................146

Host MAC Address Register Low (0x110 - 0x111): MARL .............................................................................................146

Host MAC Address Register Middle (0x112 - 0x113): MARM ........................................................................................146

Host MAC Address Register High (0x114 - 0x115): MARH............................................................................................146

0x116 - 0x121: Reserved ................................................................................................................................................146

EEPROM Control Register (0x122 - 0x123): EEPCR.....................................................................................................147

Memory BIST Info Register (0x124 - 0x125): MBIR........................................................................................................147

Global Reset Register (0x126 - 0x127): GRR.................................................................................................................148

0x128 - 0x129: Reserved ................................................................................................................................................148

Wake-Up Frame Control Register (0x12A - 0x12B): WFCR...........................................................................................149

0x12C - 0x12F: Reserved................................................................................................................................................149

Wake-Up Frame 0 CRC0 Register (0x130 - 0x131): WF0CRC0....................................................................................149

Wake-Up Frame 0 CRC1 Register (0x132- 0x133): WF0CRC1.....................................................................................150

Wake-Up Frame 0 Byte Mask 0 Register (0x134 - 0x135): WF0BM0 ............................................................................150

Wake-Up Frame 0 Byte Mask 1 Register (0x136 - 0x137): WF0BM1 ............................................................................150

Wake-Up Frame 0 Byte Mask 2 Register (0x138 - 0x139): WF0BM2 ............................................................................150

Wake-Up Frame 0 Byte Mask 3 Register (0x13A - 0x13B): WF0BM3 ...........................................................................150

0x13C – 0x13F: Reserved...............................................................................................................................................150

Wake-Up Frame 1 CRC0 Register (0x140 – 0x141): WF1CRC0...................................................................................151

Wake-Up Frame 1 CRC1 Register (0x142 – 0x143): WF1CRC1...................................................................................151

Wake-Up Frame 1 Byte Mask 0 Register (0x144 – 0x145): WF1BM0 ...........................................................................151

Wake-Up Frame 1 Byte Mask 1 Register (0x146 – 0x147): WF1BM1 ...........................................................................151

Wake-Up Frame 1 Byte Mask 2 Register (0x148 – 0x149): WF1BM2 ...........................................................................152

Wake-Up Frame 1 Byte Mask 3 Register (0x14A – 0x14B): WF1BM3...........................................................................152

0x14C – 0x14F: Reserved...............................................................................................................................................152

Wake-Up Frame 2 CRC0 Register (0x150 – 0x151): WF2CRC0...................................................................................152

Wake-Up Frame 2 CRC1 Register (0x152 – 0x153): WF2CRC1...................................................................................152

Wake-Up Frame 2 Byte Mask 0 Register (0x154 – 0x155): WF2BM0 ...........................................................................152

Wake-Up Frame 2 Byte Mask 1 Register (0x156 – 0x157): WF2BM1 ...........................................................................153

Wake-Up Frame 2 Byte Mask 2 Register (0x158 – 0x159): WF2BM2 ...........................................................................153

Wake-Up Frame 2 Byte Mask 3 Register (0x15A – 0x15B): WF2BM3...........................................................................153

0x15C – 0x15F: Reserved...............................................................................................................................................153

Wake-Up Frame 3 CRC0 Register (0x160 – 0x161): WF3CRC0...................................................................................154

Wake-Up Frame 3 CRC1 Register (0x162 – 0x163): WF3CRC1...................................................................................154

Wake-Up Frame 3 Byte Mask 0 Register (0x164 – 0x165): WF3BM0 ...........................................................................154

Wake-Up Frame 3 Byte Mask 1 Register (0x166 – 0x167): WF3BM1 ...........................................................................154

June 23, 2014 10 Revision 1.0

Micrel, Inc.

KSZ8852HLE

Wake-Up Frame 3 Byte Mask 2 Register (0x168 – 0x169): WF3BM2 ...........................................................................154

Wake-Up Frame 3 Byte Mask 3 Register (0x16A - 0x16B): WF3BM3 ...........................................................................155

0x16C – 0x16F: Reserved...............................................................................................................................................155

Internal I/O Register Space Mapping for the Queue Management Unit (QMU) (0x170 - 0x1FF) .....................................156

Transmit Control Register (0x170 - 0x171): TXCR .........................................................................................................156

Transmit Status Register (0x172 - 0x173): TXSR...........................................................................................................157

Receive Control Register 1 (0x174 - 0x175): RXCR1.....................................................................................................157

Receive Control Register 2 (0x176 - 0x177): RXCR2.....................................................................................................158

TXQ Memory Information Register (0x178 - 0x179): TXMIR..........................................................................................159

0x17A - 0x17B: Reserved................................................................................................................................................159

Receive Frame Header Status Register (0x17C - 0x17D): RXFHSR.............................................................................159

Receive Frame Header Byte Count Register (0x17E - 0x17F): RXFHBCR ...................................................................160

TXQ Command Register (0x180 - 0x181): TXQCR........................................................................................................161

RXQ Command Register (0x182 - 0x183): RXQCR.......................................................................................................161

TX Frame Data Pointer Register (0x184 - 0x185): TXFDPR..........................................................................................162

RX Frame Data Pointer Register (0x186 - 0x187): RXFDPR .........................................................................................163

0x188 - 0x18B: Reserved................................................................................................................................................163

RX Duration Timer Threshold Register (0x18C - 0x18D): RXDTTR...............................................................................163

RX Data Byte Count Threshold Register (0x18E - 0x18F): RXDBCTR..........................................................................163

Internal I/O Register Space Mapping for Interrupt Registers (0x190 - 0x193) ...................................................................164

Interrupt Enable Register (0x190 - 0x191): IER..............................................................................................................164

Interrupt Status Register (0x192-– 0x193): ISR..............................................................................................................165

0x194 - 0x19B: Reserved................................................................................................................................................166

Internal I/O Register Space Mapping for the Queue Management Unit (QMU) (0x19C - 0x1B9).....................................167

RX Frame Count and Threshold Register (0x19C -0x19D): RXFCTR............................................................................167

TX Next Total Frames Size Register (0x19E - 0x19F): TXNTFSR.................................................................................167

MAC Address Hash Table Register 0 (0x1A0 - 0x1A1): MAHTR0 .................................................................................167

Multicast Table Register 0 ...........................................................................................................................................167

MAC Address Hash Table Register 1 (0x1A2 - 0x1A3): MAHTR1 .................................................................................168

Multicast Table Register 1 ...........................................................................................................................................168

MAC Address Hash Table Register 2 (0x1A4 - 0x1A5): MAHTR2 .................................................................................168

Multicast Table Register 2 ...........................................................................................................................................168

MAC Address Hash Table Register 3 (0x1A6 - 0x1A7): MAHTR3 .................................................................................168

Multicast Table Register 3 ...........................................................................................................................................168

0x1A8 - 0x1AF: Reserved ...............................................................................................................................................168

Flow Control Low Water Mark Register (0x1B0 - 0x1B1): FCLWR.................................................................................168

Flow Control High Water Mark Register (0x1B2 - 0x1B3): FCHWR...............................................................................169

Flow Control Overrun Water Mark Register (0x1B4 - 0x1B5): FCOWR .........................................................................169

0x1B6 - 0x1B7: Reserved RX Frame Count Register (0x1B8 - 0x1B9): RXFC..............................................................169

0x1BA - 0x747: Reserved................................................................................................................................................170

Analog Control 1 Register (0x748 - 0x749): ANA_CNTRL_1 .........................................................................................170

0x74A - 0x74B: Reserved................................................................................................................................................170

Analog Control 3 Register (0x74C - 0x74D): ANA_CNTRL_3........................................................................................170

0x74E - 0x7FF: Reserved................................................................................................................................................170

Management Information Base (MIB) Counters .................................................................................................................171

MIB Counter Examples:...................................................................................................................................................173

Additional MIB Information ..............................................................................................................................................173

Static MAC Address Table..................................................................................................................................................174

Static MAC Table Lookup Examples:..............................................................................................................................175

Dynamic MAC Address Table.............................................................................................................................................176

Dynamic MAC Address Lookup Example: ......................................................................................................................176

VLAN Table.........................................................................................................................................................................177

VLAN Table Lookup Examples: ......................................................................................................................................177

Absolute Maximum Ratings(2) .............................................................................................................................................178

Operating Ratings(3) ............................................................................................................................................................178

Electrical Characteristics(5)..................................................................................................................................................178

Timing Specifications..........................................................................................................................................................183

June 23, 2014 11 Revision 1.0

Micrel, Inc.

KSZ8852HLE

Host Interface Read / Write Timing.................................................................................................................................183

Auto−Negotiation Timing .................................................................................................................................................184

Serial EEPROM Interface Timing....................................................................................................................................185

Reset Timing and Power Sequencing.................................................................................................................................186

Reset Circuit Guidelines......................................................................................................................................................187

Reference Circuits – LED Strap-In Pins..............................................................................................................................188

Reference Clock – Connection and Selection ....................................................................................................................189

Selection of Reference Crystal............................................................................................................................................189

Selection of Isolation Transformers ....................................................................................................................................190

Package Information(11) and Recommended Landing Pattern............................................................................................191

June 23, 2014 12 Revision 1.0

Micrel, Inc.

KSZ8852HLE

List of Figures

Figure 1. Typical Straight Cable Connection ........................................................................................................................26

Figure 2. Typical Crossover Cable Connection ....................................................................................................................27

Figure 3. Auto-Negotiation and Parallel Operation...............................................................................................................28

Figure 4. Near-End and Far-End Loopback..........................................................................................................................30

Figure 5. Destination Address Lookup Flow Chart in Stage One.........................................................................................32

Figure 6. Destination Address Resolution Flow Chart in Stage Two....................................................................................33

Figure 7. Tail Tag Frame Format..........................................................................................................................................38

Figure 8. 802.1p Priority Field Format ..................................................................................................................................41

Figure 9. Host TX Single Frame in Manual Enqueue Flow Diagram....................................................................................46

Figure 10. Host RX Single or Multiple Frames in Auto-Dequeue Flow Diagram..................................................................49

Figure 11. Recommended Low-Voltage Power Connection using an External Low-Voltage-Regulator..............................51

Figure 12. Recommended Low-Voltage Power Connections using the Internal Low-Voltage Regulator ............................52

Figure 13. Traffic Activity and EEE .......................................................................................................................................54

Figure 14. KSZ8852 8-Bit and 16-Bit Data Bus Connections...............................................................................................59

Figure 15. Interface and Register Mapping...........................................................................................................................61

Figure 16. Host Interface Read/Write Timing......................................................................................................................183

Figure 17. Auto-Negotiation Timing....................................................................................................................................184

Figure 18. Serial EEPROM Timing.....................................................................................................................................185

Figure 19. KSZ8852 Reset and Power Sequence Timing..................................................................................................186

Figure 20. Sample Reset Circuit.........................................................................................................................................187

Figure 21. Recommended Reset Circuit for Interfacing with a CPU/FPGA Reset Output.................................................187

Figure 22. Typical LED Strap-In Circuit ..............................................................................................................................188

Figure 23. 25MHz Crystal and Oscillator Clock Connections.............................................................................................189

June 23, 2014 13 Revision 1.0

Micrel, Inc.

KSZ8852HLE

List of Tables

Table 1. MDI/MDI-X Pin Definitions ......................................................................................................................................26

Table 2. MAC Address Filtering Scheme..............................................................................................................................36

Table 3. Spanning Tree States.............................................................................................................................................37

Table 4. Tail Tag Rules.........................................................................................................................................................39

Table 5. FID + DA Lookup in VLAN Mode............................................................................................................................40

Table 6. FID + SA Lookup in VLAN Mode............................................................................................................................41

Table 7. Frame Format for Transmit Queue.........................................................................................................................44

Table 8. Transmit Control Word Bit Fields............................................................................................................................44

Table 9. Transmit Byte Count Format...................................................................................................................................45

Table 10. Register Setting for Transmit Function Block .......................................................................................................45

Table 11. Frame Format for Receive Queue........................................................................................................................47

Table 12. Register Settings for Receive Function Block.......................................................................................................48

Table 13. KSZ8852 Device Clocks.......................................................................................................................................50

Table 14. Voltage Options and Requirements......................................................................................................................51

Table 15. Power Management and Internal Blocks..............................................................................................................53

Table 16. Available Interfaces...............................................................................................................................................57

Table 17. Bus Interface Unit Signal Grouping.......................................................................................................................58

Table 18. KSZ8852 Serial EEPROM Format........................................................................................................................60

Table 19. Mapping of Functional Areas within the Address Space ......................................................................................62

Table 20. Ingress or Egress Data Rate Limits....................................................................................................................106

Table 21. Format of Per-Port MIB Counters.......................................................................................................................171

Table 22. Port 1 MIB Counters - Indirect Memory Offset....................................................................................................172

Table 23. "All Ports Dropped Packet" MIB Counter Format ...............................................................................................173

Table 24. "All Ports Dropped Packet" MIB Counters− Indirect Memory Offsets.................................................................173

Table 25. Static MAC Table Format (8 Entries)..................................................................................................................174

Table 26. Dynamic MAC Address Table Format (1024 Entries)........................................................................................176

Table 27. VLAN Table Format (16 Entries).........................................................................................................................177

Table 28. Host Interface Read/Write Timing Parameters...................................................................................................183

Table 29. Auto-Negotiation Timing Parameters..................................................................................................................184

Table 30. Serial EEPROM Timing Parameters...................................................................................................................185

Table 31. Reset Timing Parameters(8, 9, 10)..........................................................................................................................186

Table 32. Typical Reference Crystal Characteristics..........................................................................................................189

Table 33. Transformer Selection Criteria............................................................................................................................190

Table 34. Qualified Single Port Magnetic............................................................................................................................190

June 23, 2014 14 Revision 1.0

Micrel, Inc.

KSZ8852HLE

Acronyms

BIU Bus Interface Unit The host interface function that performs code conversion,

buffering, and the like required for communications to and from a

network.

BPDU Bridge Protocol Data Unit A packet containing ports, addresses, etc. to make sure data being

passed through a bridged network arrives at its proper destination.

CMOS Complementary Metal

Oxide Semiconductor A common semiconductor manufacturing technique in which

positive and negative types of transistors are combined to form a

current gate that in turn forms an effective means of controlling

electrical current through a chip.

CRC Cyclic Redundancy Check A common technique for detecting data transmission errors. CRC

for Ethernet is 32 bits long.

CUT-THROUGH SWITCH A switch typically processes received packets by reading in the full

packet (storing), then processing the packet to determine where it

needs to go, then forwarding it. A cut−through switch simply reads

in the first bit of an incoming packet and forwards the packet.

Cut−through switches do not store the packet.

DA

Destination Address The address to send packets.

DMA Direct Memory Access A design in which memory on a chip is controlled independently of

the CPU.

EMI Electromagnetic Interference A naturally occurring phenomena when the electromagnetic field of

one device disrupts, impedes or degrades the electromagnetic field

of another device by coming into proximity with it. In computer

technology, computer devices are susceptible to EMI because

electromagnetic fields are a byproduct of passing electricity through

a wire. Data lines that have not been properly shielded are

susceptible to data corruption by EMI.

FCS Frame Check Sequence See CRC.

FID

Frame or Filter ID Specifies the frame identifier. Alternately is the filter identifier.

IGMP Internet Group Management

Protocol The protocol defined by RFC 1112 for IP multicast transmissions.

IPG Inter-Packet Gap A time delay between successive data packets mandated by the

network standard for protocol reasons. In Ethernet, the medium has

to be "silent" (i.e., no data transfer) for a short period of time before

a node can consider the network idle and start to transmit. IPG is

used to correct timing differences between a transmitter and

receiver. During the IPG, no data is transferred, and information in

the gap can be discarded or additions inserted without impact on

data integrity.

ISI Inter-Symbol Interference The disruption of transmitted code caused by adjacent pulses

affecting or interfering with each other.

ISA Industry Standard Architecture A bus architecture used in the IBM PC/XT and PC/AT.

JUMBO PACKET A packet larger than the standard Ethernet packet (1500 bytes).

Large packet sizes allow for more efficient use of bandwidth, lower

overhead, less processing, etc.

MAC Media Access Controller A functional block responsible for implementing the Media Access

Control layer which is a sub layer of the Data Link Layer.