Micrel KSZ8862-16MQL User manual

KSZ8862-16/32MQL

2-Port Ethernet Switch with Non-PCI Interface

and Fiber Support

Rev 3.1

LinkMD is a registered trademark of Micrel, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

August 2010 M9999-081310-3.1

General Description

The KSZ8862M is 2-port switch with non-PCI CPU

interface and fiber support, and is available in 8/16-bit

and 32-bit bus designs (see Ordering Information). This

datasheet describes the KSZ8862M non-PCI CPU

interface chip.

The KSZ8862M is the industry’s first fully managed, 2-

port switch with a non-PCI CPU interface and fiber

support. It is based on a proven, 4th generation,

integrated Layer-2 switch, compliant with IEEE 802.3u

standards.

For industrial applications, the KSZ8862M can run in

half-duplex mode regardless of the application.

In fiber mode, port 1 can be configurable to either

100BASE-FX or 100BASE-SX/10BASE-FL.

The LED driver and post amplifier are also included for

10Base-FL and 100Base-SX applications.

LinkMD®

In copper mode, port 2 supports 10/100BASE-T/TX with

HP Auto MDI/MDI-X for reliable detection of and

correction for straight-through and crossover cables.

Micrel’s proprietary LinkMD®Time Domain

Reflectometry (TDR)-based function is also available for

determining the cable length, as well as cable

diagnostics for identifying faulty cabling.

The KSZ8862M offers an extensive feature set that

includes tag/port-based VLAN, quality of service (QoS)

priority management, management information base

(MIB) counters, and CPU control/data interfaces to

effectively address Fast Ethernet applications.

The KSZ8862M contains: Two 10/100 transceivers with

patented, mixed-signal, low-power technology, two

media access control (MAC) units, a direct memory

access (DMA) channel, a high-speed, non-blocking,

switch fabric, a dedicated 1K entry forwarding table, and

an on-chip frame buffer memory.

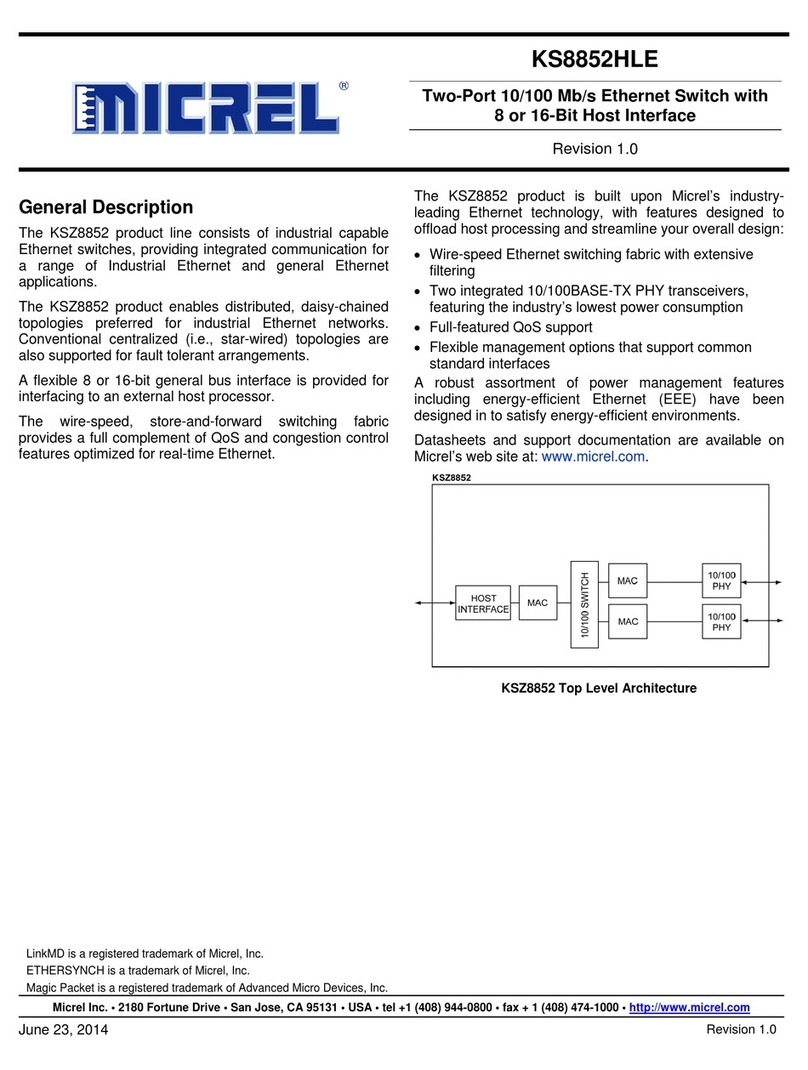

Functional Diagram

Port 1

Fiber

Port 2

Copper

Embedded

ProcessorInterface

1K look-up

Engine

Scheduling

Management

Buffer

Management

Frame

Buffers

FIFO, Flow Control, VLAN Tagging ,Priority

10/100

MAC 1

10/100

MAC 2

Switch

Host

MAC

10/100 Base-

T/TX

PHY 2

EEPROM

Interface

LED

Drivers

MIB

Counters

P1 LED[3:0]

P2 LED[3:0]

EEPROM I/F

Non-PCI

CPU

Bus

Interface

Unit

QMU

DMA

Channel

Control

Registers

RXQ

4KB

8,16, or 32-bit

Generic Host

Interface

TXQ

4KB

10/100 Base-

FL/FX/SX

PHY 1

LED

Driver

Post

Amp

TX

RX

Figure 1. KSZ8862M Functional Diagram

Micrel, Inc. KSZ8862-16/32MQL

August 2010

2 M9999-081310-3.1

Features

Switch Management

•Non-blocking switch fabric assures fast packet

delivery by utilizing a 1K entry forwarding table and a

store-and-forward architecture

•Fully compliant with IEEE 802.3u standards

•Full-duplex IEEE 802.3x flow control (Pause) with

force mode option

•Half-duplex back pressure flow control

Advanced Switch Management

•IEEE 802.1Q VLAN support for up to 16 groups (full

range of VLAN IDs)

•VLAN ID tag/untag options, on a per port basis

•IEEE 802.1p/Q tag insertion or removal on a per port

basis (egress)

•Programmable rate limiting at the ingress and egress

ports

•Broadcast storm protection

•IEEE 802.1d spanning tree protocol support

•MAC filtering function to filter or forward unknown

unicast packets

•Direct forwarding mode enabling the processor to

identify the ingress port and to specify the egress port

•Internet Group Management Protocol (IGMP) v1/v2

snooping support for multicast packet filtering

•IPV6 Multicast Listener Discovery (MLD) snooping

support

Fiber Support

•Integrated LED driver and post amplifier for 10BASE-

FL and 100BASE-SX optical modules

•100BASE-FX/SX and 10BASE-FL fiber support on

port 1

Monitoring

•Port mirroring/monitoring/sniffing: ingress and/or

egress traffic to any port

•MIB counters for fully compliant statistics gathering –

34 MIB counters per port

•Loopback modes for remote failure diagnostics

Comprehensive Register Access

•Control registers configurable on-the-fly (port-priority,

802.1p/d/Q)

QoS/CoS Packets Prioritization Support

•Per port, 802.1p and DiffServ-based

•Remapping of 802.1p priority field on a per port basis

Power Modes, Packaging, and Power Supplies

•Full-chip hardware power-down (register configuration

not saved) allows low power dissipation

•Per port-based, software power-save on PHY (idle

link detection, register configuration preserved)

•Single power supply: 3.3V

•Commercial Temperature Range: 0oC to +70oC

•Industrial Temperature Range: –40oC to +85oC

(see Ordering Information).

•Available in 128-pin PQFP

•Available in –16 version for 8/16-bit bus support and –

32 version for 32-bit bus support (see Ordering

Information).

Additional Features

In addition to offering all of the features of an integrated

Layer-2 managed switch, the KSZ8862M offers:

•Dynamic buffer memory scheme

– Essential for applications such as Video over IP

where image jitter is unacceptable

•2-port switch with a flexible 8, 16, or 32-bit generic

host processor interfaces

•Micrel LinkMD®cable diagnostics to determine cable

length, diagnose faulty cables, and determine

distance-to-fault

•Hewlett Packard (HP) Auto-MDIX crossover with

disable and enable options

•Four priority queues to handle voice, video, data, and

control packets

•Ability to transmit and receive jumbo frame sizes up to

1916 bytes

Applications

•Video Distribution Systems

•High-end Cable, Satellite, and IP set-top boxes

•Video over IP

•Voice over IP (VoIP) and Analog Telephone Adapters

(ATA)

•Industrial Control in Latency Critical Applications

•Motion Control

•Industrial Control Sensor Devices (Temperature,

Pressure, Levels, and Valves)

•Security and Surveillance Cameras

Markets

•Fast Ethernet

•Embedded Ethernet

•Industrial Ethernet

Micrel, Inc. KSZ8862-16/32MQL

August 2010

3 M9999-081310-3.1

Ordering Information

Part Number Temperature Range Package Comment

KSZ8862-16MQL-FX 0oC to 70oC128-Pin PQFP Port 1 operates on 100BASE-FX mode only

KSZ8862-16MQL 0oC to 70oC128-Pin PQFP Port 1 operates on 10BASE-FL or

100BASE-SX mode only

KSZ8862-32MQL-FX 0oC to 70oC128-Pin PQFP Port 1 operates on 100BASE-FX mode only

KSZ8862-32MQL 0oC to 70oC128-Pin PQFP Port 1 operates on 10BASE-FL or

100BASE-SX mode only

KSZ8862-100FX-EVAL Evaluation Board for the KSZ8862-16MQL at 100FX Mode

KSZ8862-10FL-EVAL Evaluation Board for the KSZ8862-16MQL at 100SX_10FL Mode

Revision History

Revision Date Summary of Changes

1.0 07/18/06 First released Information

2.0 09/13/06 Added evaluation ordering info. to Ordering Information Table

3.0 04/04/07 Updated part ordering info. to Ordering Information Table

Improve the ARDY low time in read cycle to 40ns and in write cycle to 50 ns during QMU

data register access

3.1 8/13/10 Changed the FL/SX part order information

Micrel, Inc. KSZ8862-16/32MQL

August 2010

4 M9999-081310-3.1

Content

General Description........................................................................................................................................................1

Functional Diagram.........................................................................................................................................................1

Features ...........................................................................................................................................................................2

Applications.....................................................................................................................................................................2

Markets.............................................................................................................................................................................2

Ordering Information ......................................................................................................................................................3

Revision History..............................................................................................................................................................3

Content.............................................................................................................................................................................4

List of Figures..................................................................................................................................................................9

List of Tables.................................................................................................................................................................10

Pin Configuration for KSZ8862-16MQL (8/16-Bit)......................................................................................................11

Pin Description for KSZ8862-16MQL (8/16-Bit)..........................................................................................................12

Pin Configuration for KSZ8862-32MQL (32-Bit).........................................................................................................17

Pin Description for KSZ8862-32 MQL (32-Bit)............................................................................................................18

Functional Description .................................................................................................................................................23

Functional Overview: Physical Layer Transceiver....................................................................................................23

100BASE-TX Transmit.............................................................................................................................................................23

100BASE-TX Receive..............................................................................................................................................................23

Scrambler/De-scrambler (100BASE-TX only)..........................................................................................................................23

100BASE-FX Operation...........................................................................................................................................................23

100BASE-FX Signal Detection.................................................................................................................................................23

100BASE-FX Far-End-Fault (FEF) ..........................................................................................................................................24

100BASE-SX Operation...........................................................................................................................................................24

Physical Interface................................................................................................................................................................24

Enabling 100BASE-SX Mode..............................................................................................................................................24

Enabling Fiber Forced Mode ..............................................................................................................................................24

10BASE-FL Operation.............................................................................................................................................................24

Physical Interface................................................................................................................................................................24

Enabling 10BASE-FL Mode ................................................................................................................................................24

Enabling Fiber Forced Mode ..............................................................................................................................................24

10BASE-T Transmit.................................................................................................................................................................25

10BASE-T Receive..................................................................................................................................................................25

LED Driver ...............................................................................................................................................................................25

Post Amplifier...........................................................................................................................................................................25

Power Management.................................................................................................................................................................25

MDI/MDI-X Auto Crossover......................................................................................................................................................25

Straight Cable......................................................................................................................................................................26

Crossover Cable..................................................................................................................................................................26

Auto Negotiation ......................................................................................................................................................................27

LinkMD®Cable Diagnostics.....................................................................................................................................................28

Access..................................................................................................................................................................................28

Usage....................................................................................................................................................................................28

Functional Overview: MAC and Switch ......................................................................................................................29

Address Lookup.......................................................................................................................................................................29

Learning...................................................................................................................................................................................29

Migration..................................................................................................................................................................................29

Aging........................................................................................................................................................................................29

Forwarding...............................................................................................................................................................................30

Switching Engine .....................................................................................................................................................................32

MAC Operation........................................................................................................................................................................32

Micrel, Inc. KSZ8862-16/32MQL

August 2010

5 M9999-081310-3.1

Inter Packet Gap (IPG) ............................................................................................................................................................32

Back-Off Algorithm...................................................................................................................................................................32

Late Collision ...........................................................................................................................................................................32

Legal Packet Size....................................................................................................................................................................32

Flow Control.............................................................................................................................................................................32

Half-Duplex Backpressure .......................................................................................................................................................32

Broadcast Storm Protection.....................................................................................................................................................33

Clock Generator.......................................................................................................................................................................33

Bus Interface Unit (BIU)................................................................................................................................................33

Asynchronous Interface...........................................................................................................................................................35

Synchronous Interface.............................................................................................................................................................36

Summary..................................................................................................................................................................................36

BIU Implementation Principles.................................................................................................................................................37

Queue Management Unit (QMU)..................................................................................................................................38

Transmit Queue (TXQ) Frame Format.....................................................................................................................................38

Receive Queue (RXQ) Frame Format .....................................................................................................................................39

Advanced Switch Functions........................................................................................................................................41

Spanning Tree Support............................................................................................................................................................41

IGMP Support..........................................................................................................................................................................42

“IGMP” Snooping...................................................................................................................................................................42

“Multicast Address Insertion” in the Static MAC Table...........................................................................................................42

IPv6 MLD Snooping.................................................................................................................................................................42

Port Mirroring Support..............................................................................................................................................................42

IEEE 802.1Q VLAN Support....................................................................................................................................................43

QoS Priority Support................................................................................................................................................................43

Port-Based Priority...................................................................................................................................................................43

802.1p-Based Priority ..............................................................................................................................................................43

DiffServ-Based Priority.............................................................................................................................................................44

Rate Limiting Support ..............................................................................................................................................................44

MAC Filtering Function ............................................................................................................................................................45

Configuration Interface.............................................................................................................................................................45

EEPROM Interface ..................................................................................................................................................................45

Loopback Support....................................................................................................................................................................46

Far-end Loopback ...............................................................................................................................................................46

Near-end (Remote) Loopback.............................................................................................................................................46

CPU Interface I/O Registers .........................................................................................................................................48

I/O Registers............................................................................................................................................................................48

Internal I/O Space Mapping .....................................................................................................................................................49

Register Map: Switch and MAC/PHY...........................................................................................................................57

Bit Type Definition....................................................................................................................................................................57

Bank 0-63 Bank Select Register (0x0E): BSR (same location in all Banks).............................................................................57

Bank 0 Base Address Register (0x00): BAR............................................................................................................................57

Bank 0 QMU RX Flow Control High Watermark Configuration Register (0x04): QRFCR........................................................57

Bank 0 Bus Error Status Register (0x06): BESR .....................................................................................................................58

Bank 0 Bus Burst Length Register (0x08): BBLR.....................................................................................................................58

Bank 1 Reserved .....................................................................................................................................................................58

Bank 2 Host MAC Address Register Low (0x00): MARL .........................................................................................................58

Bank 2 Host MAC Address Register Middle (0x02): MARM.....................................................................................................59

Bank 2 Host MAC Address Register High (0x04): MARH........................................................................................................59

Bank 3 On-Chip Bus Control Register (0x00): OBCR..............................................................................................................59

Bank 3 EEPROM Control Register (0x02): EEPCR.................................................................................................................60

Bank 3 Memory BIST INFO Register (0x04): MBIR.................................................................................................................60

Micrel, Inc. KSZ8862-16/32MQL

August 2010

6 M9999-081310-3.1

Bank 3 Global Reset Register (0x06): GRR.............................................................................................................................60

Bank 3 Bus Configuration Register (0x08): BCFG...................................................................................................................61

Banks 4 – 15: Reserved...........................................................................................................................................................61

Bank 16 Transmit Control Register (0x00): TXCR...................................................................................................................61

Bank 16 Transmit Status Register (0x02): TXSR.....................................................................................................................61

Bank 16 Receive Control Register (0x04): RXCR....................................................................................................................62

Bank 16 TXQ Memory Information Register (0x08): TXMIR....................................................................................................62

Bank 16 RXQ Memory Information Register (0x0A): RXMIR...................................................................................................63

Bank 17 TXQ Command Register (0x00): TXQCR..................................................................................................................63

Bank 17 RXQ Command Register (0x02): RXQCR.................................................................................................................63

Bank 17 TX Frame Data Pointer Register (0x04): TXFDPR....................................................................................................63

Bank 17 RX Frame Data Pointer Register (0x06): RXFDPR....................................................................................................64

Bank 17 QMU Data Register Low (0x08): QDRL.....................................................................................................................64

Bank 17 QMU Data Register High (0x0A): QDRH...................................................................................................................64

Bank 18 Interrupt Enable Register (0x00): IER........................................................................................................................65

Bank 18 Interrupt Status Register (0x02): ISR.........................................................................................................................66

Bank 18 Receive Status Register (0x04): RXSR .....................................................................................................................67

Bank 18 Receive Byte Counter Register (0x06): RXBC...........................................................................................................67

Bank 19 Multicast Table Register 0 (0x00): MTR0...................................................................................................................68

Bank 19 Multicast Table Register 1 (0x02): MTR1...................................................................................................................68

Bank 19 Multicast Table Register 2 (0x04): MTR2...................................................................................................................68

Bank 19 Multicast Table Register 3 (0x06): MTR3...................................................................................................................68

Banks 20 – 31: Reserved.........................................................................................................................................................68

Bank 32 Switch ID and Enable Register (0x00): SIDER..........................................................................................................69

Bank 32 Switch Global Control Register 1 (0x02): SGCR1......................................................................................................69

Bank 32 Switch Global Control Register 2 (0x04): SGCR2......................................................................................................70

Bank 32 Switch Global Control Register 3 (0x06): SGCR3......................................................................................................71

Bank 32 Switch Global Control Register 4 (0x08): SGCR4......................................................................................................71

Bank 32 Switch Global Control Register 5 (0x0A): SGCR5 .....................................................................................................72

Bank 33 Switch Global Control Register 6 (0x00): SGCR6......................................................................................................73

Bank 33 Switch Global Control Register 7 (0x02): SGCR7......................................................................................................73

Banks 34 – 38: Reserved.........................................................................................................................................................73

Bank 39 MAC Address Register 1 (0x00): MACAR1 ...............................................................................................................74

Bank 39 MAC Address Register 2 (0x02): MACAR2 ...............................................................................................................74

Bank 39 MAC Address Register 3 (0x04): MACAR3 ...............................................................................................................74

Bank 40 TOS Priority Control Register 1 (0x00): TOSR1 ........................................................................................................74

Bank 40 TOS Priority Control Register 2 (0x02): TOSR2 ........................................................................................................75

Bank 40 TOS Priority Control Register 3 (0x04): TOSR3 ........................................................................................................75

Bank 40 TOS Priority Control Register 4 (0x06): TOSR4 ........................................................................................................76

Bank 40 TOS Priority Control Register 5 (0x08): TOSR5 ........................................................................................................76

Bank 40 TOS Priority Control Register 6 (0x0A): TOSR6........................................................................................................77

Bank 41 TOS Priority Control Register 7 (0x00): TOSR7 ........................................................................................................77

Bank 41 TOS Priority Control Register 8 (0x02): TOSR8 ........................................................................................................78

Bank 42 Indirect Access Control Register (0x00): IACR..........................................................................................................78

Bank 42 Indirect Access Data Register 1 (0x02): IADR1.........................................................................................................79

Bank 42 Indirect Access Data Register 2 (0x04): IADR2.........................................................................................................79

Bank 42 Indirect Access Data Register 3 (0x06): IADR3.........................................................................................................79

Bank 42 Indirect Access Data Register 4 (0x08): IADR4.........................................................................................................79

Bank 42 Indirect Access Data Register 5 (0x0A): IADR5.........................................................................................................79

Bank 43: Reserved ..................................................................................................................................................................79

Bank 44 Digital Testing Status Register (0x00): DTSR............................................................................................................80

Bank 44 Analog Testing Status Register (0x02): ATSR...........................................................................................................80

Micrel, Inc. KSZ8862-16/32MQL

August 2010

7 M9999-081310-3.1

Bank 44 Digital Testing Control Register (0x04): DTCR ..........................................................................................................80

Bank 44 Analog Testing Control Register 0 (0x06): ATCR0....................................................................................................80

Bank 44 Analog Testing Control Register 1 (0x08): ATCR1....................................................................................................80

Bank 44 Analog Testing Control Register 2 (0x0A): ATCR2....................................................................................................80

Bank 45 PHY 1 MII-Register Basic Control Register (0x00): P1MBCR ...................................................................................80

Bank 45 PHY 1 MII-Register Basic Status Register (0x02): P1MBSR.....................................................................................82

Bank 45 PHY 1 PHYID Low Register (0x04): PHY1ILR...........................................................................................................82

Bank 45 PHY 1 PHYID High Register (0x06): PHY1IHR.........................................................................................................82

Bank 45 PHY 1 Auto-Negotiation Advertisement Register (0x08): P1ANAR...........................................................................83

Bank 45 PHY 1 Auto-Negotiation Link Partner Ability Register (0x0A): P1ANLPR..................................................................83

Bank 46 PHY 2 MII-Register Basic Control Register (0x00): P2MBCR ...................................................................................84

Bank 46 PHY 2 MII-Register Basic Status Register (0x02): P2MBSR.....................................................................................85

Bank 46 PHY 2 PHYID Low Register (0x04): PHY2ILR...........................................................................................................85

Bank 46 PHY 2 PHYID High Register (0x06): PHY2IHR.........................................................................................................85

Bank 46 PHY 2 Auto-Negotiation Advertisement Register (0x08): P2ANAR...........................................................................86

Bank 46 PHY 2 Auto-Negotiation Link Partner Ability Register (0x0A): P2ANLPR..................................................................86

Bank 47 PHY1 Special Control/Status Register (0x02): P1PHYCTRL.....................................................................................87

Bank 47 PHY2 LinkMD®Control/Status (0x04): P2VCT..........................................................................................................87

Bank 47 PHY2 Special Control/Status Register (0x06): P2PHYCTRL.....................................................................................88

Bank 48 Port 1 Control Register 1 (0x00): P1CR1...................................................................................................................88

Bank 48 Port 1 Control Register 2 (0x02): P1CR2...................................................................................................................89

Bank 48 Port 1 VID Control Register (0x04): P1VIDCR...........................................................................................................90

Bank 48 Port 1 Control Register 3 (0x06): P1CR3...................................................................................................................90

Bank 48 Port 1 Ingress Rate Control Register (0x08): P1IRCR...............................................................................................91

Bank 48 Port 1 Egress Rate Control Register (0x0A): P1ERCR..............................................................................................93

Bank 49 Port 1 PHY Special Control/Status, LinkMD®(0x00): P1SCSLMD ............................................................................95

Bank 49 Port 1 Control Register 4 (0x02): P1CR4...................................................................................................................95

Bank 49 Port 1 Status Register (0x04): P1SR.........................................................................................................................96

Bank 50 Port 2 Control Register 1 (0x00): P2CR1...................................................................................................................97

Bank 50 Port 2 Control Register 2 (0x02): P2CR2...................................................................................................................97

Bank 50 Port 2 VID Control Register (0x04): P2VIDCR...........................................................................................................97

Bank 50 Port 2 Control Register 3 (0x06): P2CR3...................................................................................................................97

Bank 50 Port 2 Ingress Rate Control Register (0x08): P2IRCR...............................................................................................97

Bank 50 Port 2 Egress Rate Control Register (0x0A): P2ERCR..............................................................................................97

Bank 51 Port 2 PHY Special Control/Status, LinkMD®(0x00): P2SCSLMD ............................................................................98

Bank 51 Port 2 Control Register 4 (0x02): P2CR4...................................................................................................................99

Bank 51 Port 2 Status Register (0x04): P2SR.......................................................................................................................100

Bank 52 Host Port Control Register 1 (0x00): P3CR1 ...........................................................................................................101

Bank 52 Host Port Control Register 2 (0x02): P3CR2 ...........................................................................................................101

Bank 52 Host Port VID Control Register (0x04): P3VIDCR....................................................................................................102

Bank 52 Host Port Control Register 3 (0x06): P3CR3 ...........................................................................................................102

Bank 52 Host Port Ingress Rate Control Register (0x08): P3IRCR........................................................................................102

Bank 52 Host Port Egress Rate Control Register (0x0A): P3ERCR ......................................................................................102

Banks 53 – 63: Reserved.......................................................................................................................................................102

MIB (Management Information Base) Counters.......................................................................................................103

Format of “All Ports Dropped Packet” MIB Counters .............................................................................................................104

Additional MIB Information.....................................................................................................................................................105

Static MAC Address Table .........................................................................................................................................106

Static MAC Table Lookup Examples: 106

Dynamic MAC Address Table ....................................................................................................................................107

Dynamic MAC Address Lookup Example:.............................................................................................................................107

Micrel, Inc. KSZ8862-16/32MQL

August 2010

8 M9999-081310-3.1

VLAN Table ..................................................................................................................................................................108

VLAN Table Lookup Examples:.............................................................................................................................................108

Absolute Maximum Ratings(1) ....................................................................................................................................109

Operating Ratings(1) ....................................................................................................................................................109

Electrical Characteristics(1) ........................................................................................................................................110

Timing Specifications.................................................................................................................................................111

Asynchronous Timing without using Address Strobe (ADSN = 0)..........................................................................................111

Asynchronous Timing Using Address Strobe (ADSN)...........................................................................................................112

Asynchronous Timing Using DATACSN ................................................................................................................................113

Address Latching Timing for All Modes..................................................................................................................................114

Synchronous Timing in Burst Write (VLBUSN = 1)................................................................................................................115

Synchronous Timing in Burst Read (VLBUSN = 1)................................................................................................................116

Synchronous Write Timing (VLBUSN = 0).............................................................................................................................117

Synchronous Read Timing (VLBUSN = 0).............................................................................................................................118

EEPROM Timing....................................................................................................................................................................119

Auto Negotiation Timing.........................................................................................................................................................120

Reset Timing..........................................................................................................................................................................121

Selection of Isolation Transformers..........................................................................................................................122

Selection of Reference Crystal..................................................................................................................................122

Package Information...................................................................................................................................................123

Acronyms and Glossary.............................................................................................................................................124

Micrel, Inc. KSZ8862-16/32MQL

August 2010

9 M9999-081310-3.1

List of Figures

Figure 1. KSZ8862M Functional Diagram....................................................................................................................................1

Figure 2. Standard – KSZ8862-16 MQL 128-Pin PQFP (Top View)......................................................................................11

Figure 3. Standard – KSZ8862-32 MQL 128-Pin PQFP (Top View)......................................................................................17

Figure 4. Typical Straight Cable Connection .............................................................................................................................26

Figure 5. Typical Crossover Cable Connection.........................................................................................................................26

Figure 6. Auto Negotiation and Parallel Operation....................................................................................................................27

Figure 7. Destination Address Lookup Flow Chart in Stage One...........................................................................................30

Figure 8. Destination Address Resolution Flow Chart in Stage Two......................................................................................31

Figure 9. Mapping from ISA-like, EISA-like, and VLBus-like transactions to the KSZ8862M Bus.....................................36

Figure 10. KSZ8862M 8-Bit, 16-Bit, and 32-Bit Data Bus Connections.................................................................................37

Figure 11. 802.1p Priority Field Format......................................................................................................................................44

Figure 12. Port 2 Far-End Loopback Path..................................................................................................................................47

Figure 13. Port 1 and port 2 Near-End (Remote) Loopback Path ..........................................................................................47

Figure 14. Asynchronous Cycle – ADSN = 0...........................................................................................................................111

Figure 15. Asynchronous Cycle – Using ADSN ......................................................................................................................112

Figure 16. Asynchronous Cycle – Using DATACSN ..............................................................................................................113

Figure 17. Address Latching Cycle for All Modes ...................................................................................................................114

Figure 18. Synchronous Burst Write Cycles – VLBUSN = 1 .................................................................................................115

Figure 19. Synchronous Burst Read Cycles – VLBUSN = 1.................................................................................................116

Figure 20. Synchronous Write Cycle – VLBUSN = 0..............................................................................................................117

Figure 21. Synchronous Read Cycle – VLBUSN = 0 .............................................................................................................118

Figure 22. EEPROM Read Cycle Timing Diagram .................................................................................................................119

Figure 23. Auto-Negotiation Timing...........................................................................................................................................120

Figure 24. Reset Timing..............................................................................................................................................................121

Figure 25. 128-Pin PQFP Package...........................................................................................................................................123

Micrel, Inc. KSZ8862-16/32MQL

August 2010

10 M9999-081310-3.1

List of Tables

Table 1. MDI/MDI-X Pin Definitions..................................................................................................................................................25

Table 2. Bus Interface Unit Signal Grouping ....................................................................................................................................35

Table 3. Transmit Queue Frame Format..........................................................................................................................................38

Table 4. Transmit Control Word Bit Fields........................................................................................................................................38

Table 5. Transmit Byte Count Format ..............................................................................................................................................39

Table 6. Receive Queue Frame Format...........................................................................................................................................39

Table 7. FRXQ Packet Receive Status.............................................................................................................................................40

Table 8. FRXQ RX Byte Count Field................................................................................................................................................40

Table 9. Spanning Tree States.........................................................................................................................................................41

Table 10. FID+DA Lookup in VLAN Mode........................................................................................................................................43

Table 11. FID+SA Lookup in VLAN Mode........................................................................................................................................43

Table 12. EEPROM Format..............................................................................................................................................................45

Table 13. ConfigParam Word in EEPROM Format ..........................................................................................................................46

Table 14. Format of Per Port MIB Counters....................................................................................................................................103

Table 15. Port 1 MIB Counters Indirect Memory Offset...................................................................................................................104

Table 16. “All Ports Dropped Packet” MIB Counters Format...........................................................................................................104

Table 17. “All Ports Dropped Packet” MIB Counters Indirect Memory Offsets ................................................................................104

Table 18. Static MAC Table Format (8 Entries)..............................................................................................................................106

Table 19. Dynamic MAC Address Table Format (1024 Entries).....................................................................................................107

Table 20. VLAN Table Format (16 Entries) .....................................................................................................................................108

Table 21. Maximum Ratings...........................................................................................................................................................109

Table 22. Operating Ratings...........................................................................................................................................................109

Table 23. Electrical Characteristics................................................................................................................................................110

Table 24. Asynchronous Cycle (ADSN = 0) Timing Parameters....................................................................................................111

Table 25. Asynchronous Cycle using ADSN Timing Parameters...................................................................................................112

Table 26. Asynchronous Cycle using DATACSN Timing Parameters............................................................................................113

Table 27. Address Latching Timing Parameters.............................................................................................................................114

Table 28. Synchronous Burst Write Timing Parameters.................................................................................................................115

Table 29. Synchronous Burst Read Timing Parameters ................................................................................................................116

Table 30. Synchronous Write (VLBUSN = 0) Timing Parameters..................................................................................................117

Table 31. Synchronous Read (VLBUSN = 0) Timing Parameters..................................................................................................118

Table 32. EEPROM Timing Parameters.........................................................................................................................................119

Table 33. Auto Negotiation Timing Parameters..............................................................................................................................120

Table 34. Reset Timing Parameters...............................................................................................................................................121

Table 35. Transformer Selection Criteria........................................................................................................................................122

Table 36. Qualified Single Port Magnetic .......................................................................................................................................122

Table 37. Typical Reference Crystal Characteristics......................................................................................................................122

Micrel, Inc. KSZ8862-16/32MQL

August 2010

11 M9999-081310-3.1

Pin Configuration for KSZ8862-16MQL (8/16-Bit)

Figure 2. 128-Pin PQFP

(Top View)

Micrel, Inc. KSZ8862-16/32MQL

August 2010

12 M9999-081310-3.1

Pin Description for KSZ8862-16MQL (8/16-Bit)

Pin

Number Pin Name Type Pin Function

1 TEST_EN I

Test Enable

For normal operation, 1K ohm pull-down this pin to ground.

2 SCAN_EN I

Scan Test Scan MUX Enable

For normal operation, 1K ohm pull-down this pin to ground.

3 P1LED2 Opu

4 P1LED1 Opu

5P1LED0 Opu

6 P2LED2 Opu

7 P2LED1 Opu

8 P2LED0 Opu

Port 1 and Port 2 LED indicators1 defined as follows:

Switch Global Control Register 5:

SGCR5 bit [15,9]

[0,0] Default [0,1]

P1LED32 /P2LED3 — —

P1LED2/P2LED2 Link/Act 100Link/Act

P1LED1/P2LED1 Full duplex/Col 10Link/Act

P1LED0/P2LED0 Speed Full duplex

Reg. SGCR5 bit [15,9]

[1,0] [1,1]

P1LED32 /P2LED3 Act —

P1LED2/P2LED2 Link —

P1LED1/P2LED1 Full duplex/Col —

P1LED0/P2LED0 Speed —

Notes:

1. Link = On; Activity = Blink; Link/Act = On/Blink; Full Dup/Col = On/Blink;

Full Duplex = On (Full duplex); Off (Half duplex)

Speed = On (100BASE-T); Off (10BASE-T)

2. P1LED3 is pin 27. P2LED3 is pin 22.

9 DGND Gnd

Digital ground

10 VDDIO P

3.3V digital VDDIO input power supply for IO with well decoupling capacitors.

11 RDYRTNN Ipd

Ready Return Not:

For VLBus-like mode: Asserted by the host to complete synchronous read cycles. If

the host doesn’t connect to this pin, assert this pin.

For burst mode (32-bit interface only): Host drives this pin low to signal waiting

states.

12 BCLK Ipd

Bus Interface Clock

Local bus clock for synchronous bus systems. Maximum frequency is 50MHz.

This pin should be tied Low or unconnected if it is in asynchronous mode.

13 NC Ipu No connect.

14 NC Opu No connect.

15 SRDYN Opu Synchronous Ready Not

Ready signal to interface with synchronous bus for both EISA-like and VLBus-like

extended accesses.

For VLBus-like mode, the falling edge of this signal indicates ready. This signal is

synchronous to the bus clock signal BCLK.

For burst mode (32-bit interface only), the KSZ8862M drives this pin low to signal

wait states.

Micrel, Inc. KSZ8862-16/32MQL

August 2010

13 M9999-081310-3.1

Pin

Number Pin Name Type Pin Function

16 INTRN Opd Interrupt

Active Low signal to host CPU to indicate an interrupt status bit is set, this pin need

an external 4.7K pull-up resistor.

17 LDEVN Opd Local Device Not

Active Low output signal, asserted when AEN is Low and A15-A4 decode to the

KSZ8862M address programmed into the high byte of the base address register.

LDEVN is a combinational decode of the Address and AEN signal.

18 RDN Ipd Read Strobe Not

Asynchronous read strobe, active Low.

19 EECS Opu EEPROM Chip Select

20 ARDY Opd Asynchronous Ready

ARDY may be used when interfacing asynchronous buses to extend bus access

cycles. It is asynchronous to the host CPU or bus clock. This pin needs an external

4.7K pull-up resistor.

21 CYCLEN Ipd

Cycle Not

For VLBus-like mode cycle signal; this pin follows the addressing cycle to signal the

command cycle.

For burst mode (32-bit interface only), this pin stays High for read cycles and Low for

write cycles.

22 P2LED3 Opd Port 2 LED indicator

See the description in pins 6, 7, and 8.

23 DGND Gnd Digital IO ground

24 VDDCO P

1.2V digital core voltage output (internal 1.2V LDO power supply output), this 1.2V

output pin provides power to VDDC, VDDA and VDDAP pins.

Note: Internally generated power voltage. Do not connect an external power supply

to this pin. This pin is used for connecting external filter (Ferrite bead and capacitors).

25 VLBUSN Ipd VLBus-like Mode

Pull-down or float: Bus interface is configured for synchronous mode.

Pull-up: Bus interface is configured for 8-bit or 16-bit asynchronous mode or EISA-

like burst mode.

26 EEEN Ipd EEPROM Enable

EEPROM is enabled and connected when this pin is pull-up.

EEPROM is disabled when this pin is pull-down or no connect.

27 P1LED3 Opd Port 1 LED indicator. See the description in pins 3, 4, and 5.

28 EEDO Opd EEPROM Data Out

This pin is connected to DI input of the serial EEPROM.

29 EESK Opd EEPROM Serial Clock

A 4μs serial output clock to load configuration data from the serial EEPROM.

30 EEDI Ipd EEPROM Data In

This pin is connected to DO output of the serial EEPROM when EEEN is pull-up.

This pin can be pull-down for 8-bit bus mode, pull-up for 16-bus mode or don’t care

for 32-bus mode when EEEN is pull-down (without EEPROM).

31 SWR Ipd Synchronous Write/Read

Write/Read signal for synchronous bus accesses. Write cycles when high and Read

cycles when low.

32 AEN Ipu Address Enable

Address qualifier for the address decoding, active Low.

Micrel, Inc. KSZ8862-16/32MQL

August 2010

14 M9999-081310-3.1

Pin

Number Pin Name Type Pin Function

33 WRN Ipd Write Strobe Not

Asynchronous write strobe, active Low.

34 DGND Gnd Digital IO ground

35 ADSN Ipd Address Strobe Not

For systems that require address latching, the rising edge of ADSN indicates the

latching moment of A15-A1 and AEN.

36 PWRDN Ipu Full-chip power-down. Low = Power down; High or floating = Normal operation.

37 AGND Gnd Analog ground

38 VDDA P 1.2V analog VDD input power supply from VDDCO (pin24) through external Ferrite

bead and capacitor.

39 AGND Gnd Analog ground

40 NC — No connect

41 100FX/10FL Ipu Fiber mode select for port 1. 1K ohm pull-up to 3.3V for 100Base-FX, 100 ohm pull-

down to GND for 100Base-SX or 10Base-FL.

42 AGND Gnd Analog ground

43 VDDA P 1.2V analog VDD input power supply from VDDCO (pin24) through external Ferrite

bead and capacitor.

44 FXSD1 I Fiber signal detect input for port 1 in 100Base-FX fiber mode. 1K ohm pull-up to 3.3V

for port 1 in 100Base-SX or 10Base-FL fiber modes.

45 RXP1 I/O Port 1 physical receive (MDI) signal (+ differential) from external fiber module

46 RXM1 I/O Port 1 physical receive (MDI) signal (– differential) from external fiber module

47 AGND Gnd Analog ground

48 TXP1 I/O Port 1 physical transmit (MDI) signal (+ differential) to external fiber module

49 TXM1 I/O Port 1 physical transmit (MDI) signal (– differential) to external fiber module

50 VDDATX P 3.3V analog VDD input power supply with well decoupling capacitors.

51 VDDARX P 3.3V analog VDD input power supply with well decoupling capacitors.

52 RXM2 I/O Port 2 physical receive (MDI) or transmit (MDIX) signal (- differential)

53 RXP2 I/O Port 2 physical receive (MDI) or transmit (MDIX) signal (+ differential)

54 AGND Gnd Analog ground

55 TXM2 I/O Port 2 physical transmit (MDI) or receive (MDIX) signal (- differential)

56 TXP2 I/O Port 2 physical transmit (MDI) or receive (MDIX) signal (+ differential)

57 VDDA P 1.2 analog VDD input power supply from VDDCO (pin24) through external Ferrite

bead and capacitor.

58 AGND Gnd Analog ground

59 NC Ipu No connect

60 NC Ipu No connect

61 ISET O Set physical transmits output current.

Pull-down this pin with a 3.01K 1% resistor to ground.

62 AGND Gnd Analog ground

63 VDDAP P 1.2V analog VDD for PLL input power supply from VDDCO (pin24) through external

Ferrite bead and capacitor.

64 AGND Gnd Analog ground

Micrel, Inc. KSZ8862-16/32MQL

August 2010

15 M9999-081310-3.1

Pin

Number Pin Name Type Pin Function

65 X1 I

66 X2 O

25MHz crystal or oscillator clock connection.

Pins (X1, X2) connect to a crystal. If an oscillator is used, X1 connects to a 3.3V

tolerant oscillator and X2 is a no connect.

Note: Clock requirement is 50ppm for either crystal or oscillator.

67 RSTN Ipu Hardware reset pin (active Low). This reset input is required minimum of 10ms low

after stable supply voltage 3.3V.

68 A15 I Address 15

69 A14 I Address 14

70 A13 I Address 13

71 A12 I Address 12

72 A11 I Address 11

73 A10 I Address 10

74 A9 I Address 9

75 A8 I Address 8

76 A7 I Address 7

77 A6 I Address 6

78 DGND Gnd Digital IO ground

79 VDDIO P 3.3V digital VDDIO input power supply for IO with well decoupling capacitors.

80 A5 I Address 5

81 A4 I Address 4

82 A3 I Address 3

83 A2 I Address 2

84 A1 I Address 1

85 NC I No Connect

86 NC I No Connect

87 BE1N I Byte Enable 1 Not, Active low for Data byte 1 enable (don’t care in 8-bit bus mode).

88 BE0N I Byte Enable 0 Not, Active low for Data byte 0 enable (there is an internal inverter

enabled and connected to the BE1N for 8-bit bus mode).

89 NC I No Connect

90 DGND Gnd Digital core ground

91 VDDC P

1.2V digital core VDD input power supply from VDDCO (pin24) through external

Ferrite bead and capacitor.

92 VDDIO P 3.3V digital VDDIO input power supply for IO with well decoupling capacitors.

93 NC I No Connect

94 NC I No Connect

95 NC I No Connect

96 NC I No Connect

97 NC I No Connect

98 NC I No Connect

99 NC I No Connect

100 NC I No Connect

101 NC I No Connect

102 NC I No Connect

103 NC I No Connect

Micrel, Inc. KSZ8862-16/32MQL

August 2010

16 M9999-081310-3.1

Pin

Number Pin Name Type Pin Function

104 NC I No Connect

105 NC I No Connect

106 NC I No Connect

107 DGND Gnd Digital IO ground

108 VDDIO P 3.3V digital VDDIO input power supply for IO with well decoupling capacitors.

109 NC I No Connect

110 D15 I/O Data 15

111 D14 I/O Data 14

112 D13 I/O Data 13

113 D12 I/O Data 12

114 D11 I/O Data 11

115 D10 I/O Data 10

116 D9 I/O Data 9

117 D8 I/O Data 8

118 D7 I/O Data 7

119 D6 I/O Data 6

120 D5 I/O Data 5

121 D4 I/O Data 4

122 D3 I/O Data 3

123 DGND Gnd Digital IO ground

124 DGND Gnd Digital core ground

125 VDDIO P 3.3V digital VDDIO input power supply for IO with well decoupling capacitors.

126 D2 I/O Data 2

127 D1 I/O Data 1

128 D0 I/O Data 0

Legend:

P = Power supply Gnd = Ground

I/O = Bi-directional I = Input O = Output

Ipd = Input with internal pull-down

Ipu = Input with internal pull-up

Opd = Output with internal pull-down

Opu = Output with internal pull-up

Micrel, Inc. KSZ8862-16/32MQL

August 2010

17 M9999-081310-3.1

Pin Configuration for KSZ8862-32MQL (32-Bit)

Figure 3. 128-Pin PQFP

(Top View)

Micrel, Inc. KSZ8862-16/32MQL

August 2010

18 M9999-081310-3.1

Pin Description for KSZ8862-32 MQL (32-Bit)

Pin

Number Pin Name Type Pin Function

1 TEST_EN I

Test Enable

For normal operation, 1K ohm pull-down this pin-to-ground.

2 SCAN_EN I

Scan Test Scan Mux Enable

For normal operation, 1K ohm pull-down this pin-to-ground.

3 P1LED2 Opu

4 P1LED1 Opu

5 P1LED0 Opu

6 P2LED2 Opu

7 P2LED1 Opu

8 P2LED0 Opu

Port 1 and Port 2 LED indicators1 defined as follows:

Switch Global Control Register 5:

SGCR5 bit [15,9]

[0,0] Default [0,1]

P1LED32 /P2LED3 — —

P1LED2/P2LED2 Link/Act 100Link/Act

P1LED1/P2LED1 Full duplex/Col 10Link/Act

P1LED0/P2LED0 Speed Full duplex

Reg. SGCR5 bit [15,9]

[1,0] [1,1]

P1LED32 /P2LED3 Act —

P1LED2/P2LED2 Link —

P1LED1/P2LED1 Full duplex/Col —

P1LED0/P2LED0 Speed —

Notes:

1. Link = On; Activity = Blink; Link/Act = On/Blink; Full Dup/Col = On/Blink;

Full Duplex = On (Full duplex); Off (Half duplex)

Speed = On (100BASE-T); Off (10BASE-T)

2. P1LED3 is pin 27. P2LED3 is pin 22.

9 DGND Gnd

Digital ground

10 VDDIO P

3.3V digital VDDIO input power supply for IO with well decoupling capacitors.

11 RDYRTNN Ipd

Ready Return Not

For VLBus-like mode: Asserted by the host to complete synchronous read cycles. If the

host doesn’t connect to this pin, assert this pin.

For burst mode (32-bit interface only): Host drives this pin low to signal waiting states.

12 BCLK Ipd Bus Interface Clock

Local bus clock for synchronous bus systems. Maximum frequency is 50MHz.

This pin should be tied Low or unconnected if it is in asynchronous mode.

13 DATACSN Ipu DATA Chip Select Not (For KSZ8862-32 Mode only)

Chip select signal for QMU data register (QDRH, QDRL), active Low.

When DATACSN is Low, the data path can be accessed regardless of the value of AEN,

A15-A1, and the content of the BANK select register.

14 NC Opu

No connect.

15 SRDYN Opu

Synchronous Ready Not

Ready signal to interface with synchronous bus for both EISA-like and VLBus-like extend

accesses.

For VLBus-like mode, the falling edge of this signal indicates ready. This signal is

synchronous to the bus clock signal BCLK.

For burst mode (32-bit interface only), the KSZ8862M drives this pin low to signal wait states.

Micrel, Inc. KSZ8862-16/32MQL

August 2010

19 M9999-081310-3.1

Pin

Number Pin Name Type Pin Function

16 INTRN Opd

Interrupt

Active Low signal to host CPU to indicate an interrupt status bit is set, this pin need an

external 4.7K pull-up resistor.

17 LDEVN Opd

Local Device Not

Active Low output signal, asserted when AEN is Low and A15-A4 decode to the

KSZ8862M address programmed into the high byte of the base address register. LDEVN

is a combinational decode of the Address and AEN signal.

18 RDN Ipd

Read Strobe Not

Asynchronous read strobe, active Low.

19 EECS Opu

EEPROM Chip Select

20 ARDY Opd

Asynchronous Ready

ARDY may be used when interfacing asynchronous buses to extend bus access cycles.

It is asynchronous to the host CPU or bus clock. This pin needs an external 4.7K pull-up

resistor.

21 CYCLEN Ipd

Cycle Not

For VLBus-like mode cycle signal; this pin follows the addressing cycle to signal the

command cycle.

For burst mode (32-bit interface only), this pin stays High for read cycles and Low for

write cycles.

22 P2LED3 Opd

Port 2 LED indicator. See the description in pins 6, 7, and 8.

23 DGND Gnd

Digital IO ground

24 VDDCO P

1.2V digital core voltage output (internal 1.2V LDO power supply output), this 1.2V output

pin provides power to VDDC, VDDA and VDDAP pins.

Note: Internally generated power voltage. Do not connect an external power supply to this

pin. This pin is used for connecting external filter (Ferrite Bead and capacitors).

25 VLBUSN Ipd

VLBus-like Mode

Pull-down or float: Bus interface is configured for synchronous mode.

Pull-up: Bus interface is configured for 32-bit asynchronous mode or EISA-like burst

mode.

26 EEEN Ipd

EEPROM Enable

EEPROM is enabled and connected when this pin is pull-up.

EEPROM is disabled when this pin is pull-down or no connect.

27 P1LED3 Opd Port 1 LED indicator

See the description in pins 3, 4, and 5.

28 EEDO Opd EEPROM Data Out

This pin is connected to DI input of the serial EEPROM.

29 EESK Opd EEPROM Serial Clock

A 4μs serial output clock to load configuration data from the serial EEPROM.

30 EEDI Ipd EEPROM Data In

This pin is connected to DO output of the serial EEPROM when EEEN is pull-up.

This pin can be pulled-down for 8-bit bus mode, pulled-up for 16-bus mode or either way

for 32-bus mode when EEEN is pulled-down (without EEPROM).

31 SWR Ipd Synchronous Write/Read

Write/Read signal for synchronous bus accesses. Write cycles when high and Read

cycles when low.

32 AEN Ipu Address Enable

Address qualifier for the address decoding, active Low.

33 WRN Ipd Write Strobe Not Asynchronous write strobe, active Low.

Micrel, Inc. KSZ8862-16/32MQL

August 2010

20 M9999-081310-3.1

Pin

Number Pin Name Type Pin Function

34 DGND Gnd Digital IO ground

35 ADSN Ipd Address Strobe Not

For systems that require address latching, the rising edge of ADSN indicates the latching

moment of A15-A1 and AEN.

36 PWRDN Ipu Full-chip power-down. Low = Power down; High or floating = Normal operation.

37 AGND Gnd Analog ground

38 VDDA P 1.2V analog VDD input power supply from VDDCO (pin24) through external Ferrite bead

and capacitor.

39 AGND Gnd Analog ground

40 NC — No connect

41 100FX/10F

L Ipu Fiber mode select for port 1. 1K ohm pull-up to 3.3V for 100Base-FX, 100 ohm pull-down

to GND for 100Base-SX or 10Base-FL.

42 AGND Gnd Analog ground

43 VDDA P 1.2V analog VDD input power supply from VDDCO (pin24) through external Ferrite bead

and capacitor.

44 FXSD1 I Fiber signal detect input for port 1 in 100Base-FX fiber mode. 1K ohm pull-up to 3.3V for

port 1 in 100Base-SX or 10Base-FL fiber modes.

45 RXP1 I/O Port 1 physical receive (MDI) signal (+ differential) from external fiber module

46 RXM1 I/O Port 1 physical receive (MDI) signal (– differential) from external fiber module

47 AGND Gnd Analog ground

48 TXP1 I/O Port 1 physical transmit (MDI) signal (+ differential) to external fiber module

49 TXM1 I/O Port 1 physical transmit (MDI) signal (– differential) to external fiber module

50 VDDATX P 3.3V analog VDD input power supply with well decoupling capacitors.

51 VDDARX P 3.3V analog VDD

52 RXM2 I/O Port 2 physical receive (MDI) or transmit (MDIX) signal (- differential)

53 RXP2 I/O Port 2 physical receive (MDI) or transmit (MDIX) signal (+ differential)

54 AGND Gnd Analog ground

55 TXM2 I/O Port 2 physical transmit (MDI) or receive (MDIX) signal (- differential)

56 TXP2 I/O Port 2 physical transmit (MDI) or receive (MDIX) signal (+ differential)

57 VDDA P 1.2 analog VDD input power supply from VDDCO (pin24) through external Ferrite bead

and capacitor.

58 AGND Gnd Analog ground

59 NC Ipu No connect

60 NC Ipu No connect

61 ISET O Set physical transmits output current.

Pull-down this pin with a 3.01K 1% resistor to ground.

62 AGND Gnd Analog ground

63 VDDAP P 1.2V analog VDD for PLL input power supply from VDDCO (pin24) through external

Ferrite bead and capacitor.

64 AGND Gnd Analog ground

65 X1 I

66 X2 O

25MHz crystal or oscillator clock connection.

Pins (X1, X2) connect to a crystal. If an oscillator is used, X1 connects to a 3.3V tolerant

oscillator and X2 is a no connect.

Note: Clock is 50ppm for either crystal or oscillator.

67 RSTN Ipu Hardware reset pin (active Low). This reset input is required minimum of 10ms low after

stable supply voltage 3.3V.

Other manuals for KSZ8862-16MQL

1

This manual suits for next models

3

Table of contents

Other Micrel Switch manuals