RTE-V821-PC USER’S MANUAL

2

CONTENTS

1. INTRODUCTION..........................................................................................................................4

1.1. NUMERIC NOTATION...........................................................................................................4

2. FEATURES AND FUNCTIONS.....................................................................................................5

3. BOARD CONFIGURATION..........................................................................................................6

3.1. RESET SWITCH (SWRESET)...............................................................................................6

3.2. POWER SUPPLY CONNECTOR (JPOWER).........................................................................6

3.3. SWITCH1 (SW1) ..................................................................................................................6

3.4. SWITCH2 (SW2) ..................................................................................................................7

3.5. LED ......................................................................................................................................7

3.6. TEST PINS (TP)....................................................................................................................7

3.7. SUBPORT (JSUBPORT).......................................................................................................7

3.8. SERIAL CONNECTOR (JSIO)...............................................................................................8

3.9. CPU TEST PINS (JCPU).......................................................................................................9

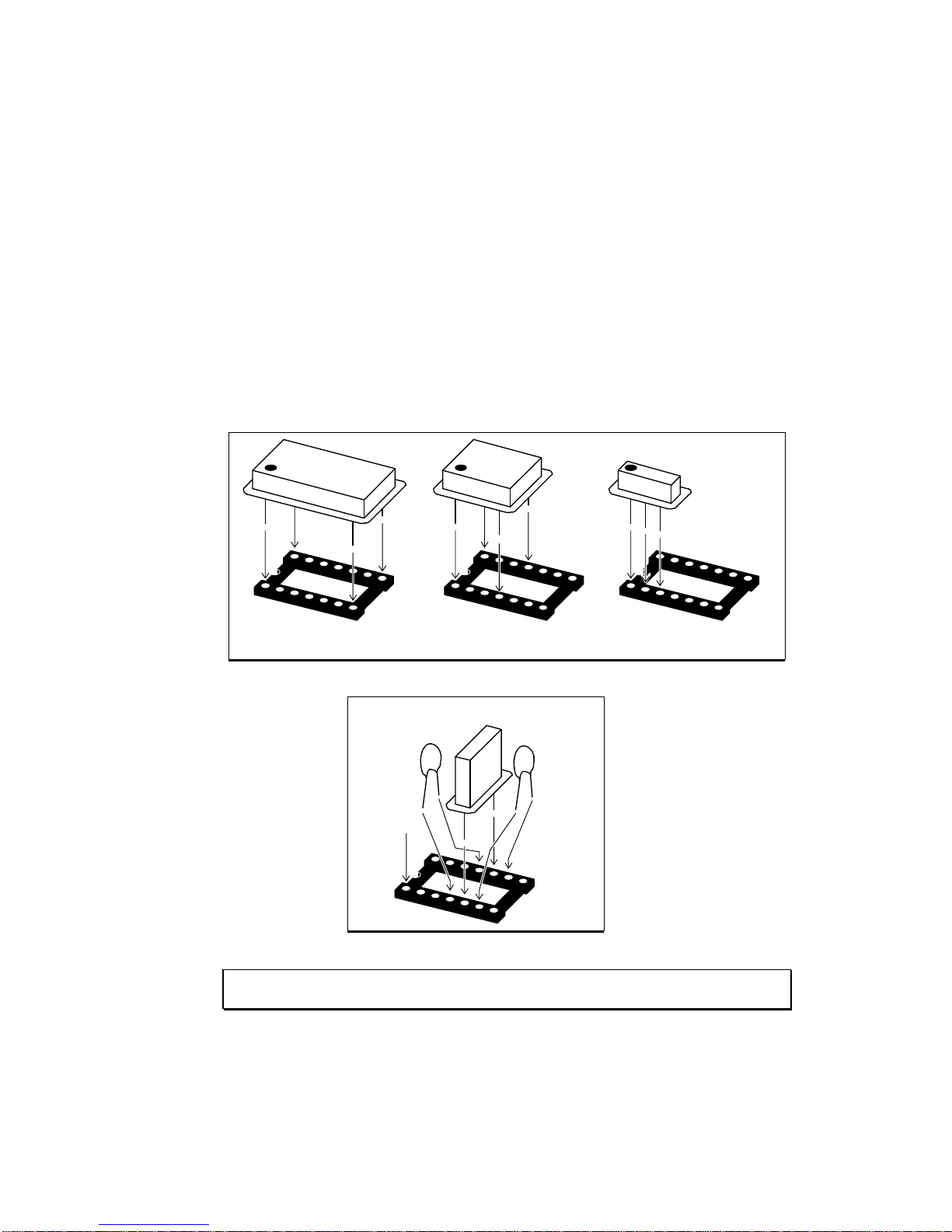

3.10. CLOCK SOCKET (OSC1)......................................................................................................9

3.11. DRAM-SIMM SOCKETS......................................................................................................10

3.12. ROM SOCKETS..................................................................................................................10

4. INSTALLATION AND USE.......................................................................................................... 11

4.1. BOARD SETTING............................................................................................................... 11

4.2. INSTALLATION ON THE ISA BUS.......................................................................................12

4.3. STANDALONE USE OF THE BOARD .................................................................................12

5. HARDWARE REFERENCES......................................................................................................13

5.1. MEMORY MAP....................................................................................................................13

5.2. I/O MAP..............................................................................................................................14

5.2.1. Port Unit (PORT)..........................................................................................................14

5.2.2. Wait Control Unit (WCU)..............................................................................................14

5.2.3. DRAM Control Unit (DRAMC).......................................................................................15

5.2.4. ROM Controller (ROMC)...............................................................................................15

5.2.5. DMA Controller (DMAC)................................................................................................15

5.2.6. Realtime Pulse Unit (RPU) ...........................................................................................15

5.2.7. Serial Control Unit (SCU)..............................................................................................15

5.2.8. Interrupt Control Unit (ICU)...........................................................................................16

5.2.9. Bus Arbitration Unit (BAU)............................................................................................16

5.2.10. Clock Generator (CG)...............................................................................................16

5.2.11. Watchdog Timer Unit (WDT) ........................................................................................16

6. SYSTEM-I/O..............................................................................................................................17

6.1. UART/TIMER (SCC2691)....................................................................................................17

6.2. PIO (µPD71055)..................................................................................................................17

7. JEXT BUS SPECIFICATION.......................................................................................................19

8. OTHER CPU RESOURCES.......................................................................................................21