3.15 JTAG Debugging ..........................................................................................................................18

3.16 Powering the board .................................................................................................................... 18

3.17 Parallella On-Board Power Management ...................................................................................19

3.18 Parallella Supply Outputs............................................................................................................20

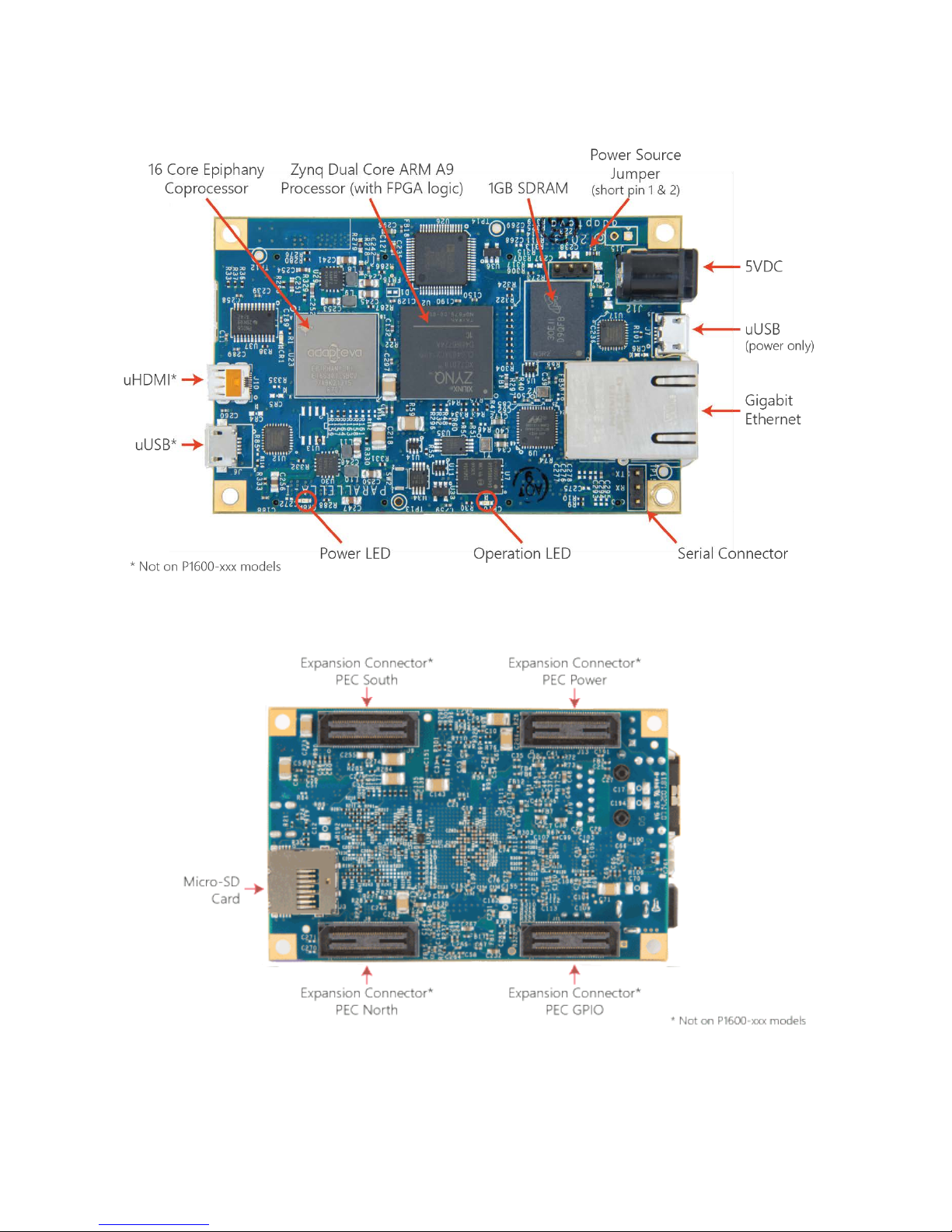

3.19 Parallella Expansion Connectors................................................................................................. 20

3.20 Mounting Holes........................................................................................................................... 22

4 Parallella System Architecture.................................................................................................. 23

4.1 Zynq Memory Map......................................................................................................................23

4.2 Epiphany Memory Map ..............................................................................................................24

4.3 Epiphany Specific FPGA Resources .............................................................................................25

5 Board Configuration ................................................................................................................. 27

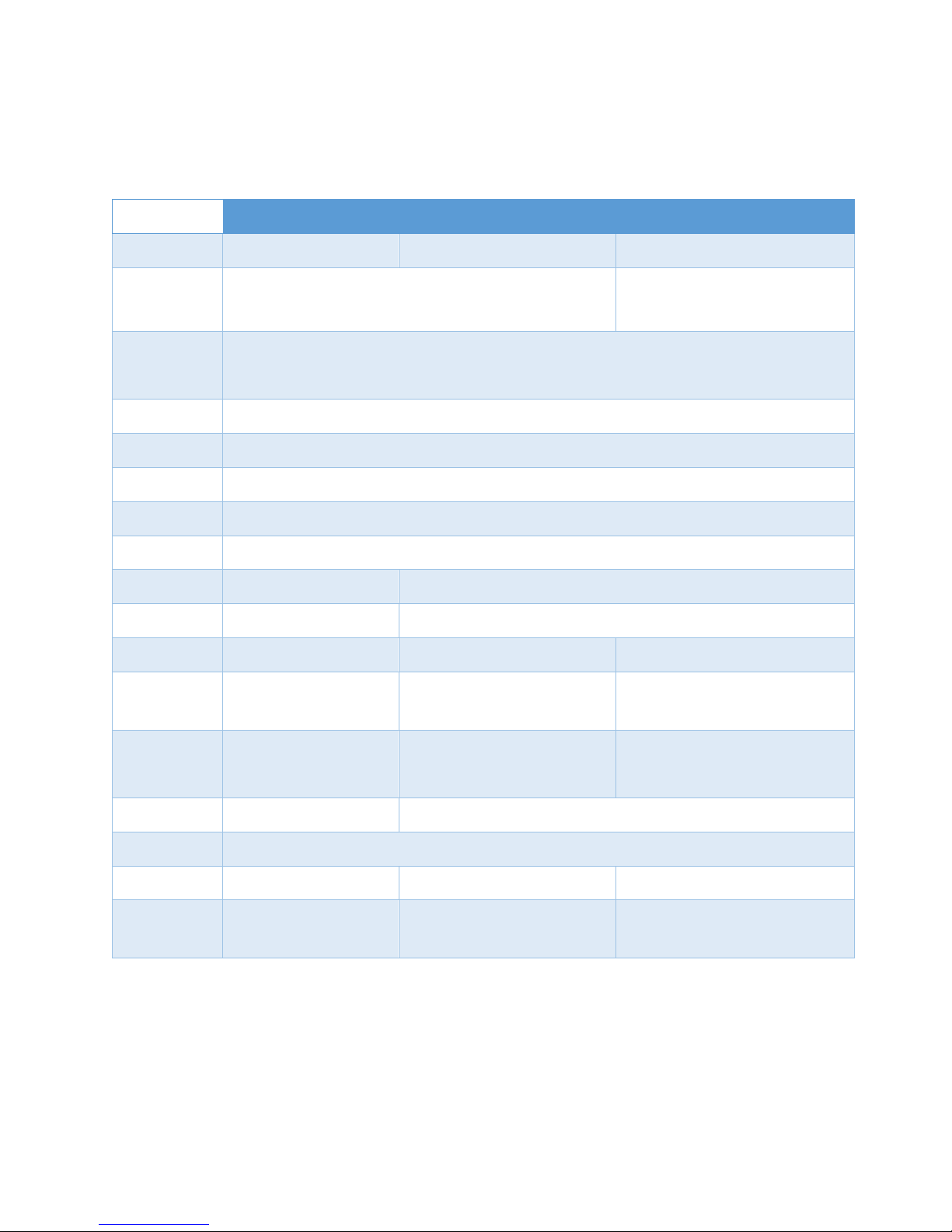

5.1 FPGA Pin Assignment .................................................................................................................. 27

6 Booting the Parallella................................................................................................................ 32

7 Parallella Expansion Connector Details .................................................................................... 33

7.1 PEC_POWER................................................................................................................................33

7.2 PEC_FPGA.................................................................................................................................... 36

7.3 PEC_NORTH/PEC_SOUTH ...........................................................................................................38

8 Electrical and Performance Specifications ............................................................................... 43

8.1 Dimensions and Weight.............................................................................................................. 43

8.2 Power Consumption ................................................................................................................... 43

8.3 Performance Metrics ..................................................................................................................43

8.4 IC Metrics Summary.................................................................................................................... 44

9 About the Parallella Board........................................................................................................ 45

9.1 Design Information ..................................................................................................................... 45

9.2 Build Options............................................................................................................................... 45

9.3 Contributors................................................................................................................................ 46

9.4 Attributions ................................................................................................................................. 47

9.5 Licensing...................................................................................................................................... 47

9.6 Disclaimers ..................................................................................................................................48

9.7 Warranty ..................................................................................................................................... 50

REV 14.09.09 5