User's Manual 3

TABLE OF CONTENTS

PREFACE................................................................................... 5

CHAPTER 1 INTRODUCTION........................................................ 6

Specification ............................................................................................ 6

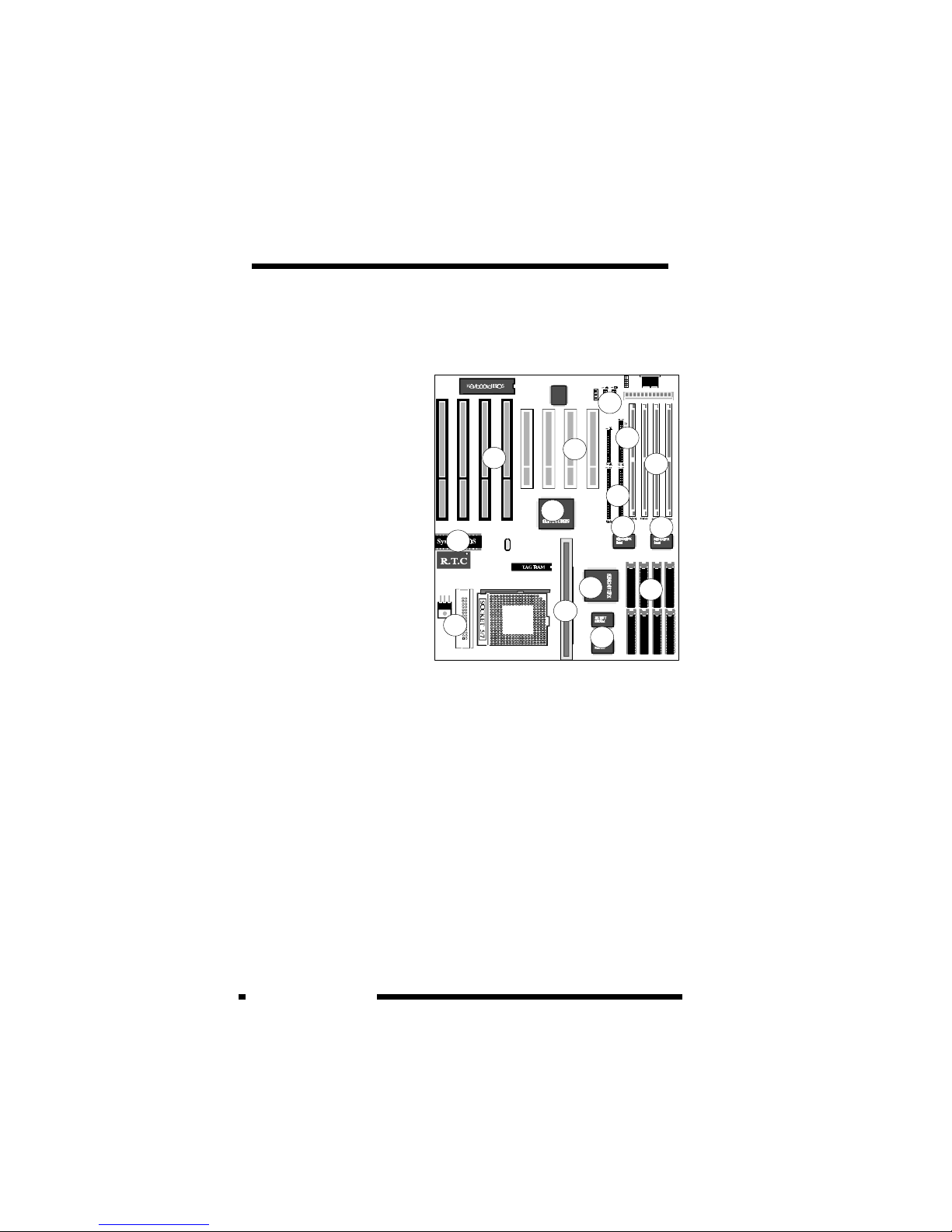

541 Mainboard Description ................................................................... 8

541 Mainboard Layout .........................................................................10

CHAPTER 2 JUMPER SETTING ....................................................11

System Clock Selection .........................................................................11

Pentium CPU Clock Multiplier..............................................................12

Onboard Regulator & VRM Selection...................................................13

Onboard Voltage Regulator Output Selection .....................................14

AT Bus Clock Selection .........................................................................15

Cache Type Selection............................................................................16

Standard Type Cache Size Selection ....................................................18

Cache Voltage Selection........................................................................19

I/O Port Setting & Parallel Port DREQ Selection ...................................20

Flash EPROM Jumper ............................................................................21

Clear CMOS...........................................................................................22

Clear Password ......................................................................................22

Connectors ............................................................................................23

CHAPTER 3 MEMORY CONFIGURATION......................................26

Memory Configuration Reference Table...............................................27

Chapter 4 Power management..............................................................28

Power Management Description ..........................................................28

EPMI Connector ....................................................................................29

CHAPTER 5 AMI BIOS SETUP ...................................................30

BIOS Setup Feature................................................................................31

Navigating with the keyboard in WinBIOS Setup.................................32

Standard Setup.......................................................................................34

Advanced Setup ....................................................................................36

Chipset Setup.........................................................................................40

Power Management Setup ....................................................................43

Peripheral Setup ....................................................................................45

WinBIOS Password Support .................................................................47