BU RF Solutions

- 2-

Table of Contents Page

Introduction 4

1. General Block Diagram and Descriptions 4

2.PinningConfigurations 6

3. Quick Startup Guide for User 7

4. An overview of the Evaluation Board 8

4.1 Board Settings 10

4.1.2 Board Power Supplies 10

4.1.3 Connectors 10

4.1.4 Jumper Configurations 11

4.1.5 Hard Reset 11

5. Channel Decoder Software Guide And Installation 12

5.1 Software Installation 12

5.2 Channel Decoder TDA10021 12

5.2.1 TDA10021 – Control Software Windows 12

5.2.2 TDA10021 - A Quick Guide to software Usage 16

5.3 Channel Decoder TDA10046 16

5.3.1 TDA10046 -- Control Software Windows 16

5.3.2 TDA10046 – A Quick Guide to software Usage 20

5.4 Trouble Shooting 21

List of Figures

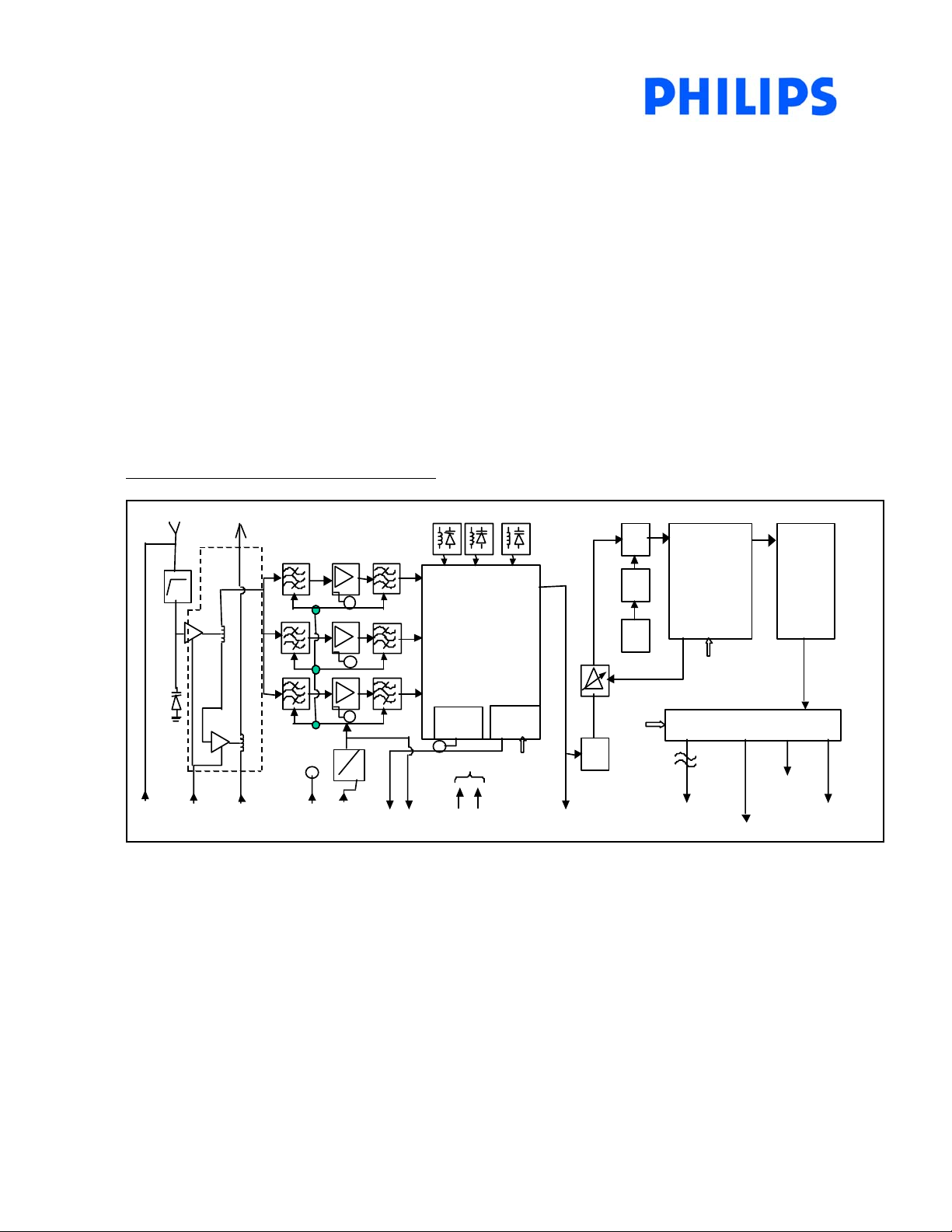

Figure 1.1 CU1216 General Block Diagram 4

Figure 1.2 TU1216 General Block Diagram 5

Figure 4.1 Evaluation Board Layout 8

Figure 4.2 Physical Evaluation Board 9

Figure 5.1 TDA10021 Main User Interface Window 13

Figure 5.2 TDA10021 Board Configuration Window 14

Figure 5.3 TDA10021 Registers under lock condition 15

Figure 5.4 TDA10046 Main User Interface Window – Download DSP code 17

Figure 5.5 TDA10046 Main User Interface Window 17

Figure 5.6 TDA10046 Board Configuration Window 19

Figure 5.7 TDA10046 Registers 19

List of Tables

Table 2.1 Pinning Configurations 6

Table 5.1 Descriptions for the TDA10021 main user interface window 13

Table 5.2 Descriptions for the TDA10021 board configuration window 15

Table 5.3 Descriptions for the TDA10046 main user interface window 18

Table 5.4 Descriptions for the TDA10046 board configuration window 19

Appendix A : Evaluation Board Schematic Diagram 22