Interconnectivity Page 3of 14

PDIUSBD12 Evaluation Board (PC Kit) User’s Manual REV. 2.1

_______________________________________________________________________________________________

Philips Semiconductors - Asia Product Innovation Centre

Visit http://www.flexiusb.com

TABLE OF CONTENTS

DISCLAIMER .............................................................................................................2

TABLE OF CONTENTS.............................................................................................3

INSTALLATION OF PDIUSBD12 EVALUATION BOARD........................................4

Introduction....................................................................................................................................................4

System Requirements.....................................................................................................................................4

Installation......................................................................................................................................................5

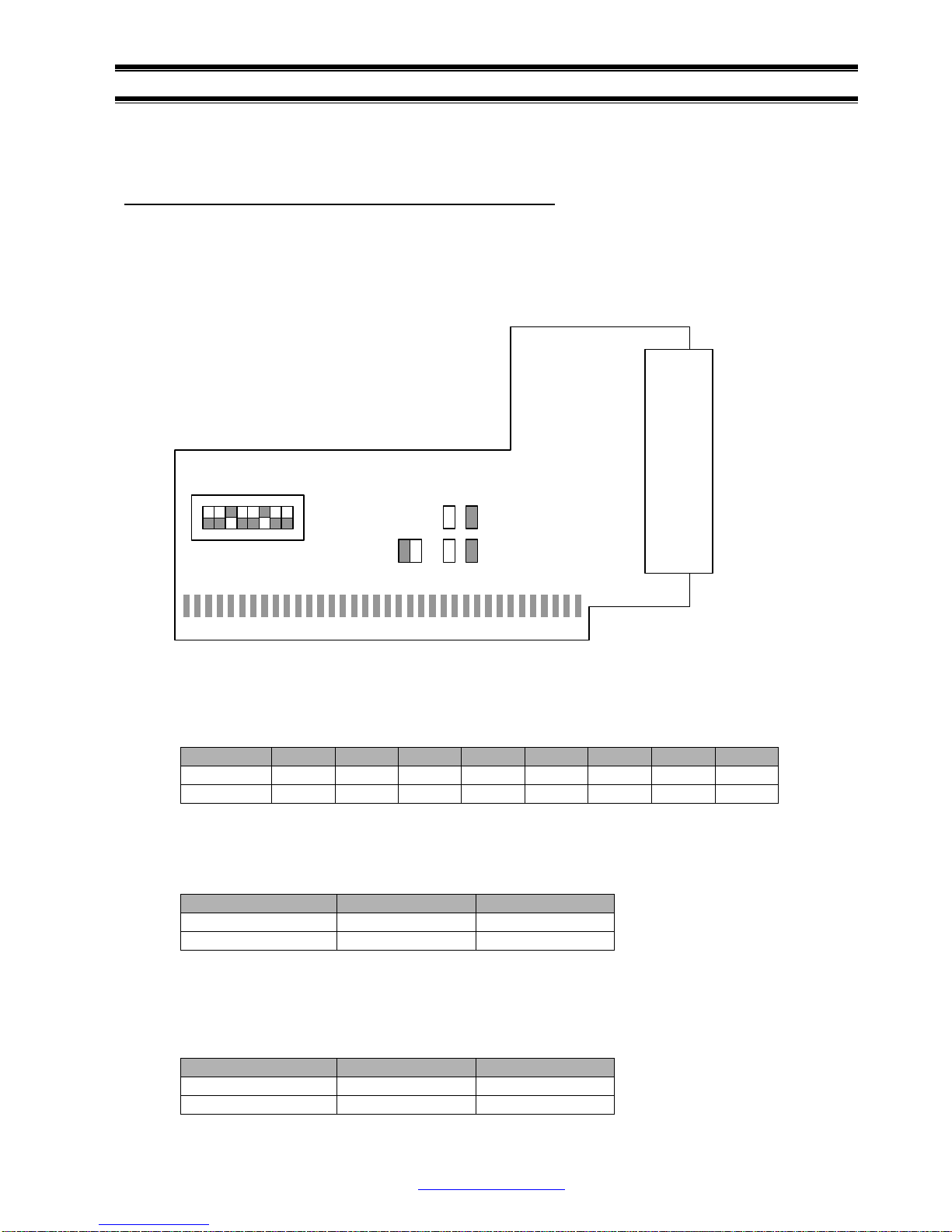

Jumper’s setting on PDIUSBD12 ISA bridging board...................................................................................5

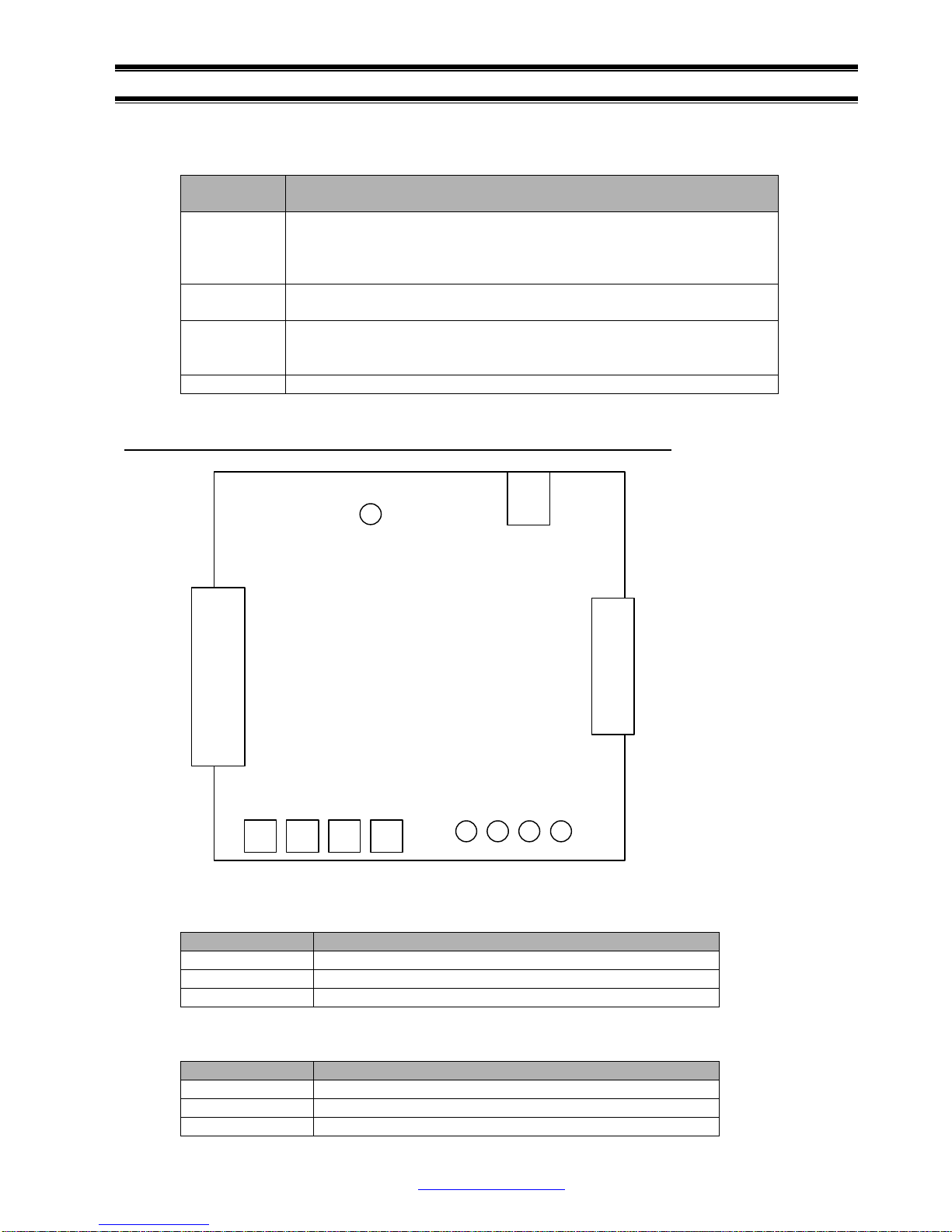

Location of key components on the PDIUSBD12 evaluation board. ..............................................................6

Installation of firmware, INF and driver........................................................................................................7

Using the Host Applet ....................................................................................................................................7

HARDWARE DESCRIPTION.....................................................................................9

Block Diagram................................................................................................................................................9

I/O Mapping...................................................................................................................................................9

Connectors....................................................................................................................................................10

PAL Equations.............................................................................................................................................11

Address and command decoder...................................................................................................................11

Schematics....................................................................................................................................................12

Schematics for PDIUSBD12 evaluation board ............................................................................................12

Schematic for PDIUSBD12 ISA bridging board..........................................................................................13

Bill of Materials............................................................................................................................................14

Bill of materials of the PDIUSBD12 evaluation board.................................................................................14

Bill of materials of the PDIUSBD12 ISA bridging board.............................................................................14