digit will not involve any number except 1, fre-

quency data is applied only to input A at time T4,

the B, C and D inputs serving as for data desig-

nating the FM/AM operational mode. Input L is

the load pulse input employed to prevent mis-

rading of input data. Data latching starts with

down stroke of the load pulse.

The SX-D5000 synthesizer system is operated

on the basisof time division pulses (T1-T4) pre-

pared by the synthesizercontrol IC (TC9124AP).

Data transfer is basedon dynamic time division.

OperatingDuringFM Reception

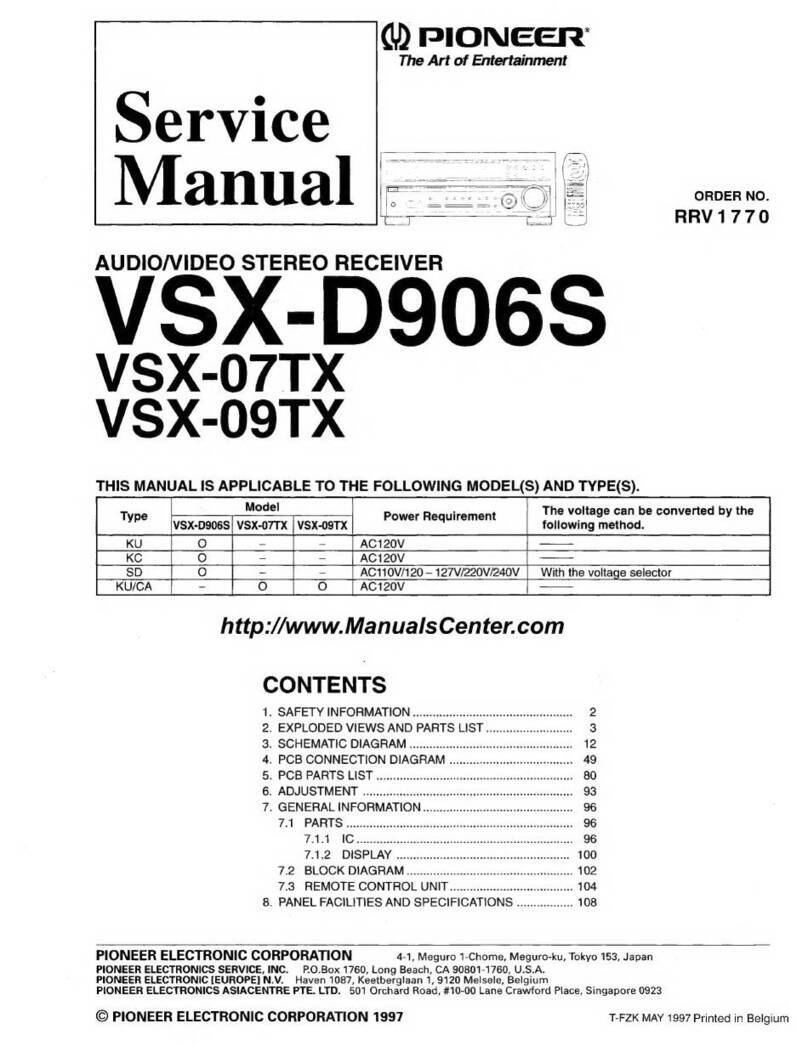

Fig. 4-5 outlines the block diagtam of the SX-

D5000 synthesizer stage during FM reception.

With the basic operational step at 100kHz in

Fig. 4-5, and the prescalar

dividing the frequency

by 8, the phase comparison frequency will be

t2.5kHz. The referencefrequency signalis obtain-

ed by dividing the 6.4MHz crystal oscillator output

by 512. And since the reception band is 87.5

MHz to 108MHz and the IF 10.7MH2,the local

oscillator frequency will range from 98.2MHz to

118.7MH2. After dividing by 8 in the prescalar,

this range will be 72.275MH2 to 14.8375MH2.

Hence, the 12.5kHz may be obtained by setting

the programmable countet frequency division

ratio N to 982-1187 for comparison with the

reference signal in the phase comparator. The

phase comparator output is passedvia a low-

pass filter to the tuning circuit vari-cap, resulting

in the local oscillator frequency being locked to

8N times the reference frequency (12.5kH2), or

in other words,N times 100kHz.

Since the reception frequency data (n) applied

to the synthesizerIC (TC9123P-GR) is shown in

the FL indicator tube (frequency display) as

875-1080, the required frequency division ratio

may be obtained from the reception frequency

data by programming for frequency division

ratioN:n+107 duringFM reception.

50kHz StepOperation (Model SX-D5000/S/G)

The circuit shown in Fig. 4-5 will only change

the reception frequency in 100kHz steps unless

otherwise modified. By altering the frequency

division ratio N, a 50kHz shift circuit may be

activated with every second 100kHz frequency

shift, resulting in the reception frequency being

changedin 50kHz steps.

The Fig. 4-5 circuit forms a PLL (phase

locked

loop) where the local oscillator signalis sampled,

divided, and then locked to a frequency 8N times

the referece frequency (12.5kH2). Consequently,

any attempt to vary the local oscillator frequency

will result in the voltage applied to the vari-cap be-

ing changed in a way that wilI tend to cancel this

variation. If then by some means a count can be

obtained 50kHz lower than the actual frequency

when the local oscillator is being sampled,it will

be possible to alter the voltage applied to the

vari-cap so that the oscillation frequency is increas-

ed by 50kHz.

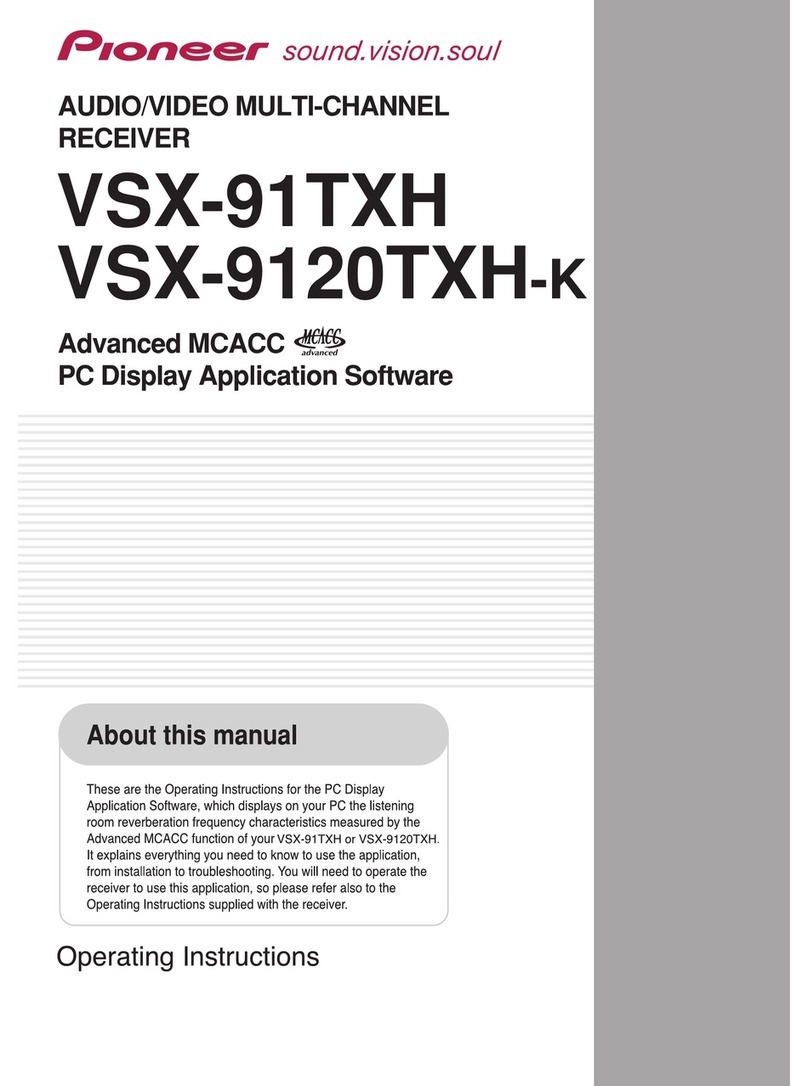

The prescalarIC (TD6L02P) shown in Fig. 4-6

contains 3 separate 1/2 frequency dividers for a

total frequency division of U8. If a single shift

pulse is applied to pin 9, a pulsecount at the Ll4

division stage will be eliminated. And if the shift

pulse frequency is 72.5kH2, a total of 12,500

pulses will not be counted during the 1 second

period. In terms of the IC input terminal (pin 2),

this is equivalent to not counting 50,000 pulses

within the sameperiod, which in turn is equivalent

to applying an input frequency which is 50kHz

lower than the actual input frequency. The PLL

consequentlyattempts to cancelthis change,

there-

by increasing the voltage applied to the vari-cap so

that the oscillation frequency is increased by

50kHz. The local oscillator frequency is thus

locked at afrequency increasedby 50kHz, thereby

shifting the reception frequency by +50kHz.

98.2-118.7lVHz -12.275-

tc (Tc9123-GR)

Fig.4-6 50kHzShiftCircuit

10

Fig.4-5 OutlineDuring

FMReception