www.scalys.com

User Manual

May 17, 2018

Contents

List of Tables 4

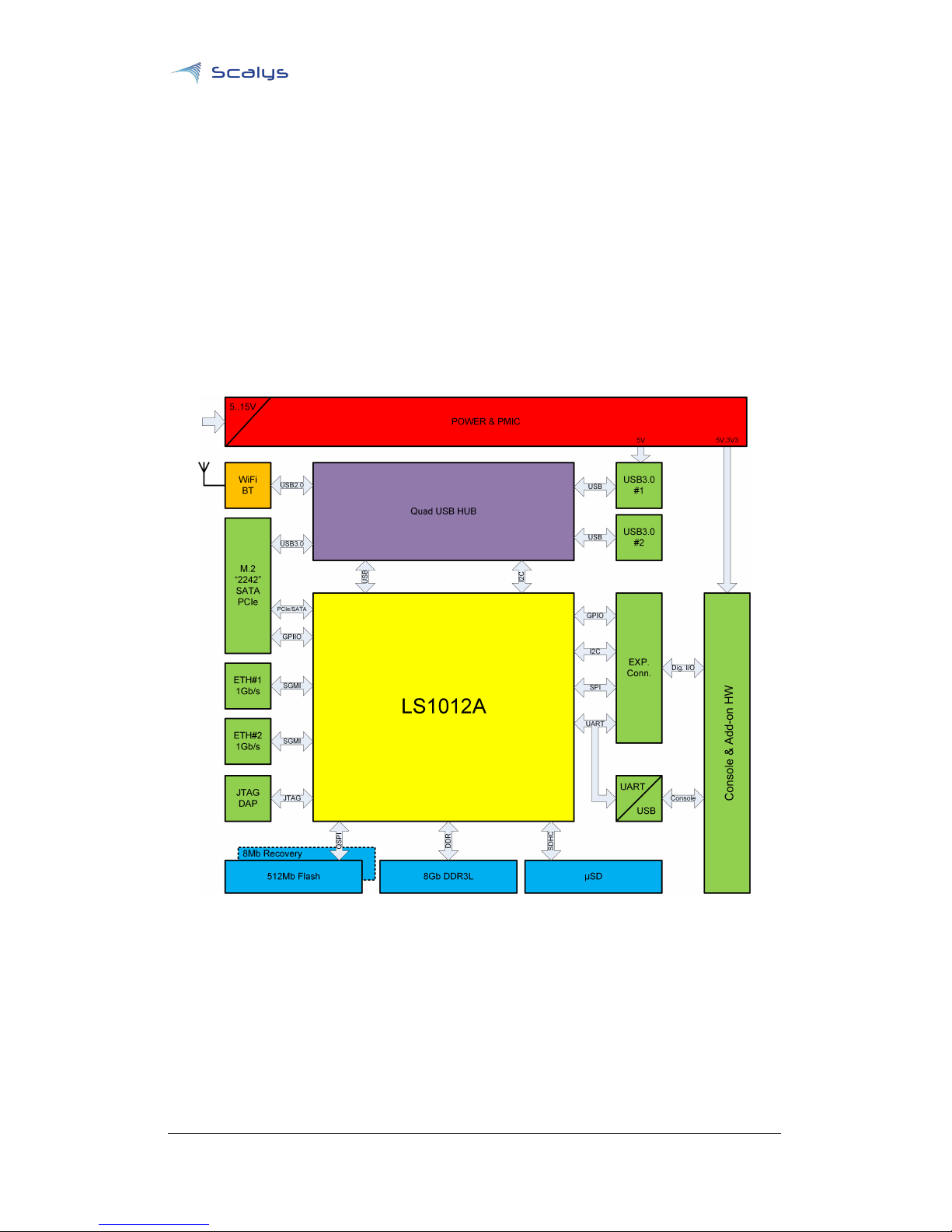

1 GrapeBoard™ features 5

1.1 Block diagram ........................................ 5

1.2 Feature List ......................................... 6

1.2.1 Main board components .............................. 6

1.2.2 Interfaces ...................................... 6

2 Board overview 7

2.1 Mechanical drawing .................................... 7

2.2 Mounting holes ....................................... 7

2.3 Connectors .......................................... 9

2.3.1 Buttons and LEDs ................................. 11

3 Electrical Specification 12

3.1 Supply voltage ........................................ 12

3.2 Power specification ..................................... 12

3.3 Temperature specification ................................. 12

4 Interfaces 13

4.1 SERDES options ....................................... 13

4.2 I2C.............................................. 13

4.2.1 Raspberry PI™ connector ............................. 14

4.2.2 JTAG ......................................... 14

4.2.3 WiFi/ Bluetooth ................................... 15

4.2.4 Tamper ........................................ 16

4.2.5 Boot device ..................................... 16

4.2.6 Boundary scan ................................... 16

4.2.7 Ethernet ....................................... 16

4.2.8 USB2.0-B micro ................................... 17

4.2.9 PWR_IN connector ................................. 17

4.2.10 PWR for industrial use ............................... 17

4.2.11 SDHC ........................................ 17

4.2.12 USB 3.0 ........................................ 17

4.2.13 M.2 Socket ...................................... 18

4.2.14 Board reset ...................................... 18

4.2.15 Push button for recovery boot operation .................... 19

5 Board Support Package 20

A References 21

B List of Acronyms 22

Copyright © 2018, Scalys BV Public 3