SD System VFW-III User manual

)

VFW-III

J

ERSAFLOPPY

WINCHESTER

DISK

CONTROLLER

OPERATIONS

MANUAL

SD

#7140174

REVISION A

SEPTEMBER 21, 1983

.•

P.O. B

ox

28810, Dal

las

, Te

xas

75228

)

)

)

VFW-III

VERSAFLOPPY

WINCHESTER

DISK

CONTROLLER

SD

#7140174

REVISION

A

SEPTEMBER

21,

1983

OPERATIONS

MANUAL

•

TABLE

OF

CONTENTS

Subsection

Page

Number

Title

No.

SECTION

I

INTRODUCTION

1.0

GENERAL

1-1

1.1

FEATURES

1-1

1.2

SCOPE

1-2

SECTION

II

THEORY

OF

OPERATION

2.0

GENERAL

2-1

2.1

S-100

COMPUTER

BUS

2-1

2.2

WINCHESTER

DISK

DRIVES

2-3

2.3

FLOPPY

DISK

DRIVES

2-5

2.4

VFW-III

DISK

CONTROLLER

2-6

2.4.1

Zone

1:

Winchester

Control

2-6

2.4.2

Zone

2:

Buffer

Control

and

Support

Logic

2-7

2.4

. 3 Zone

3:

Status

and

Control

Port

2-7

2.4.4

Zone

4:

Basic

S-100

Interface

2-7

2.4.5

Zone

5:

TMA

Interface

2-7

2.4.6

Zone

6:

Control

Processor

2-7

)

2.4.7

Zone

7:

Floppy

Disk

Interface

2-8

3.0

3.1

3.1.1

3.1.2

3.

1.2

.1

3.

1

.2.2

3.1.2.3

3.

1.

2.3.1

3.1.2.3.2

3.1.2.3.3

3.1

.2.4

3.1.2.5

3.1.2.6

3

.1.3

3

.1.4

3.1.5

3 .

1.6

3.1.7

3.

1

.8

3.

1

.9

3.1.9.1

3.1.9.2

3.1.9.3

3.1.9.4

3.1.9.5

3.1.9.6

3.1.9.7

3.1.10

3.1

.11

3.1

.1

2

3.1.13

3

.1.14

3.1.14.1

3.1.14.2

3.1.14.3

3.1.14.4

3.1.14.5

3.1.14.6

3

.1.1

4.7

3.2

3.2.1

3.2

.

1.l

3

.2.1.2

3

.2.1.

3

3 . 2

.2

3.2.2.1

3.2.2.2

3.2.3

3.2.3.1

3

.2.

3 . 2

3.2

.

3.3

GENERAL

MEMORY

MAP

SECTION

III

SOF'IWARE

DRIVERS

SECTOR

BUFFER

(READ/WRITE

AND

INCREMENT)

ERROR

REGISTER

(READ

ONLY)

NO

DATA

ADDRESS

MARK

TRACK

0

NOT

FOUND

COMMAND

ABORTED

STATUS

REGISTER

BIT

6:

READY

STATUS

REGISTER

BIT

5:

WRITE

FAULT

STATUS

REGISTER

BIT

4:

SEEK

COMPLET

E

IDENTIFICATION FIELD

NOT

FOUND

UNCORRECTABLE

ERROR

BAD

BLOCK

DETECT

WRITE

PRECOMPENSATION

CYLINDER

(WRITE

ONLY)

SECTOR

COUNT

(READ/WRITE)

SECTOR

NUMBER

(READ/WRITE)

CYLINDER

LOW

(READ/WRITE)

CYLINDER

HIGH

(READ/WRITE)

SIZE/DEVICE/HEAD REGISTER (READ/WRITE)

STATUS

REGISTER

(READ

ONLY)

ERROR

ENCOUNTERED

(BIT

0)

ECC

CORRECTION

MADE

(BIT

2)

DATA

TRANSFER

REQUESTED

(BIT

3)

SEEK

COMPLETE

(BIT

4)

WRITE

FAULT

(BIT

5)

DRIVE

READY

(BIT

6)

VFW

-

III

BUSY

(BIT

7)

COMMAND

REGISTER

(WRITE

ONLY)

TMA

LEAST

SIGNIFICANT

BYTE

(WRITE

ONLY)

TMA

MOST

SIGNIFICANT

BYTE

(WRITE

ONLY)

TMA

EXTENDED

SIGNIFICANT

BYTE

(WRITE

ONLY)

VFW-III

CONTROL

PORT

(WRITE

ONLY)

8"

FULL

SIZE

FLOPPY

SELECT

(BIT

0)

EXTENDED

HEAD

SELECTION

(BIT

1)

SINGLE DENSITY SELECT {BIT 2)

MOTOR-ON

MODE

(B

IT 3)

TEMPORARY

MASTER

ACCESS

DIRECTION

(BIT

4)

TEMPORARY

MASTER

ACCESS

ENABLE

{BIT 5)

EXTENDED

PROM

DISABLE

(BIT

7)

VFW-III

COMMAND

SET

Type

1 Commands

Restore

Command

Seek

Command

Diagnostic

Test

Command

Type

2 Commands

Read

Command

Readlong

Command

Type

3 Commands

Write

Command

Writelong

Command

Format

Command

3-1

3-1

3-2

3- 2

3-3

3-3

3-3

3-3

3-4

3-4

3-4

3

-4

3-4

3

-4

3-5

3-5

3-5

3-5

3-6

3-6

3

-7

3-7

3-7

3-7

3-7

3-7

3-7

3-8

3-8

3-8

3- 8

3-8

3-8

3-9

3-9

3-9

3-9

3

-9

3-10

3-10

3-

1 0

3-11

3-12

3-12

3-12

3-12

3-13

3-13

3-13

3-13

3-13

)

)

)

)

Subsection

Number

4.0

4.1

4.2

4.2.1

4.2.2

4.2.3

4.3

4.3.l

4.3.2

4.4

4.4.1

4.4.2

4.4.2.1

4.4.2.2

4.4.2.3

4.4.3

4.5

4.5.1

4.5.2

5.0

5.1

5.2

APPENDICES

A

B

c

D

E

F

G

H

I

J

TABLE

OF

CONTENTS--Continued

GENERAL

Title

SECTION

IV

INSTALLATION

POWER

AND

COOLING

CABLES

FLOPPY

DISK

DRIVES

TEST

CONNECTOR

WINCHESTER

DISK

DRIVES

JUMPERS

AND

SWITCHES

JUMPERS

SWITCHES

CALIBRATION

TEST

MODE

FOR

THE

VFW-III

FLOPPY

DISK

CONTROLLER

CALIBRATION

FLOPPY

DISK

WRITE

PRECOMPENSATION

FLOPPY

DISK

READ

PULSE

WIDTH

FLOPPY

VOLTAGE

CONTROLLED

OSCILLATOR

CENTER

FREQUENCY

WINCHESTER

VOLTAGE

CONTROLLED

OSCILLATOR

NON-IEEE-696

BUSSES

PIN

ASSIGNMENTS

DATA

TRANSFER

MODES

GENERAL

SECTION V

SPECIFICATIONS

POWER

REQUIREMENTS

ENVIRONMENT

SELECTED

IEEE-696

SPECIFICATION

SH

EE

TS

DISCLAIMER

LIMITED

WARRANTY

FLOPPY

INTERFACE

WINCHESTER

INTERFACE

PAL

SPECIFICATION

FLOPPY

DISK

DRIVER

SOFTWARE

PARTS

LIST

FOR

VFW-III

PARTS

PLACEMENT

DIAGRAM

SCHEMATIC

Page

No.

4-1

4-1

4-1

4-1

4-2

4-2

4-3

4-3

4-6

4-7

4-7

4-7

4-8

4-8

4-8

4-8

4-9

4-9

4-10

5-1

5-1

5-1

A-1

B-1

C-1

D-1

E-1

F-1

G-1

H-1

I-1

J-1

Figure

No.

2-1

ILLUSTRATION

Title

VFW-III

BLOCK

DIAGRAM

Page

No

.

2-2

)

)

)

)

)

1.0

GENERAL

SECTION

I

INTRODUCTION

The

SDSystems

VFW-III

is

a

high

performance

disk

controller

capable

of

running

both

Winchester

hard

disk

and

floppy

disk

drives.

This

unique

design

brings

together

the

function

of

several

controller

boards

onto

a

single

S-100/IEEE-696

compliant

board.

Winchester

drives

designed

for

the

industry

standard

ST506/412

interface

comprising

up

to

16

read/write

heads

and

floppy

disk

drives

of

single

or

double

density,

single

or

double

sided

and

5.25"

minis

or

8"

full

size

configurations

may

be

controlled

concurrently

by

the

VFW-III.

Data

may

be

interchanged

with

the

controller

via

a

DMA

mode

wherein

the

board

becomes

a

Temporary

Master

capable

of

addressing

any

location

within

the

24

bits

of

address

defined

by

the

IEEE-696

specification,

or

via

a

programmed

I/O

mode

wherein

data

is

sequentially

transferred

through

a

single

port

of

the

controller.

On-board

processors

transfer

sector

data

between

the

internal

sector

buffer

and

the

selected

drive

without

need

of

the

host

processor's

supervision,

thus

freeing

the

host

for

other

activities

such

as

servicing

interrupts.

Automatic

retries.

CRC

generation/verification

and

optional

er

r

or

co

r r e

ct

ion

(on

ha

r d d i s k

tr

ans

f e r s )

of

a

sing

1e ·

bur

s t

error

of

five

bits

ensure

data

integrity

and

further

unburden

the

CPU

from

monitoring

these

events.

1.1

-

FEATURES

Versatile

Disk

Configurations:

Three

varied

5.25"

Winchest

.

er

hard

disk

drives

utilizing

the

ST506/412

interface

with

up

to

16

read/write

heads

may

be

controlled

by

the

VFW-III,

along

with

four

floppy

disk

drives

in

any

mixed

configuration

from

single

sided,

single

density,

5.25"

minis

to

double

sided,

double

density,

8"

full

size

drives.

-

Fully

S-100/IEEE-696

Compliant:

-

When

operating

as

a

Temporary

Master,

the

controller

can

perform

eight

bit

Direct

Memory

Accesses

(DMA)

for

faster

transfers

of

data

between

the

sector

buffer

and

any

memory

location

within

the

extended

memory

addressing

range

of

16Mbytes

(24

bit

addressing).

Data

Integrity:

Single

burst

errors

of

up

to

five

bits

are

automatically

corrected

on

data

received

from

5.25"

Winchester

drives

formatted

in

ECC mode.

Single

burst

errors

of

20

bits

and

double

burst

errors

of

four

bits

can

be

detected

from

a 256

byte

sector.

1-1

-

-

Convenient

Packaging:

By

supplying

the

function

of

two

controllers

in

a

single

board,

the

VFW-III

allows

existing

systems

to

expand

to

Winchester

drives

without

sacrificing

an

S-100

slot

and

allows

new

systems

to

get

more

system

performance

into

small

card

cages.

Two

regulators

and

heatsinks

have

been

used

to

assure

adequate

cooling

even

under

conditions

where

the

8

volts

unregulated

input

is

at

its

IEEE-696

maximum

value

of

11

volts

DC.

Care

has

been

taken

to

place

all

cable

connectors

along

the

top

edge

of

the

board

for

optimum

access.

Flexible

Data

Storage

and

Transfers:

Sector

sizes

of

128,

256,

512

and

1024

bytes

and

physical

placement

of

the

logical

sectors

for

interleaving

are

both

software

selectable.

The

VFW-III

processors

supervise

a1·1

disk

to

on-board

single

sector

buffer

transfers,

requiring

only

that

the

host

CPU

issue

the

command

sequence

and

later

evaluate

the

command

completion

status.

When

Temporary

Master

OMA

transfers

are

used,

a

completion

interrupt

may

be

issued

after

all

sectors

have

transferred

between

the

host

memory

and

the

selected

drive.

Using

programmed

I/O

mode

requires

the

host

CPU

to

move

sector

data

between

the

on-board

buffer

and

host

memory.

-

Interruptable

Data

Transfers:

When

operating

the

VFW-III

under

programmed

I/O

transfer

mode,

interrupts

may

be

serviced

in

the

middle

of

a

sector

buffer

to

host

transfers.

On

board

processors

transfer

sector

data

between

the

internal

:·

sector

buffer

and

the

selected

drive

without

need

of

the

host

processor's

supervision.

In

this

mode

of

operation,

no

interrupts

need

be

missed.

1.2

SCOPE

OF

THIS

MANUAL

I

This

manual

is

divided

into

five

sections,

each

directed

toward

a

need

of

the

user.

Section

I

summarizes

the

board's

features

and

defines

the

structure

of

the

manual.

Section

II

defines

terms

involved

in

disk

operation,

basic

flow

of

information

on

the

VFW-III

and

location

of

various

circuits

on

.

the

schematics.

It

is

written

with

the

novice

in

mind

and

is

an

easy

introduction

into

rotating

media

storage

devices.

Information

required

to

write

or

modify

a

software

driver

is

presented

in

Section

III.

It

includes

the

memory

map

of

the

controller

and

the

command

set

to

it.

Sectio~

IV

contains

all

information

required

to

physically

install

the

board

into

an

existing

system

and

the

power

and

cooling

requirements

of

the

board

• .

specifications

of

the

VFW-III

are

listed

in

the

last

section.

Reference

material

is

located

in

the

appendices.

]

.

. I

I .

1-2

)

)

--

2.

0 GENERAL .

SECTION

II

THEORY

OF

OPERATION

Section

II

is

intended

to

be

used

as

a

light

tutorial

on

the

S-100

computer

bus,

the

Winchester

and

floppy

disk

drives,

and

the

interface

that

connects

them

together.

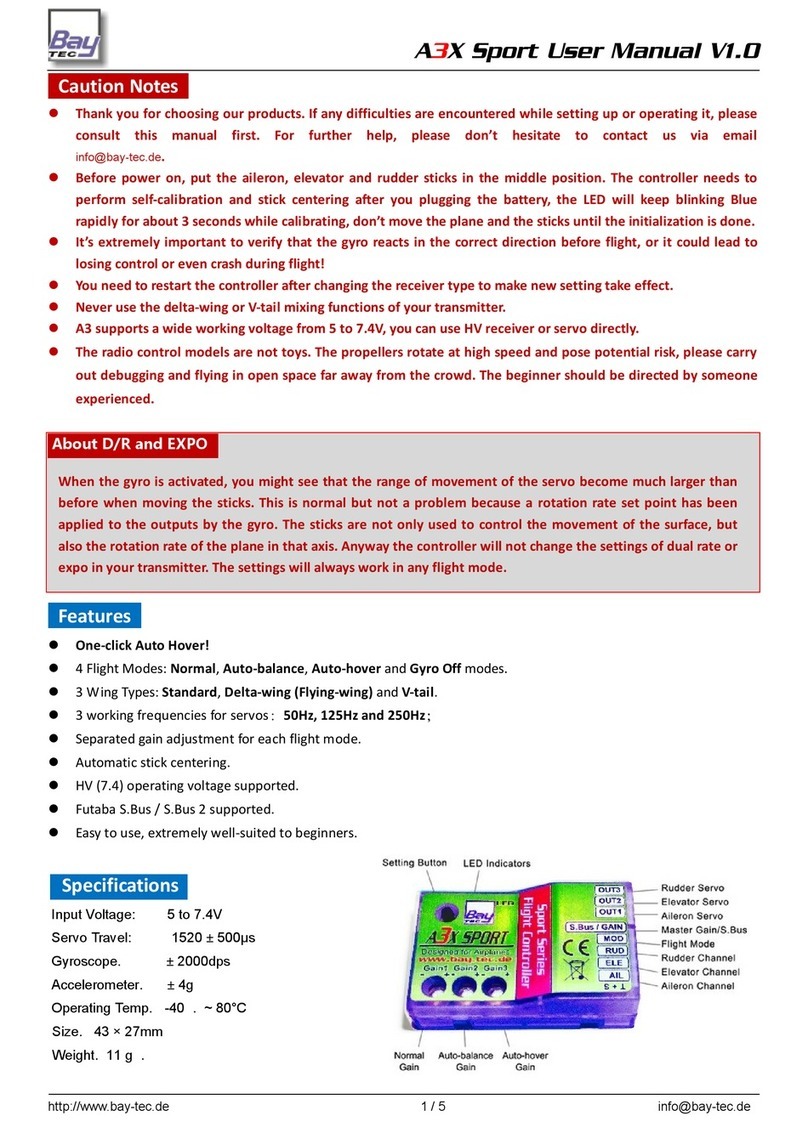

The

block

diagram

(Figure

2-1)

illustrating

the

functions

of

the

VFW-III

is

discussed

in

Section

II,

Subsection

2.4.

2.1

S-100

COMPUTER

BUS

The

S-100

computer

bus

has

a

100

pin

parallel

backplane.

This

means

that

the

slot

in

which

a

board

is

plugged

into

the

bus

is

inrnaterial.

Information

required

for

any

card

on

the

bus

is

pr

·

esented

to

every

location.

An

addressing

scheme

is

used

to

specify

which

board

is

to

respond

to

the

following

bus

cycle.

The

S-100

defines

two

basic

transfers;

the

memory

access

and

the

input/output

(I/O)

device

access.

The

address

of

a

memory

location

can

be

either

16

or

24

bits

long

for

either

65,536

or

16,777,216

memory

locations.

The

address

of

an

I/O

port

can

be

either

8

or

16

bits

long

for

a

range

of

256

or

65,536

locations.

S-100

boards

monitor

the

bus·

for

an

address

within

the

range

of

locations

which

it

alone

contains.

Once

selected

by

the

address,

a

board

w.

ill

perform

the

command

presented

on

the

control

lines.

All

addressing

is

done

by

one

board

at

a

time;

either

the

permanent

master

or

one

of

16

temporary

masters.

The

permanent

master

is

usually

the

main

CPU

and

will

relinquish

the

bus

using

a

priority

scheme

that

ensures

that

only

one

master

is

controlling

the

bus

at

a

given

time.

The

VFW-III

can

speed

data

across

the

bus,

avoiding

the

two

step

process

w

herein

the

CPU

first

·

reads

fr

om

the

controller

and

second

writes

into

memory,

by

becoming

a

temporary

master.

This

allows

the

VFW-III

to

transfer

data

directly

between

its

single

sector

buffer

and

any

memory

location

within

in

a

range

of

16,777,216

locations.

Data

transferred

in

this

fashion

is

quicker

but

may

not

be

chosen

for

an

application

where

real-

time

interrupts

must

be

handled

quickly.

TMA

transfers

disable

the

CPU

from

accessing

the

bus

to

service

a

pending

interrupt

until

after

the

current

sector

is

transferred.

Operating

the

controller

in

a

programmed

I/O

mode,

where

the

CPU

always

controls

the

bus

and

moves

data

in

the

slower

two-

step

process

described

above,

allows

immediate

access

to

the

bus

for

servicing

interrupts

in

the

middle

of

data

transfers

without

disturbing

them.

In

this

mode,

all

transfers

made

with

the

controller

are

I/O

transfers.

2-1

ZONE 1-WINCHESTER CONTROL

ZOHE

2-8UFFER

CONTROL

ANO

SUPPORT LOGIC

ZONE

3-

STATUS ANO CONTROL POAT

ZONE,-BASIC

$100

INTERFACE

ZONE

S-TMA

INTERFACE

ZOHE6-CONTAOL

PROCESSOA

ZONE

7-FLOPPY

DISK INTERFACE

S'IOO

ZONE 1

INnANAL

DATA

BUS

WINCHESTER

INTERFACE ANO

DATA

SEPARATOR

I

I

WD1010 WINCHESTER

DISK CONTROLLER

-

--

-

-

--

VFW-III

llOCk

DIAGRAM

-

J4

-

Je

J7

.

J8

INTERNAL

CONTROL BUS

51110

.......

--- - -----_

....

-

--

---

---

~

._.

.-..

.....

--

.--.

--

._

-

_.

--

--

W010~

ERROR

ZONE2

--OETECTtON ·suPPORT --

LOGIC

• t

SECTOR

ADDRESS

---

-

BUFFER COt.NTER

......

~

- -

._.

--

- - --

_._

-,._.,_

_.

-.

- - .._.,

._

-

.....

-.

-- -

--

..._,

---

...-

ZONE 3 CONTROL PORT STATUS PORT

--------~-

-

--

-

...

~

--------

-~

-

._.

.-

-- -

-.

~

-

--

DATA

aus

CONT9'0l

•us

. ---

INTERFACE

ZONE4..._

______________

~

INTERFACE

....

--

~

-- - --

--

-

-~

-- -

---

~

_.

- - -

...

~

- -

.....

~

.-

-.

._.

-

......

-

TEMPORARY

MA.STEA

-

OMA

--

~ONE

5

A.ODRESS

INTERFACE

TEMPORAR'f'

MASTER

OMA

COHTAOl

INTERFACE --

~

--

- - -

-- --

-

--

-

...

._

-

.....

._.

--- - -

--~

---

--

- - -

.,...._.

--

W01015

ZONE 8 -. CONTROL

PA()CS:f;"""~-:;c-,..

.....

_~

ADDRESS ANO

-CONTROL

LATCH

•

-

CONTROl

PROCESSOR

EXTERNAL PROM

ii---

.-.

- -

---

~

- - - -

---

- -

._._.

~

.....

...._..

- - -

-~

- - -

__.

~

.....

- -

....

-

ZONE 7

5100

INTERHAL

~TA

BUS

Figure

2-1.

--

W02797

FLOPPY

OtSI'.

CONTROLLER

I I

1

A..OPf>Y 01$1(

INTERFACE

.•

INTERNAL

COHTROl

BUS

:.

J2

...

-------~J

3

VFW-III

BLOCK

DIAGRAM

2-2

$100

)

)

An

interrupt

bus

is

defined

under

the

S-100

to

stop

the

CP

U

to

quickly

do

a

time-dependent

routine

transparent

to

the

present

task.

In~errupts

are

commonly

used

to

get

the

CPU

to

transfer

data

with

an

input/output

device

and

are

more

efficient

than

polling

status

loops

where

many

wasted

reads

are

made

until

the

status

changes,

signalling

an

operation

needed

to

take

place.

Status

loops

seldom

respond

as

quick

as

interrupts.

Data

lines

exist

for

moving

either

8

bit

bytes

or

16

bit

words

during

memory

or

I/O

transfers.

All

data

transfers

to

or

from

the

VFW-III

will

be

8

bit

byte

length

only

•

.

2.2

WINCHESTER

DISK

DRIVES

Winchester

disk

drives

are

rotating

memory,

random

access

storage

devices

which

fulfill

the

need

for

fast,

large,

on-

line

data

storage

and

retrieval.

The

word

Winchester

a c·t u a

11

y r e f e r s t o

th

e t e c hn o1 o gy .

of

.

the

ni c ke

1-

z i nc

formulated

read

·

/write

head,

but

is

commonly

used

to

refer

to

5.25"

hard

disk

drives.

The

term

"Winchester

disk

drive"

is

used

interchangeably

with

•hard

disk

drive"

throughout

this

manual.

A

hard

disk

drive

is

a

device

which

allows

access

to

data

stored

magnetically

within

a

vertical

stack

of

several

magnetic

coated

disks

or

platters.

The

stack

is

continuously

spinning

at

speeds

roughly

12

times

as

fast

as

a

floppy

disk

drive

with

the

read/write

heads

aerodynamically

"flying"

microns

above

each

sur

·f

ace

in

the

stack

(two

heads

pe

r

platter;

top

and

bottom).

All

heads

are

attached

to

an

assembly

som~times

called

an

actuator

ara,

which

can

be

controlled

to

position

the

heads

in

or

out

along

·

the

radii

of

the

stack.

At

any

given

position

of

the

read/write

heads,

the

magn~tic

media

spinning

below

it

that

could

be

read

or

written

would

trace

out

a

circle

on

the

media.

This

circle

is

called

a

track.

At

each

position

of

the

actuator

arm,

its

associated

track

is

assigned

a

trac

·k

number.

Track

numbe

·

rs

range

from

zero

at

the

outermost

concentric

circle

to

the

maximum number

located

nearest

the

stack

axis.

The movement

of

.

the

actuator

arm

from

one

track

to

another

is

termed

a

seek

and

is

issued

by

the

controller

as

a

series

of

pulses

called

steps.

The

time

required

to

electically

switch

from

one

read/write

head

to

·

another

·

above

o·r

below

it

is

considerably

less

than

the

time

taken

to

seek

from

one

track

to

its

neighboring

~rack.

For

this

reason,

when

the

end

of

one

track

has

been

reached,

the

continuation

of

information

will

be

found

on

the

same

track

number

but

on

the

next

higher

head

number.

The

vertical

stack

of

tracks

accessed

by

all

the

heads

of

the

actuator

arm

is

referred

to

as

a

cylinder.

Information

in

the

present

cylinder

can

be

accessed

the

quickest.

When

consecutive

data

passes

the

end

of

a

cylinder

boundary,

a

seek

must

be

issued

and

the

head

number

is

reset

to

zero.

2-3

The

OEM

manual

or

product

specification

of

every

drive

gives

the

unformatted

capacity

of

the

entire

drive

and

of

an

individual

track.

This

is

the

number

of

locations

where

bits

of

information

may

reside.

Since

each

of

these

bits

cannot

be

uniquely

addressed,

a

method

is

used

that

sacrifices

some

of

the

bits

to

identify

blocks

of

continuous

data.

While

this

scheme

is

common

among

controller

manufacturers,

the

identification

blocks

must

be

identical

to

allow

information

written

by

one

company's

controller

to

be

read

by

another's.

Th

e

VF

w- I I I

use

s a

wester

n Dig

it

a1 40

pin

ch

i p

to

hand

1e

th

e

foraatting

or

writing

of

the

pattern

required

for

subsequent

reads

and

writes.

As

this

chip

gains

popularity

in

the

market

place,

com

pa

tibili

ty

among

control

le

rs

w

il

1

increase.

It

is

important

to

point

out

that

more

is

involved

than

the

physical

access

·

to

the

old

data.

The

driving

software

·

must

also

be

compatible.

Each

track

is

subdivided

into

units

called

sectors.

The

data

field

which

contains

the

information

to

be

read

or

written

is

accompanied

by

an

identification

or

ID

field

and

gaps

before,

between

and

following

these

fields.

The ID

field

contains

the

"address"

of

the

sector

and

includes

the

cylinder

number,

the

head

number

and

the

sector

number.

This

is

the

information

that

the

Central

Processing

Unit

(CPU)

or

host

processor

must

provide

to

the

controller

board

in

order

to

transfer

the

associated

data

field.

The

controller

takes

all

action

nessessary

to

locate

the

target

sector

and

transfer

the

data

field

between

the

drive

and

the

controller's

on-board

single

sect

or

buff

er.

All

tr

an

sf

e

rs

be

tween

the

ho

st

and

.

the

controller

are

independent

of

transfers

between

the

controller

and

the

drives.

This

means

that

the

host

needn't

be

"locked-

up"

as

it

waits

to

move

data

directly

with

the

drive

as

·

some

controllers

require.

If

programmed

I/O

·mode

is

used

to

move

data

with

the

controller,

any

higher

level

interrupts

or

conditions

requiring

immediate

action

may

be

handled

in

..

the

middle

of

the

transfer,

only

to

complete

it

after

the

interrupt

has

been

serviced.

An

index

pulse

is

used

to

the

controller

when

a

reference

radius

of

the

disk

stack

passes

below

the

read/write

heads.

This

reference

is

used

to

initiate

formatting

physical

sectors,

which

are

the

actual

·

sector

fields

placed

consecutively

along

the

track.

To

increase

the

throughput

or

average

rate

at

which

information

is

transferred

on

a

track,

a

technique

known

as

sector

interleaving

is

used.

If

physical

sectors'

ID

fields

contain

consecutive

numbers

(an

interleave

factor

of

1),

a

dilemma

occurs

when

two

sectors

are

to

be

read.

As

the

first

sector

spins

under

the

.

read/write

head,

its

ID

field

matches

the

target

sector,

and

the

following

data

field

is

transferred

into

the

controller's

single

sector

buffer.

When

the

last

bytes

of

data

are

read

in,

the

cont

·

roller

begins

to

move

the

saved

data

into

the

host

system's

memory,

at

the

same

time

that

the

next

target

sector

is

spinning

past

the

read/write

head.

The

disk

controller

2-4

)

)

)

then

returns,

looking

for

the

next

target

sector's

ID

field,

and

now

must

wait

a

full

revolution

for

it

to

spin

under

•

again.

Sector

interleaving

makes

a

distinction

between

the

physical

sector

and

the

logical

sector.

A

logical

sector

is

the

next

sector

that

the

system

would

request,

but

its

position

is

staggered

around

the

disk

so

that

while

the

buffer

is

moved

into

the

host,

unwanted

sectors

spin

below

the

read/write

head.

Shortly

after

the

controller

returns,

searching

for

the

next

logical

sector,

it

spins

under

the

head.

The

minimum

interleave

factor

the

VFW-III

handles

on

a

Winchester

is

3;

every

third

physical

sector

is

the

next

logical

sector.

The

table

below

illustrates

an

imaginary

case

where

16

sectors

of

512

bytes

length

are

formatted

with

an

interleave

factor

of

3.

Physical

Sector

1 2 3 4 5 6 7 8 9

10

11

12

13

14 15

16

Logical

Sector

1

12

7 2

13

8 3

14

9 4

15

10

5 16 11 6

1st

Revolution

1 • • 2 • • 3 • • 4 • • 5 • • 6

2nd

Revolution

• • 7 • • 8 • • 9 • •

10

• •

11

•

3rd

Revolution

•

12

• • 13 • •

14

• •

15

• • 16 • •

This

shows

that

the

entire

track

can

be

read

in

3

revolutions

with

an

interleave

factor

of

3

as

opposed

to

16

revolutions

(1

per

sector)

for

an

interleave

factor

of

1

or

2.

This

increases

the

throughput

by

5.3

times.

The

interleave

factor

is

set

only

when

a

drive

is

formatted

and

is

software

selectable

as

explained

in

Section

IV.

An

important

misconception

about

the

interleave

factor

is

that

it

should

always

be

set

to

the

minimum

value

handled

successfully

by

a

disk

controller.

The

proper

interleave

factor

is

dependent

not

only

upon

the

time

it

takes

the

controller

to

empty

its

sector

buffer,

but

also

upon

the

average

time

between

consecutive

sector

requests.

This

time

may

be

lengthened

by

interrupt

servicing

or

other

computations

between

sectors,

as

may

occur

when

searching

files.

If

it

is

set

too

low,

the

next

sector

will

spin

under

before

the

controller

begins

searching

again,

resulting

in

1

sector

per

revolution.

This

throughput

is

much

more

noticeable

on

flopy

disk

drives

where

the

magnetic

media

is

spinning

12

times

slower.

The

proper

procedure

for

determining

the

interleave

factor

is

to

run

benchmarks

or

timing

tests

in

the

final

system

using

typical

application

software.

2.3

FLOPPY

DISK

DRIVES

A

floppy

disk

drive

can

be

considered

to

be

a

simpler

version

of

the

hard

disk

drive

discussed

in

Section

II,

Subsection

2.2.

Only

one

removable

magnetic

disk

is

used

in

a

floppy

drive.

A

flexible

plastic

jacket

protects

and

supports

the

media

and

has

an

open

slot

on

front

and

back

for

the

one

or

two

read/write

heads.

Track

densities

are

roughly

1/3

to

1/10

that

of

hard

disk

drives

and

rotational

speeds

are

1/12.

Data

2-5

..

is

stored

on

the

media

using

the

same

method

described

for

)

Winchesters

(ID

fields,

data

fields,

gaps

and

interleave

factors).

Floppy

drives

vary,

but

their

characteristics

are

usually

some

combinations

of

the

following:

5.25~

or

8"

sized

diskettes

and

drives.

Single

or

double

density

recording

(FM

or

MFM).

Single

or

double

sided

drives

(1

or

2

heads).

48

or

96

tracks

per

inch

track

density.

The

VFW-III

can

handle

a

total

of

four

floppy

drives

in

any

combination

of

the

above

characteristics

with

the

appropriate

driving

software.

·

Removability

is

perhaps

the

greatest

advantage

of

floppy

disks.

Large

amounts

of

data

may

be

backed-up

or

saved

as

redundant

copies.

The

portability

of

·

the

diskette

makes

it

a

convenient

way

of

transferring

information

between

computers.

Eight

inch

single

sided,

single

density

format

is

one

of

the

few

controller

independent,

standard

formats.

Using

this

format,

files

may

be

transferred

to

diverse

computer

systems.

2.4

VFW-III

DISK

CONTROLLER

The

VFW-III

is

a

single

board,

six

layer

disk

controller

capable

of

interfacing

three

hard

disk

drives

and

four

floppy

disk

drives

with

minimal

software

differences.

It

is

designed

around

the

Western

Digital

4

chip

set:

the

WD1010,

WD1014,

WD1015

and

WD2797.

On-board

processors

and

sector

buffer

make

the

board

more

bus

efficient,

handling

all

disk

·

actions

necessary

to

locate

the

target

sector

specified

by

the

CPU.

Error

detection

and

correction

are

done

by

the

controller's

processors

and

require

no

work

or

supervision

of

the

host.

The

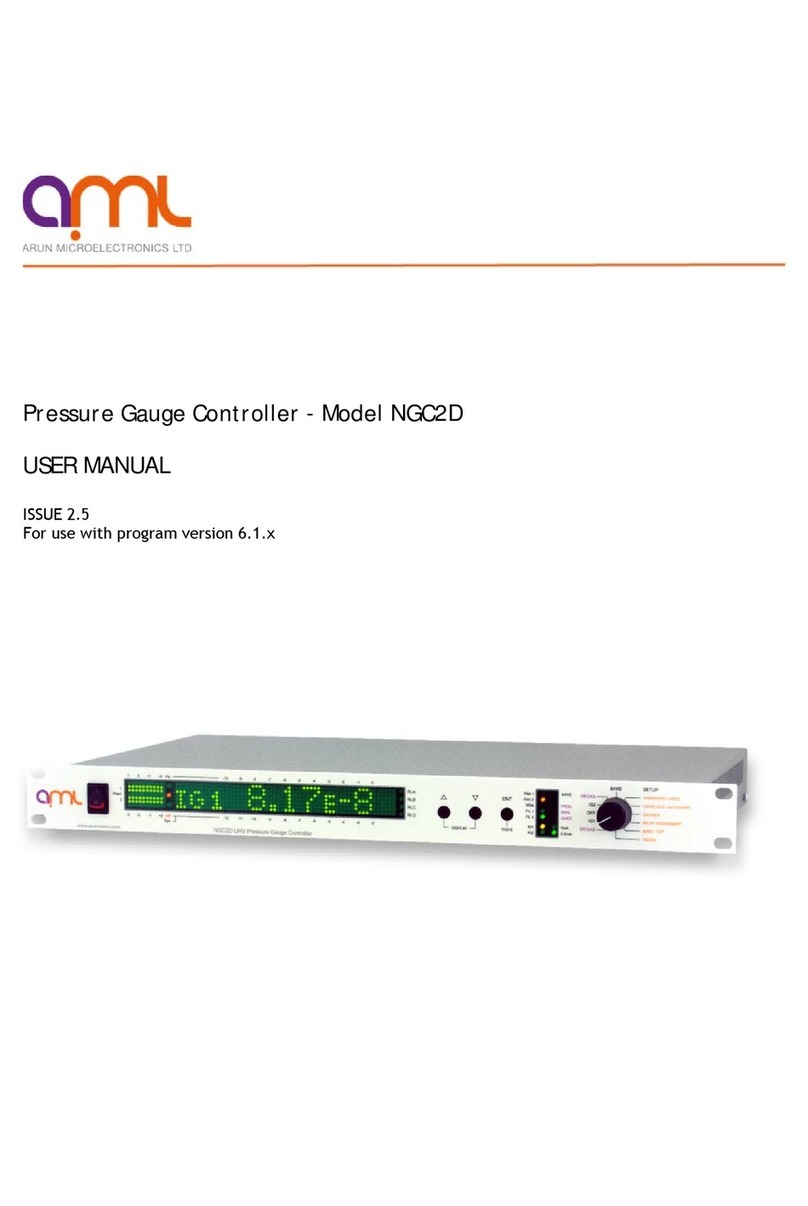

block

diagram

for

the

VFW-III

shows

connection

to

three

busses:

the

S-100,

the

internal

data

bus

and

an

internal

control

bus.

Note

that

the

S-100

bus

is

drawn

on

both

sides

for

·

clarity.

Function

has

been

divided

into

seven

zones

vertically

and

each

is

discussed

in

the

following

subsections.

2.4.1

Zone

1:

Winchester

Control

The

heart

of

the

Winchester

control

circuit

is

the

WD1010

Winchester

Disk

Controller.

This

circuit

is

located

on

the

schematic

on

Sheets

4

and

5

and

provides

the

hard

disk

drive

positioning

logic,

write

precornpensation

logic

and

the

data

separator.

The

three

drives

are

daisy-chained

to

the

control

connector

J4

for

selection.

positioning

and

status

signals-'

Connectors

JS,

J6

and

J7

link

drives

1,

2

and

3,

respectively,

)

to

transfer

high

frequency

read

and

write

data

along

differential

1

ines.

J·umper

3,

used

in

conj

unction

with

bit

2

2-6

of

the

control

port

(BASE+

OB),

can

be

used

to

extend

the

h~ad

addressing

to

4

bits

or

16

heads.

New

drives

utilizing

smaller

Whitney

read/write

heads

and

internal

spindle

motors

are

making

more

than

lOOMbytes

of

data

available

in

a

single

standard

size

5.25"

drive.

2.4.2

Zone

2:

Buffer

Control

And

Support

Logic

.

...

.

..

...

--. . -

.,,

.

....

-,

~

.._

..

This

circuit

is

located

on

the

top

half

of

Sheet

2

of

the

schematic.

The

WD1014

Error

Detection/Support

Logic

calculates

the

four

bytes

of

appended

ECC

syndrome

as

data

to

be

moved

to

or

from

the

sector

buffer

which

it

controls.

Assorted

other

signals

are

decoded

within

the

WD1014

save

space

on

the

board.

The

address

counter

to

the

sector

buffer

is

automatically

incremented

after

every

access

and

cleared

when a command

is

issued

to

the

command

port

at

location

BASE

+

07H~

2.4.3

Zone

3:

Status

And

Control

Port

Located

at

the

top

left

of

Sheet

1

and

the

top

center

of

Sheet

3

of

the

schematic,

this

circuit

is

used

by

the

host

to

determine

what

the

status

of

the

board

is

and

to

define

parameters

for

the

next

disk

access.

Section

IV,

Subsections

4.1.9

and

4.1.14

define

their

use

in

detail.

2.4.4

Zone

4:

Basic

S-100

Interface

Sheet

1

and

the

left

side

of

Sheet

3

of

the

schematic

contain

this

circuitry.

Address

decoding,

data

bus

buffering,

interrupts,

resets,

wait

states

and

power

are

the

functions

handled

by

this

interface.

Twelve

ports

are

mapped

onto

this

controller,

and

it

decodes

standard

input/output

device

addressing

as

specified

by

the

IEEE-696.

All

data

transfers

are

eight

bits

wide,

one

software

definable

vectored

interrupt

may

be

selected

and

on-board

reset

may

follow

either

pin

75

or

99.

Jumper

20,

when

installed,

will

assert

two

wait

states

for

every

port

access

to

the

board.

This

is

used

for

operation

on

a 6 MHz

bus.

2.4.5

Zone

5:

TMA

Interface

Most

of

Sheet

1

of

the

schematic

is

used

to

control

temporary

master

access

on

the

S-100

bus.

The

loadable

address

counters

are

used

to

select

host

memory

for

data

transfers.

The

two

buffers

are

used

to

control

or

hold

the

status

and

control

signals

of

the

bus

during

TMA,

and

the

two

programmable

logic

arrays

are

used

to

handle

TMA

priority

resolution,

and

then

to

control

both

the

internal

and

external

busses.

2.4.6

Zone

6:

Control

Processor

The

control

processor

circuit

on

the

lower

half

of

Sheet

2

is

designed

around

the

WD1015.

This

device

intercepts

commands

from

the

bus

and

converts

them

to

what

would

·

be

required

by

2-7

either

the

Winchester

or

floppy

contoller

chips.

The

external

PROM

enhances

the

internal

program,

offering

more

formats

to

be

supported.

The

address

latch

is

used

both

to

address

the

PROM

and

to

address

the

other

40

pin

chips.

Data

is

moved

on

the

internal

data

bus

by

the

control

processor

between

the

sector

buffer

and

the

Winchester

·

and

the

floppy

controllers.

When

ECC

errors

less

than

or

equal

to

five

bi~s

are

detected,

the

WD1015

will

perform

the

correction

within

the

sector

buffer

before

passing

it

on

to

the

host.

2.4.7

Zone

7:

Floppy

Disk

Interface

The

floppy

disk

interface

on

Sheet

3

allows

control

of

both

8"

and

5.25"

drives

of

either

density

or

head

count.

Drives

are

connected

to

J2

and

J3

for

5.25"

and

8",

respectively.

Since

both

cables

are

electrically

common,

unique

unit

numbers

must

exist

on

both

cables

and

only

one

terminator

may

be

connected

•

•

2-8

)

)

)

3.0

GENERAL

..

SECTION

III

SOF'IWARE

DRIVERS

This

section

is

intended

to

supply

all

necessary

information

to

write

or

modify

a

software

driver

for

the

SDSystems

VFW-III.

Provided

herein

are

the

complete

memory map

of

the

controller

and

the

command

set

for

the

commands.

3.1

MEMORY

MAP

The

VFW-III

is

mapped

onto

the

S-100/IEEE-696

using

Standard

Input/Output

Device

Addressing.

Address

lines

A7

through

A4

are

compared

with

the

I/O

base

address

set

by

SWl

positions

5

through

8

to

determine

if

the

board

is

to

be

selected.

If

so,

address

lines

A3

through

AO

are

needed

to

select

locations

within

the

memory map

of

the

controller.

These

16

locations

are

illustrated

in

the

following

table

as

offsets

from

the

base

address.

--------------------------------~------------------------------

I/O

Address

Read

Access

Write

Access

-----------------~-----

...

----------------------------------------

BASE+OO

BASE+Ol

BASE+02

BASE+03

BASE+04

BASE+OS

BASE+06

BASE+07

BASE+O

8

BASE+09

BASE+OA

BASE+OB

BASE+OC

BASE+OD

BASE+OE

BASE+OF

Sector

buff

er

Error

register

Sector

count

Sector

number

Cylinder

low

Cylinder

high

Size/device/

head

register

Status

register

Not

selected

Not

selected

Not

selected

Not

selected

Not

selected

Not

selected

Not

selected

Not

selected

Sector

buffer

Write

precompensation

cylinder

Sector

count

Sector

number

Cylinder

low

Cylinder

high

Size/device/head

register

Command

register

DMA

address

least

significant

byte

DMA

address

most

significant

byte

DMA

address

extended

significant

byte

VFW-III

control

port

Not

selected

Not

selected

Not

selected

Not

selected

____

...

_______________________________________

i-.

__________________

__

Note

that

when

connecting

W20

to

enable

two

wait

states

for

6

MHz

operation,

the

controller

will

also

assert

the

wait

for

address

BASE+OC

through

BASE+OF,

even

though

these

locations

are

not

used.

Other

I/O

cards

requiring

wait

states

for

6 MHz

but

not

incorporating

them

within

their

designs

may

be

mapped

here.

3-1

3.1.l

Sector

Buffer

(Read/Write

And

Increment)

A

lK

byte

wide

sector

buffer,

capable

of

containing

only

one

sector

regardless

of

sector

size,

is

mapped

into

location

BASE+OO.

Except

for

READLONG

and

WRITELONG

commands,

all

access

to

this

location

must

be

by

block

transfers

equal

in

length

to

the

sector

size,

using

the

quicker

DMA

mode

or

programmed

I/O

mode.

On-board

counters,

which

are

reset

at

the

issuance

of

a

command.

address

the

Random

Access

Memory

(RAM),

consecutively

incrementing

the

address

after

each

access.

In

programmed

I/O

mode,

this

port

is

simply

continuously

read

or

written

by

the

host

processor

until

a

full

sector

length

is

transferred.

In

DMA

mode,

the

transfer

of

data

between

the

host's

memory

and

the

sector

buffer

is

handled

by

making

the

VFW-III

a

temporary

master.

Provided

that

the

absolute

address

has

been

loaded

into

registers

BAS

E+O

8,

+O

9

and

+OA

and

that

the

control

port,

BAS

E+O

B,

has

enabled

DMA

mode

and

selected

the

proper

direction,

then

the

controller

will

move

the

data

around

without

need

of

the

processor.

3.1.2

Error

Register

(Read

Only)

.

In

addition

to

normal

error

reporting,

this

register

will

also

hold

the

results

of

on-board

diagnostics

initiated

by a

power-

up

or

by a

test

command. The

diagnostic

sequence

starts

with

the

WD1015

and

progresses

to

the

WD2797

or

until

the

first

error

occurs

wherein

the

error

code

is

posted

and

the

test

)

terminated.

Error

codes

for

the

internal

diagnostics

and

their

meaning

are

tabulated

below.

Note

that

the

error

bit

of

the

status

register

will

never

indicate

an

error

at

the

completion

of

the

diagnostics.

--------------------------------------------------------------

Error

Code

Meaning

--------------------------------------------------------------

0

All

diagnostics

ran

error-free;

test

passed

1

Error

found

within

the

WD2797

Floppy

Disk

Controller

2

Error

found

within

the

WD1010

Winchester

Disk

Controller

3

Error

found

within

the

sector

buffer

4

Error

found

within

the

WD1014

or

internal

bus

5

Error

found

within

the

WDlOlS

Control

Processor

--------------------------------------------------------------

The

error

register

is

also

used

to

determine

the

type

of

error

encountered

during

the

last

command

and

is

only

val

id

if

the

status

register

(Section

III,

Subsection

3.1.9)

indicates

an

error

exists.

An

active

high

bit

specif

icies

the

errors

illustrated

in

the

following

table.

3-2

) l

)

...

------------------------

Bit

Error

-------------------------

0

2

4

6

No

data

address

mark

Command

aborted

ID

field

not

found

Incorrectable

error

--------------------------

3.1.2.1

No

Data

Address

Mark

--------------------------

Bit

Error

-----------------~-------

1

3

5

7

Track

0

not

found

Not

used

Not

used

Bad

block

detect

-------

....

----~-------------

A

no

data

address

mark

error

occurs

if,

after

successfully

finding

the

target

sector's

ID

field

or

header,

the

subsequent

byte

marking

the

beginning

of

the

sector's

data

field

is

not

found

with

16

bytes.

Possible

caused

of

this

error

include:

bad

diskette,

media

flaw

after

the

ID

field,

or

controller

out

of

calibration.

3.1.2.2

Track

0

Not

Found

Both

floppy

and

Winchester

drives

assert

a

signal

when

their

read/write

heads

are

on

track

O.

During

a

restore

command,

this

signal

is

used

to

put

the

read/write

heads

in

a

known

position

by

continuously

stepping

to

a

lesser

track

number

and

then

testing

the

track

0

signal.

If

the

drive

does

not

assert

the

signal

before

1024

steps

are

attempted,

the

VFW-III

will

post

this

error.

One

probable

reason

for

receiving

the

error

in

conjunction

with

Winchester

operation

is

that

jumper

W21

is

not

connecting

C-2,

meaning

the

common

line

jumpered

to

option

2

as

shipped

from

the

factory.

The

jumper

corrects

a

design

flaw

in

the

LSI

chip

WDlOl0-00

Control

Processor

that

made

it

incompatible

with

drives

that

did

not

deactivate

the

signal

SEEK

COMPLETE

on

the

rising

edge

of

step.

Other

possible

reasons

for

this

error

are

a

bad

cable

.

connection

or

a

drive

that

has

not

had

its

read/write

heads

unlocked

after

shipping.

Note

that

few

5.25"

Winchester

drives

use

head-locking

for

transport.

3.1.2.3

Command

Aborted

Certain

conditions

must

be

reported

by

the

disk

drive

before

the

operation

of

a

valid

command

can

commence.

Failure

of

these

conditions

results

in

the

po~ting

of

this

error

by

the

VFW-III.

Interrogation

of

the

status

register

will

show

one

of

the

following

signals

in

an

abnormal

state.

3.1.2.3.1

Status

Register

Bit

6:

Ready

The

normal

state

for

this

signal

is

active

high,

which

indicates

that

the

drive

is

ready

to

read,

write

or

seek.

When

a

drive

is

disconnected,

powered

down

or

spinning

up,

this

signal

is

inactive

and

forces

an

error

if

a

command

is

sent

to

it.

3-3

Table of contents