SiFive E300 User manual

SiFive E300 Platform Reference Manual

Version 1.0.1

c

SiFive, Inc.

2SiFive E300 Platform Reference Manual, Version 1.0.1

SiFive E300 Platform Reference Manual

Proprietary Notice

Copyright c

2016, SiFive Inc. All rights reserved.

Information in this document is provided “as is”, with all faults.

SiFive expressly disclaims all warranties, representations and conditions of any kind, whether ex-

press or implied, including, but not limited to, the implied warranties or conditions of merchantabil-

ity, fitness for a particular purpose and non-infringement.

SiFive does not assume any liability rising out of the application or use of any product or circuit, and

specifically disclaims any and all liability, including without limitation indirect, incidental, special,

exemplary, or consequential damages.

SiFive reserves the right to make changes without further notice to any products herein.

Release Information

Version Date Changes

1.0.1 Dec 19, 2016 Minor clarifications on PWM, SPI, AON register fields

1.0 November 29, 2016 Initial release for HiFive1 release.

i

ii SiFive E300 Platform Reference Manual, Version 1.0.1

Contents

SiFive E300 Platform Reference Manual i

1 Introduction 1

1.1 BlockDiagram .......................................... 1

1.2 Configurable E31 RISC-V Coreplex . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.3 CustomAccelerators....................................... 2

1.4 On-ChipMemory......................................... 2

1.5 Execute-in-Place Quad-SPI Flash controller . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1.6 PeripheralDevices........................................ 3

1.7 Platform-Level Interrupt Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1.8 Always-On Block and Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1.9 DebugSupport.......................................... 3

1.10 SoftwareTools .......................................... 3

2 E300 Platform Memory Map 5

3 E300 Power Modes 7

3.1 RunMode............................................. 7

3.2 WaitMode ............................................ 7

3.3 SleepMode............................................ 7

4 E300 Clock Generation 9

4.1 ClockGenerationOverview................................... 9

4.2 Internal Trimmable Programmable 72 MHz Oscillator (HFROSC) . . . . . . . . . . . . . . 9

4.3 External 16 MHz Crystal Oscillator (HFXOSC) . . . . . . . . . . . . . . . . . . . . . . . . 11

4.4 Internal High-Frequency PLL (HFPLL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

4.5 PLLOutputDivider........................................ 13

4.6 Internal Low-Frequency Oscillator (LFRCOSC) . . . . . . . . . . . . . . . . . . . . . . . . 13

4.7 External 32.768 kHz Low-Frequency Crystal Oscillator (LFXOSC) . . . . . . . . . . . . . 13

iii

iv SiFive E300 Platform Reference Manual, Version 1.0.1

5 E300 Always-On (AON) Domain 15

5.1 AONPowerSource ....................................... 15

5.2 AON Clocking and Tilelink Slave Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

5.3 AONResetUnit ......................................... 15

5.3.1 Power-OnResetCircuit ............................... 16

5.3.2 ExternalResetCircuit ................................ 16

5.3.3 ResetCause ..................................... 17

5.4 WatchdogTimer(WDT)..................................... 17

5.5 Real-TimeClock(RTC) ..................................... 17

5.6 BackupRegisters ........................................ 17

5.7 Power-Management Unit (PMU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5.8 AONMemoryMap........................................ 17

6 E300 Power-Management Unit (PMU) 19

6.1 PMUOverview.......................................... 19

6.2 PMU Key Register (pmukey)................................... 19

6.3 PMUProgram .......................................... 19

6.4 Initiate Sleep Sequence Register (pmusleep) ......................... 20

6.5 WakeupSignalConditioning .................................. 21

6.6 PMU Interrupt Enables (pmuie) and Wakeup Cause (pmucause)............... 21

6.7 MemoryMap........................................... 22

7 E300 Power, Reset, Clock, Interrupt (PRCI) Control and Status Registers 23

7.1 PRCIAddressSpaceUsage .................................. 23

8 E300 Watchdog Timer (WDT) 25

8.1 Watchdog Count Register (wdogcount)............................. 25

8.2 WatchdogClockSelection.................................... 26

8.3 Watchdog Configuration Register wdogcfg ........................... 26

8.4 Watchdog Compare Register (wdogcmp) ............................ 27

8.5 Watchdog Key Register (wdogkey) ............................... 27

8.6 Watchdog Feed Address (wdogfeed).............................. 27

8.7 WatchdogConfiguration..................................... 27

8.8 WatchdogResets ........................................ 27

8.9 Watchdog Interrupts (wdogcmpip)................................ 28

9 E300 Real-Time Clock (RTC) 29

9.1 RTC Count Registers rtchi/rtclo ............................... 29

Copyright c

2016, SiFive Inc. All rights reserved. v

9.2 RTC Configuration Register rtccfg .............................. 29

9.3 RTC Compare Register rtccmp ................................. 30

10 E300 Backup Registers 31

11 General Purpose Input/Output Controller (GPIO) 33

11.1 MemoryMap........................................... 33

11.2 Input/OutputValues ...................................... 33

11.3 Interrupts ............................................. 33

11.4 InternalPull-Ups......................................... 35

11.5 DriveStrength .......................................... 35

11.6 OutputInversion ......................................... 35

11.7 HWI/OFunctions(IOF) ..................................... 35

11.8 BehaviorDuringSleepMode .................................. 36

12 Universal Asynchronous Receiver/Transmitter (UART) 37

12.1 UARTOverview ......................................... 37

12.2 MemoryMap........................................... 37

12.3 Transmit Data Register (txdata) ................................ 38

12.4 Receive Data Register (rxdata) ................................ 38

12.5 Transmit Control Register (txctrl)............................... 38

12.6 Receive Control Register (rxctrl)............................... 39

12.7 Interrupt Registers (ip and ie) ................................. 39

12.8 Baud Rate Divisor Register (div)................................ 39

13 Serial Peripheral Interface (SPI) 41

13.1 SPIOverview........................................... 41

13.2 MemoryMap........................................... 41

13.3 Serial Clock Divisor Register (sckdiv)............................. 41

13.4 Serial Clock Mode Register (sckmode)............................. 42

13.5 Chip Select ID Register (csid) ................................. 43

13.6 Chip Select Default Register (csdef).............................. 43

13.7 Chip Select Mode Register (csmode).............................. 43

13.8 Delay Control Registers (delay0 and delay1)......................... 44

13.9 Frame Format Register (fmt) .................................. 44

13.10 Transmit Data Register (txdata) ................................ 45

13.11 Receive Data Register (rxdata) ................................ 45

13.12 Transmit Watermark Register (txmark)............................. 46

vi SiFive E300 Platform Reference Manual, Version 1.0.1

13.13 Receive Watermark Register (rxmark)............................. 46

13.14 Interrupt Registers (ie and ip) ................................. 46

13.15 SPI Flash Interface Control Register (fctrl) ......................... 47

13.16 SPI Flash Instruction Format Register (ffmt) ......................... 47

14 One-Time Programmable Memory (OTP) Peripheral 49

14.1 MemoryMap........................................... 49

14.2 Programmed-I/O lock register (otp lock) ........................... 49

14.3 Programmed-I/O Sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

14.4 Read sequencer control register (otp rsctrl) ........................ 51

15 E300 Pulse-Width Modulation (PWM) Peripheral 53

15.1 PWMOverview.......................................... 53

15.2 PWMMemoryMap ....................................... 53

15.3 PWM Count Register (pwmcount)................................ 53

15.4 PWM Configuration Register (pwmcfg)............................. 54

15.5 PWM Compare Registers (pwmcmp0–pwmcmp3)......................... 55

15.6 Deglitch and Sticky circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

15.7 Generating Left- or Right-Aligned PWM Waveforms . . . . . . . . . . . . . . . . . . . . . 56

15.8 Generating Center-Aligned (Phase-Correct) PWM Waveforms . . . . . . . . . . . . . . . 57

15.9 Generating Arbitrary PWM Waveforms using Ganging . . . . . . . . . . . . . . . . . . . . 58

15.10 Generating One-shot Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

15.11 PWMInterrupts.......................................... 58

Chapter 1

Introduction

The E300 platform is the first member of SiFive’s Freedom Everywhere family of customizable

RISC-V SoCs. By combining a highly configurable base platform with customer-specific hardware

extensions, the Freedom Everywhere family provides low-NRE and rapid time-to-market solutions

for performance, cost, and power-sensitive embedded and IoT markets.

Each E300 SoC includes a SiFive E3 series RISC-V Coreplex with integrated instruction and data

memories, a platform-level interrupt controller, on-chip debug unit, and an extensive selection of

peripheral devices. This manual should be read together with the E3 Coreplex manual.

All aspects of the base E300 platform can be flexibly configured. In addition, the platform can be

readily extended with customer-specific instruction-set extensions, custom coprocessors, custom

accelerators, custom I/O, and custom always-on blocks. The resulting application-specific E300

SoC is optimized for manufacture in a TSMC 180nm process, and delivered as packaged tested

parts by SiFive.

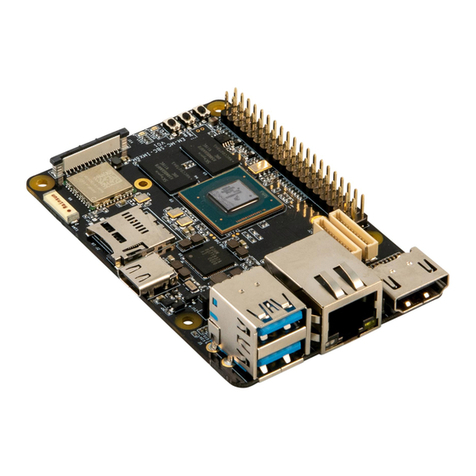

Block Diagram

Figure 1.1 shows the top-level block diagram of the E300 platform. The heart of the current

E300 platform is an E31 Coreplex, which contains an E31 RISC-V processor, instruction and data

memories, the platform-level interrupt controller (PLIC), a central DMA controller, and a debug

module.

Configurable E31 RISC-V Coreplex

The configurable E31 RISC-V Coreplex provides a high-performance single-issue in-order 32-bit

execution pipeline, with a peak sustained execution rate of one instruction per clock cycle. The

Freedom E300 platform supports most configuration options of the E31 core as described in the

E3 Coreplex manual, except for the following:

•Where present, the instruction cache line size is 32 bytes.

•The data cache is not supported.

The E3 Coreplex exports two TileLink attachments; a TileLink master port which can be used to

attach a custom accelerator, and a TileLink slave port to drive the platform bus. Both ports support

32-byte burst accesses over a 32-bit datapath.

1

2SiFive E300 Platform Reference Manual, Version 1.0.1

Freedom E300 Platform

Clock Generation

P-Bus: TileLink B32 D32

eFlash

E31 Coreplex

Platform-Level

Interrupt Control

TAPC

Debug Module

Debug SRAM

Instruction Fetch

RV32E/IMAFDCN

Branch Prediction

Integer Multiply/Divide

Inst. Decompressor

Memory Protection

Custom Instructions

Custom

Coprocessor

Instruction Buffer

M

MLoad/Store

dip

eip

lip

DMA

M

M

C-Bus

Instruction Cache

Instruction Fill/Prefetch M

Instruction SRAM

Mask ROM

Data SRAM

I-Bus

Quad SPI Flash

Custom Accelerator

M

M

Local Interrupts

Global Interrupts

EEPROM

Service

Requests

Always-On Block

Backup Registers

Real-Time Clock

Custom Always-On

Reset Unit

Watchdog Timer

GPIO Complex

PWM

Counter/Timer

UART

I2C

SPI

SRAM

OTP

FPU

Power Management

Figure 1.1: Top-Level Block Diagram of the E300 platform.

Custom Accelerators

Custom autonomous accelerators can be added to provide application-specific processing. The

custom accelerators can directly access on-chip memories and peripheral devices, and can gen-

erate and receive interrupts from the platform-level interrupt controller.

On-Chip Memory

The on-chip memory system can be flexibly configured to include ROM, OTP, eFLASH,

NVM/EEPROM, and/or SRAM of various sizes.

Execute-in-Place Quad-SPI Flash controller

A dedicated Quad-SPI flash controller can be added with support for a a memory-mapped burst-

read interface to support processor instruction cache or data cache refills from an external SPI

flash memory. Memory burst writes are not supported. The external SPI flash has a set of control

registers mapped into I/O space through which the external flash can be written under software

control.

Copyright c

2016, SiFive Inc. All rights reserved. 3

Peripheral Devices

Peripheral devices can be selected from a large catalog of standard components, including

counter/timers, watchdogs, PWM, GPIO, UART, I2C, SPI, ADC, DAC, SD/eMMC, USB 1.1/2.0

OTG, and 10/100/1000 Ethernet. The autonomous Coreplex DMA engine can be added to reduce

processor overhead in servicing I/O transfers to and from data memory. Third-party peripheral IP

can be attached via industry-standard SoC buses or TileLink. Please contact SiFive for details on

the available peripheral offerings, or on how to connect to existing IP.

Platform-Level Interrupt Controller

The configurable platform-level interrupt controller (PLIC) supports a large number of inputs and

programmable priority levels, and with the addition of the N extension can also support nested

interrupt handling for fast interrupt response.

Always-On Block and Power Management

E300 SoCs can be configured with active power management to reduce leakage current in sleep

mode. The Always-On Block (AON) supports low-power sleep with wakeup from an internal real-

time clock interrupt or external I/O stimulus, or custom always-on circuitry.

Debug Support

Each E300 system includes extensive platform-level debug facilities including hardware break-

points, watchpoints, and single-step execution accessed via an industry-standard JTAG interface

and supported by a full set of open-source debug tools. All components in the system, includ-

ing the processor, accelerators, memories, peripheral devices, and interrupt controller, can be

controlled and monitored over the debug port.

Software Tools

SiFive provides a full open-source RISC-V embedded software development toolchain for E300

SoCs, including modern C and C++ compilers with soft-floating-point support, standard libraries,

assemblers, linkers, and the FreeRTOS real-time operating system, together with debug tools to

drive the on-chip debug hardware.

4SiFive E300 Platform Reference Manual, Version 1.0.1

Chapter 2

E300 Platform Memory Map

The overall memory map of E300 is shown in Table 2.1.

Base Top Description

0x0000 0000 0x0FFF FFFF (see E3 Coreplex Manual) E3 Coreplex (256 MiB)

0x1000 0000 0x1000 7FFF Always-On (AON) (≤32 KiB)

Off-Coreplex I/O (1.75 GiB)

0x1000 8000 0x1000 FFFF Power, Reset, Clock, Interrupts (PRCI)

(≤32 KiB)

0x1001 0000 0x1001 0FFF On-chip OTP control

0x1001 1000 0x1001 1FFF On-chip eFlash control

0x1001 2000 0x1001 2FFF GPIO0

0x1001 3000 0x1001 3FFF UART0

0x1001 4000 0x1001 4FFF QSPI0

0x1001 5000 0x1FFF FFFF Additional Peripherals (<256MiB)

0x2000 0000 0x3FFF FFFF Off-chip QSPI0 flash read (512 MiB)

0x4000 0000 0x7FFF FFFF Additional I/O or RAM (1 GiB)

0x8000 0000 0x8001 FFFF Instruction and Data RAM (≤128 KiB) Memory (2 GiB)

0x8002 0000 0xFFFF FFFF Additional RAM

Table 2.1: E300 Physical Memory Map.

5

6SiFive E300 Platform Reference Manual, Version 1.0.1

Chapter 3

E300 Power Modes

This chapter describes the different power modes available on E300 systems. E300 systems

currently support three power modes: Run, Wait, and Sleep.

Run Mode

Run mode corresponds to regular execution where the processor is running. Power consumption

can be adjusted by varying the clock frequency of the processor and peripheral bus, and by en-

abling or disabling individual peripheral blocks. The processor exits run mode by executing a “Wait

for Interrupt” (WFI) instruction.

Wait Mode

When the processor executes a WFI instruction it enters Wait mode, which halts instruction exe-

cution and gates the clocks driving the processor pipeline. All state is preserved in the system.

The processor will resume in Run mode when there is a local interrupt pending or when the PLIC

sends an interrupt notification. The processor may also exit wait mode for other events, and soft-

ware must check system status when exiting wait mode to determine the correct course of action.

Sleep Mode

Sleep mode is entered by writing to a memory-mapped register pmusleep in the power-

management unit (PMU). The pmusleep register is protected by the pmukey register which must

be written with a defined value before writing to pmusleep.

The PMU will then execute a power-down sequence to turn off power to the processor and main

pads. All volatile state in the system is lost except for state held in the AON domain. The main

output pads will be left floating.

Sleep mode is exited when an enabled wakeup event occurs, whereupon the PMU will initiate

a wakeup sequence. The wakeup sequence turns on the core and pad power supplies while

asserting reset on the clocks, core and pads. After the power supplies stabilize, the clock reset

is deasserted to allow the clocks to stabilize. Once the clocks are stable, the pad and processor

resets are deasserted, and the processor begins running from the reset vector.

Software must reinitialize the core and can interrogate the PMU pmucause register to determine

the cause of reset, and can recover pre-sleep state from the backup registers. The processor

7

8SiFive E300 Platform Reference Manual, Version 1.0.1

always initially runs from the HFROSC at the default setting, and must reconfigure clocks to run

from an alternate clock source (HFXOSC or PLL) or at a different setting on the HFROSC.

Chapter 4

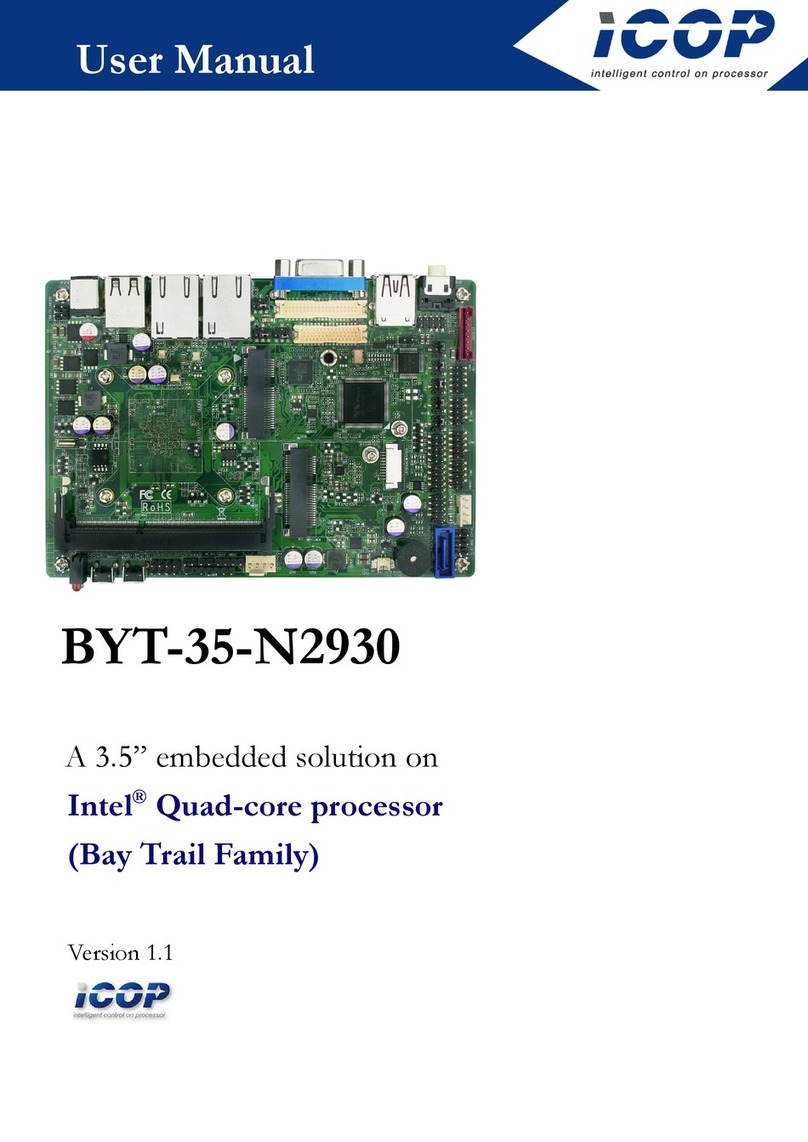

E300 Clock Generation

The Freedom E300 platform supports many alternative clock-generation schemes to match appli-

cation needs. This chapter describes the basic structure of E300 clock generation. The various

clock configuration registers live either in the AON block (Chapter 5) or the PRCI block (Chapter 7).

Clock Generation Overview

Optional PLL

Optional HF crystal oscillator

Optional LF RC oscillator

Optional LF crystal oscillator

Optional peripherals

Always-On Domain

pllref pllout

6-48MHz 50-400MHz

PLL

JTAG tck ≤16MHz

hfroscout

1.125-72MHz

lfxoscin

lfxoscout

32.768kHz

hfxoscin

hfxoscout

16MHz

LFRCOSC

lfrcoscout

30-60kHz

pllcfg

jtagclk

÷N

plloutdiv

coreclk

÷N

spiclkcfg

spiclk

8/16*baud rate

÷N

uartclkcfg

uartclk

25MHz/125MHz

÷N

enetclkcfg

enetclk

÷N

usbclkcfg

usbclk

60MHz

hfclk

÷N

hyperclkcfg

hyperclk

≤166MHz

÷N

i2sclkcfg

i2sclk

1.536MHz/1.4112MHz

pllrefsel

1

0

jtagclk is selected when

psdscanen is asserted

HFROSC

hfrosccfg

÷N

pllsel

0

1

Real-Time Clock/Alarm

Watchdog Timer

psdclkbypass_n

1

0

LFROSC

lfrosccfg

÷N

÷4

psdhfclkout

psdlfclkout

{

Only one

on-chip

LFxOSC in

system

tlclk

Process

Monitor ÷N

procmoncfg

3

0

psdlfaltclk

psdlfclksel

1

0

1

2

hfxosccfg

psdscanen_n psdscanen

0.4-400MHz

Figure 4.1: E300 clock generation scheme.

9

10 SiFive E300 Platform Reference Manual, Version 1.0.1

Figure 4.1 shows an overview of the E300 clock generation scheme. Most digital clocks on the

chip are divided down from a central high-frequency clock hfclk produced from either the PLL or

an on-chip trimmable oscillator. The PLL can be driven from either the on-chip oscillator or an off-

chip crystal oscillator. In systems without a PLL, the off-chip oscillator can drive the high-frequency

clock directly.

For the FE310-G000, the TileLink bus clock (tlclk) is fixed to be the same as the processor core

clock (coreclk). As shown, each peripheral may also generate local divided clocks from tlclk.

The Always-On block includes a real-time clock circuit that is driven from one of three possible

low-frequency clock sources: an off-chip 32 kHz crystal oscillator, an on-chip low-frequency RC

oscillator, or a clock divided down from hfclk.

Test mode can select the JTAG test clk (TCK) to be driven into all clock trees to support scan.

Internal Trimmable Programmable 72 MHz Oscillator (HFROSC)

An internal trimmable high-frequency ring oscillator (HFROSC) is used to provide the default clock

after reset, and can be used to allow operation without an external high-frequency crystal or a

PLL.

The oscillator is controlled by the hfrosccfg register, which is memory-mapped in the PRCI ad-

dress space, and whose format is shown in Figure 4.1.

31 30 29 21 20 16 15 6 5 0

hfroscrdy hfroscen 0 hfrosctrim 0 hfroscdiv

1 1 9 5 10 6

Table 4.1: The HFROSC config register, hfrosccfg.

The frequency can be adjusted in software using a 5-bit trim value in the hfrosctrim. The trim

value (from 0–31) adjusts which tap of the variable delay chain is fed back to the start of the ring. A

value of 0 corresponds to the longest chain and slowest frequency, while higher values correspond

to shorter chains and therefore higher frequencies.

The HFROSC oscillator output frequency can be divided by an integer between 1 and 64 giving

a frequency range of 1.125 MHz–72 MHz assuming the trim value is set to give a 72 MHz output.

The value of the divider is given in the hfroscdiv field, where the divide ratio is one greater than

the binary value held in the field (i.e., hfroscdiv=0 indicates divide by 1, hfroscdiv=1 indicates

divide by 2, etc.). The value of the divider can be changed at any time.

The HFROSC is the default clock source used for the system core at reset. After a reset, the

hfrosctrim value is reset to 16, the middle of the adjustable range, and the divider is reset to ÷5

(hfroscdiv=4), which gives a nominal 13.8 MHz (±50%) output frequency.

The value of hfrosctrim that most closely achieves an 72 MHz clock output at nominal conditions

(1.8 V at 25 C) is determined by manufacturing-time calibration and is stored in on-chip OTP stor-

age. Upon reset, software in the processor boot sequence can write the calibrated value into the

hfrosctrim field, but the value can be altered at any time during operation including when the

processor is running from HFROSC.

Copyright c

2016, SiFive Inc. All rights reserved. 11

To save power, the HFROSC can be disabled by clearing hfroscen. The processor must be

running from a different clock source (the PLL, external crystal, or external clock) before disabling

HFROSC. HFROSC can be explicitly renabled by setting hfroscen. HFROSC will be automatically

re-enabled at every reset.

The status bit hfroscrdy indicates if the oscillator is operational and ready for use as a clock

source.

External 16 MHz Crystal Oscillator (HFXOSC)

An external high-frequency 16 MHz crystal oscillator can be used to provide a precise clock source.

The crystal oscillator should have a capacitive load of ≤12 pF and an ESR ≤80 Ω.

When used to drive the PLL, the 16 MHz crystal oscillator output frequency must be divided by two

in the first-stage divider of the PLL (i.e., R= 2) to provide an 8 MHz reference clock to the VCO.

The input pad of the HFXOSC can also be used to supply an external clock source, in which case,

the output pad should be left unconnected.

The HFXOSC input can be used to generate hfclk directly if there is no PLL present in the system,

or if the PLL is set to bypass.

The HFXOSC is controlled via the memory-mapped hfxosccfg register.

31 30 29 0

hfxoscrdy hfxoscen 0

1 1 30

Table 4.2: The HFXOSC config register, hfxoscccfg.

The hfxoscen bit turns on the crystal driver and is set after wakeup reset, but can be cleared to

turn off the crystal driver and reduce power consumption. The hfxoscrdy bit indicates if the crystal

oscillator output is ready for use.

The hfxoscen bit must also be turned on to use the HFXOSC input pad to connect an external

clock source.

Internal High-Frequency PLL (HFPLL)

The PLL generates a high-frequency clock by multiplying a mid-frequency reference source clock,

either the HFROSC or the HFXOSC. The input frequency to the PLL can be in the range 6–48 MHz.

The PLL can generate output clock frequencies in the range 48–384 MHz.

The PLL is controlled by a memory-mapped read-write pllcfg register in the PRCI address space.

The format of pllcfg is shown in Figure 4.3.

Figure 4.2 shows how the PLL output frequency is set using a combination of three read-write

fields: pllr[2:0],pllf[2:0],pllq[1:0]. The frequency constraints must be observed between

each stage for correct operation.

The pllr[1:0] field encodes the reference clock divide ratio as a 2-bit binary value, where the

value is one less than the divide ratio (i.e., 00=1, 11=4). The frequency of the output of the

12 SiFive E300 Platform Reference Manual, Version 1.0.1

31 30 19 18 17 16 15 12 11 10 9 4 3 2 0

plllock 0pllbypass pllrefsel pllsel 0pllq pllf 0pllr

1 12 1 1 1 4 2 6 1 3

Table 4.3: The PLL config register, pllcfg.

÷R

pllr[1:0]

=1,2,3,4

×F

pllf[5:0]

=2,4,..,128

÷Q

pllq[1:0]

=2,4,8

pllref refr vco pllout

6-48MHz 6-12MHz 384-768MHz 48-384MHz

Figure 4.2: Controlling the E300 PLL output frequency.

reference divider (refr) must lie between 6–12 MHz.

The pllf[5:0] field encodes the PLL VCO multiply ratio as a 6-bit binary value, N, signifying a

divide ratio of 2×(N+ 1) (i.e., 000000=2, 111111=128). The frequency of the VCO output (vco)

must lie between 384–768 MHz. Table 4.4 summarizes the valid settings of the multiply ratio.

Legal vco

pllf frequency

refr multiplier (MHz)

(MHz) Min Max Min Max

6 64 128 384 768

8 48 96 384 768

10 39 76 390 760

12 32 64 384 768

Table 4.4: Valid PLL multiply ratios. The multiplier setting in the table is given as the actual multiply

ratio; the binary value stored in pllf field should be (M/2) −1for a multiply ratio M.

The pllq[1:0] field encodes the PLL output divide ratio as follow, 01=2, 10=4, 11=8. The value 00

is not supported. The final output of the PLL must have a frequency that lies between 48–384 MHz.

The one-bit read-write pllbypass field in the pllcfg register turns off the PLL when written with a

1 and then pllout is driven directly by the clock indicated by pllrefsel. The other PLL registers

can be configured when pllbypass is set. The agent that writes pllcfg should be running from a

different clock source before disabling the PLL. The PLL is also disabled with pllbypass=1 after a

wakeup reset.

The pllsel bit must be set to drive the final hfclk with the PLL output, bypassed or otherwise.

Table of contents